DSP中Audio专业名称解释

ADC信噪比(Signal-to-Noise Ratio SNR)

模数转换中,输出的有效功率与噪声功率的比值,值越大表示转换后声音信号越清晰,其值的计算公式如下:

S N R = 10 ∗ l g P s i g n a l P n o i s e SNR = 10*lg\frac{P_{signal}}{P_{noise}} SNR=10∗lgPnoisePsignal

差分输入

在ADC转换中接收两个信号,一个正相输入(IN+)和一个反向输入(IN-),通过正反两路信号,可以抵消共模噪声,提高信号的清晰度,其原理如下:

正相输入信号: V + V_+ V+来源于信号源,如麦、传感器和传输线传来的信号,包含了有效信号和噪声信号, V s i g n a l + V n o i s e V_{signal}+V_{noise} Vsignal+Vnoise

反相输入信号: V − V_- V−经过硬件电路(反相放大器),将正相输入信号进行180度翻转得到,即 − ( V s i g n a l + V n o i s e ) ) -(V_{signal}+V_{noise})) −(Vsignal+Vnoise))

以上两路信号在经过差分放大器时会做一个差值:

V + − V − = V s i g n a l + V n o i s e − ( − ( V s i g n a l + V n o i s e ) ) = 2 V s i g n a l V_+ - V_- = V_{signal}+V_{noise} - (-(V_{signal}+V_{noise}))=2V_{signal} V+−V−=Vsignal+Vnoise−(−(Vsignal+Vnoise))=2Vsignal

上面差分放大器对共模噪声 V n o i s e V_{noise} Vnoise不敏感,所以不会变成2倍 V n o i s e V_{noise} Vnoise,而是被抵消掉,但是实际情况下,差分放大器不是完美的,会对噪声有一定的响应,不能完全抵消

伪差分输入 (Pseudo Differential Input)

伪差分输入则是一种简化版的差分输入。它通常包含一个真正的差分输入端口和一个参考地电平。在这种配置下,一个输入端口接收信号,而另一个端口接地或参考地电平,而不是提供一个真正反相的信号。这种方式可以模拟出差分输入的效果,但在噪声抑制能力上可能不如真正的差分输入强。

模拟DRC(Dynamic Range Control)

它是一种硬件电路,自动调整音频信号的动态范围,以防止过载和减少失真,DRC通常通过压缩或限制信号电平来实现这一目标,他们都是控制电路来减少信号增益:

压缩:

DRC通常通过压缩或限制信号电平来实现这一目标当输入信号的电平超过设定的阈值时,压缩电路开始介入,逐渐减少增益,这个增益可以理解为对输入信号的音量/能量控制。增益的减少是渐进的,这意味着信号的提升量小于信号的输入量,但并不完全阻止信号的通过。

限制:

限制是压缩的一种特殊形式,它在信号电平达到某个固定阈值时,立即大幅度减少增益,几乎停止信号的进一步提升。限制器的目标是作为一个“硬限幅”,确保信号不会超过安全的电平,从而防止过载和削波。

扩张:

当电平信号小于某个阈值,DRC会增大增益,提高信号清晰度

高通滤波器HPF

软件或硬件实现,通过设置一个截止频率,输入信号经过高通滤波器时,会把低于截止频率的信号去除,而保留高于截止频率的信号;高通滤波器应用很广泛,可以用在音频、视频、通信等,在音频领域中可用于噪声去除、音调增强:

噪声去除

音频信号中的噪声,其中一些可能是低频的,比如环境噪音、机械振动或者电力线路的50/60Hz噪声,设置对应的截止频率即可去除掉噪声信号音调增强

在某些情况下,音频信号可能过于平坦或不清晰,特别是一些低质量的录音,但是人声、录音中通常富含高配信号;

采样率转换器SRC:

- 2ch x4

- FSI = 8kHz to 192kHz, FSO = 8kHz to 192kHz (FSO/FSI = 0.167 to 6.0)

采样率转换器,支持2通道,FSI和FSO是输入和输出采样率范围,他们转换的比值要再FSO/FSI内

FSCONV

单通道采样率转换器

数字音频接口(Digital Input/Output Interface)

传输数字信号的音频接口,通常可以用在DSP和Codec芯片、DSP和Memeory或者其它Soc与DSP之间传输音频数据的接口,接口类型通常有I2S、TDM、PDM和S/PDIF等:

I2S

I2S(Inter-IC Sound):集成电路内置音频总线,采用了沿独立的导线传输时钟与数据信号的设计,通过将数据和时钟信号分离,避免了因时差诱发的失真,为用户节省了购买抵抗音频抖动的专业设备的费用。

I2S有3条线:

- 串行时钟SCK或BLCK,每一个bit位的音频数据,对应一个SCK的始终脉冲,即SCK的频率等于 C h a n n e l C o u n t s ∗ S a m p l e R a t e ∗ f o r m a t ChannelCounts * SampleRate * format ChannelCounts∗SampleRate∗format

- 字段选择信号WS,也叫LRCLK,用于切换左右声道数据,其频率等于采样频率 S a m p l e R a t e SampleRate SampleRate;

| WS | 描述 |

|---|---|

| 0 | 传输左通道数据 |

| 1 | 传输右通道数据 |

- 串行数据SD,以二进制补码表示音频数据

- 通常与Cocdec连接时,还要求控制器提供MCLK,CODEC内部基于Delta-Sigma (ΔΣ)的架构设计要求使然。其主要原因是因为这类的CODEC没有所谓提供芯片的工作时钟晶振电路,它需要外部的时钟提供内部PLL;

在I2S总线上,I2S传输的是PCM编码后的音频数据,只能同时存在一个主设备和发送设备。主设备可以是发送设备,也可以是接收设备,或是协调发送设备和接收设备的其它控制设备。在I2S系统中,提供时钟(BCLK和LRCLK)的设备为主设备。

PCM

PCM数字接口原理,以一种固定频率对模拟信号进行采样、量化和编码,转换位数字信号PCM格式数据,I2S可以传输2通道的数据,而PCM接口利用TDM(时分复用技术,通过控制时间片,将多路信号交叉传输)可以传输多通道的音频数据;PCM右4条线如下:

(FS)PCM_SYNC,PCM同步信号,其频率等于采样率

(DX_IN)PCM_IN,PCM数据信号输入;

(DX_OUT)PCM_OUT,PCM数据信号输出;

(BCLK)PCM_CLK,PCM时钟信号;

最简单的音频接口是PCM(脉冲编码调制)接口,该接口由时钟脉 冲(BCLK)、帧同步信号(FS)及接收数据(DR)和发送数据(DX)组成。在FS信号的上升沿,数据传输从MSB(Most Significant Bit)字开始,FS频率等于采样率。

PCM接口的应用场景可以在AP处理器与通信Modem之间,可以支持蓝牙通话、传输语音等;但蓝牙音乐走的则是串口;

PCM收发过程

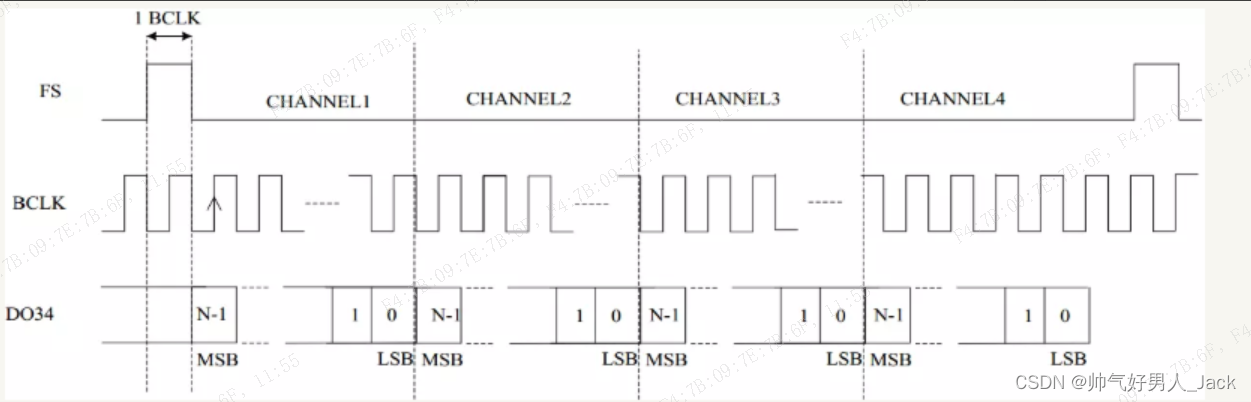

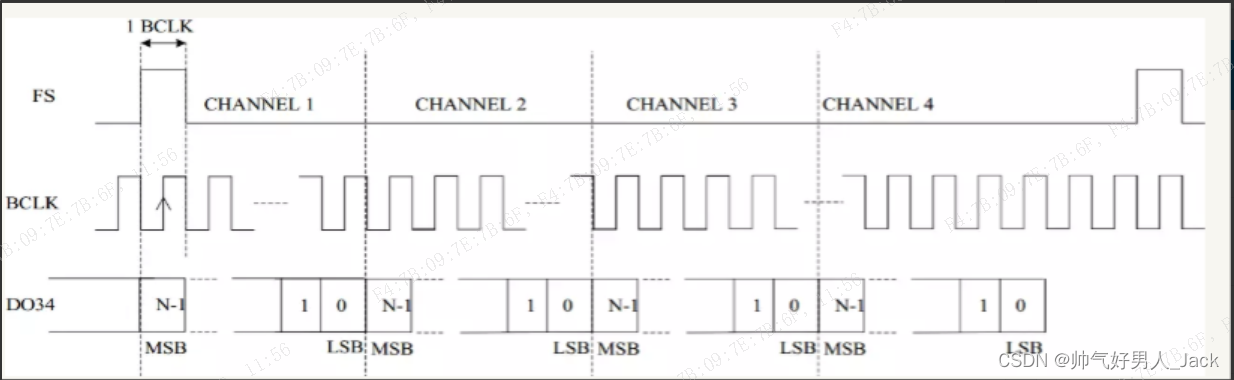

PCM接口分为两种常用操作模式:DSP A mode和DSP B mode,统称为DSP mode。

基于DSP mode,PCM接口可以配置支持TDM(Time Division Multiplexing)数据传输。可以支持传输多个声道的数据,允许多个设备同时使用总线。由于没有统一的标准,不同厂商在TDM 实现的时序上略有差异。

DSP A: FSYNC有效后,数据在BCLK的第2个上升沿(下降沿)有效(one bit clock delay)

DSP B: FSYNC有效后,数据在BCLK的第1个上升沿(下降沿)有效(no delay)

PDM

PDM接口只有两根信号线:

PDM_CLK 时钟信号。

PDM_DATA 数据信号。

PDM接口多用于传输麦克风录音,传输内容为PDM编码后的数据,在数字麦克风领域,应用最广的就是PDM接口,其次为I2S接口。PDM在诸如手机和平板等对于空间限制严格的场合有着广泛的应用前景。

TDM时分复用技术

同一条物理传输通道上,在时间上分割出多个信道来传输多通道的数据

SDR

数字混音电路(Digital Mixer Circuit)

数字混音电路(Digital Mixer Circuit)是指在数字域中混合多个音频信号的电路或系统。

PLL Circuit锁相环(Phase-Locked Loop)电路

这是一种反馈控制系统,用于生成稳定的频率输出,其频率锁定于参考信号的频率。PLL电路广泛应用于各种电子设备中,如无线电接收器、频率合成器、时钟发生器、数据传输系统等。在音频设备中,PLL电路可以用于稳定采样时钟,确保数字音频信号的准确无误处理,避免时钟抖动和相位噪声的影响。

μP Interface: SPI(7MHz max), I2C-bus (1MHz, Fast Mode Plus)

μP(microprocessor)接口指的是微处理器(或微控制器)与外部设备通信的接口。

- SPI (Serial Peripheral Interface):SPI是一种同步串行接口,用于快速数据传输。它是一种全双工(同时发送和接收)接口,通常由主设备控制时钟和数据传输。在提到的规格中,SPI接口的最大时钟频率为7MHz,这意味着数据传输速度可达7Mbps。

- I2C-bus (Inter-Integrated Circuit bus):I2C是一种两线式串行总线标准,用于连接低速的微芯片,如传感器、EEPROM、A/D转换器、D/A转换器、I/O扩展器等。I2C使用串行数据线(SDA)和串行时钟线(SCL)进行通信。Fast Mode Plus 是 I2C 的一种模式,允许更高的时钟频率,这里提到的1MHz意味着数据传输速度可达1Mbps。

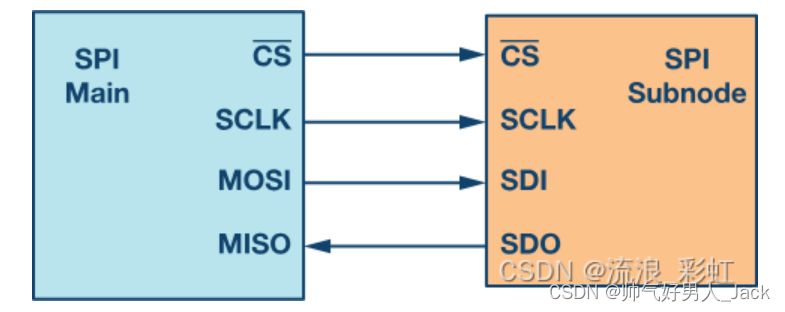

SPI接口

串行外设接口(SPI)是微控制器(MCU)与外设IC(ADC、传感器)之间的数据传输接口,支持全双工,SPI支持一个主对应多个从设备,SPI可以是三线或四线,如下:

- 时钟SCLK:时钟信号

- CS片选,低电平有效,低电平时可以进行主从设备收发

- MOSI:主输出,从输入

- MOSO:主输入,从输出

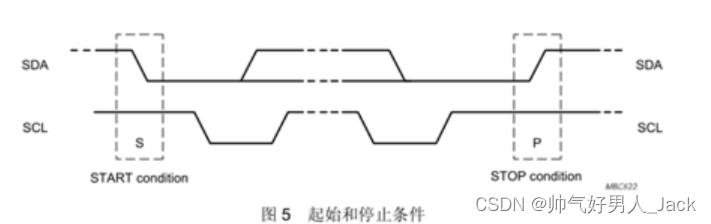

I2C接口

简单的双向总线,只有两根线分别是串行数据线(SDA),串行时钟线(SCL)。总线中可以存在一个主机多个从机的模式,

传输规则

起始条件:当SCL为高电平时,SDA从高电平向低电平切换。

停止信号:当SCL为高电平时,SDA从低电平向高电平切换

零交叉检测

用于处理音频信号,音频信号可以理解成一个正弦波,信号由正-0-负或负-0-正这一现象,叫做零交叉,音频DSP芯片中有专门检测这一信号状态,当改变增益或其它参数时,不做检测,会造成音频信号突变,从而产生哒哒声或突变噪声,例如:

y ( t ) = A 1 ∗ s i n ( 2 ∗ P I ∗ f ∗ t ) y(t) = A_1*sin(2*PI*f*t) y(t)=A1∗sin(2∗PI∗f∗t)

假设t=0.25时, y ( 0.25 ) = 0 y(0.25)=0 y(0.25)=0,这个时候音量增益A_1变为A_2,此时 y ( 0.25 ) y(0.25) y(0.25)仍然是0,不会引入突变;但是当t在其它情况时, y ( t ) ! = 0 y(t)!=0 y(t)!=0时,去改变增益A_1为其他值,最后 y ( t ) y(t) y(t)就会突变,引入噪声