1. LED流水灯的FPGA代码

在这个任务中,首先我们会使用状态机的思想来设计一个LED流水灯的控制逻辑。LED流水灯一般需要依次点亮不同的LED,并且循环播放。我们将其分为几个状态,每个状态控制一个或一组LED灯。

状态机设计

假设我们有8个LED(从LED0到LED7),流水灯的效果是依次点亮每一个LED,最终循环回第一个LED。

状态机的实现步骤

- 设计一个3位的状态寄存器,用于表示当前LED的状态(点亮的LED)。

- 在每个时钟周期,更新状态寄存器,控制下一个LED点亮。

- 当状态寄存器达到最后一个LED时,重新回到第一个LED。

Verilog 代码实现:

module led_fsm(

input clk, // 时钟信号

input rst_n, // 复位信号,低电平有效

output reg [7:0] led // 8个LED的输出

);

// 定义状态

reg [2:0] state; // 3位状态寄存器,用于表示当前的LED

reg [2:0] next_state; // 下一个状态

// 状态定义

parameter S0 = 3'b000, // LED0

S1 = 3'b001, // LED1

S2 = 3'b010, // LED2

S3 = 3'b011, // LED3

S4 = 3'b100, // LED4

S5 = 3'b101, // LED5

S6 = 3'b110, // LED6

S7 = 3'b111; // LED7

// 状态机逻辑:根据当前状态和时钟,决定下一个状态

always @ (posedge clk or negedge rst_n) begin

if (~rst_n)

state <= S0; // 复位时回到初始状态

else

state <= next_state;

end

// 下一个状态逻辑

always @ (state) begin

case(state)

S0: next_state = S1;

S1: next_state = S2;

S2: next_state = S3;

S3: next_state = S4;

S4: next_state = S5;

S5: next_state = S6;

S6: next_state = S7;

S7: next_state = S0;

default: next_state = S0; // 默认状态

endcase

end

// 根据当前状态控制LED的输出

always @ (state) begin

case(state)

S0: led = 8'b00000001;

S1: led = 8'b00000010;

S2: led = 8'b00000100;

S3: led = 8'b00001000;

S4: led = 8'b00010000;

S5: led = 8'b00100000;

S6: led = 8'b01000000;

S7: led = 8'b10000000;

default: led = 8'b00000001; // 默认状态

endcase

end

endmodule

测试代码:

接下来编写一个简单的测试平台,用于仿真测试这个LED流水灯的设计。

module tb_led_fsm;

reg clk;

reg rst_n;

wire [7:0] led;

// 实例化待测试模块

led_fsm uut (

.clk(clk),

.rst_n(rst_n),

.led(led)

);

// 时钟生成

always begin

#5 clk = ~clk; // 10ns周期的时钟

end

// 初始化信号

initial begin

clk = 0;

rst_n = 0;

#10 rst_n = 1; // 10ns后解除复位

#100; // 等待足够的时间以观察流水灯效果

$stop; // 停止仿真

end

// 监视LED的变化

initial begin

$monitor("At time %t, LED = %b", $time, led);

end

endmodule

仿真分析:

- 使用ModelSim打开工程。

- 编译Verilog代码。

- 运行仿真,查看led的变化。

DE2-115板验证:

- 将上述Verilog代码加载到DE2-115 FPGA开发板中。

- 使用Qsys或SystemVerilog工具进行配置。

- 编写一个简单的约束文件,确保LED和时钟信号正确连接。

- 使用Quartus II编译和烧录程序到FPGA开发板,观察LED的流水灯效果。

2. CPLD与FPGA的主要技术区别

CPLD(复杂可编程逻辑器件)和FPGA(现场可编程门阵列)的主要区别:

架构:

- CPLD通常具有较少的逻辑资源,采用宏单元(宏块)结构。

- FPGA具有更多的逻辑单元,采用可编程逻辑阵列结构,适用于更复杂的应用。

容量:

- CPLD的逻辑资源较少,适合简单的逻辑控制任务。

- FPGA具有更大的逻辑资源和更高的逻辑密度,适合复杂的并行处理和高性能任务。

功耗:

- CPLD功耗较低,适合低功耗应用。

- FPGA相对功耗较高,尤其是高密度FPGA。

速度:

- CPLD的时钟频率较低,适合较慢的应用。

- FPGA可以支持更高的时钟频率,适用于高速处理任务。

配置方式:

- CPLD配置速度较快,通常不需要外部配置存储。

- FPGA通常需要外部配置存储,配置速度较慢。

适用场合:

- CPLD:适用于简单的逻辑控制、时序电路、状态机等低密度任务。

- FPGA:适用于高速计算、数字信号处理(DSP)、视频处理、通信等需要大量并行计算的复杂应用。

3. hdlbits FPGA教程在线学习

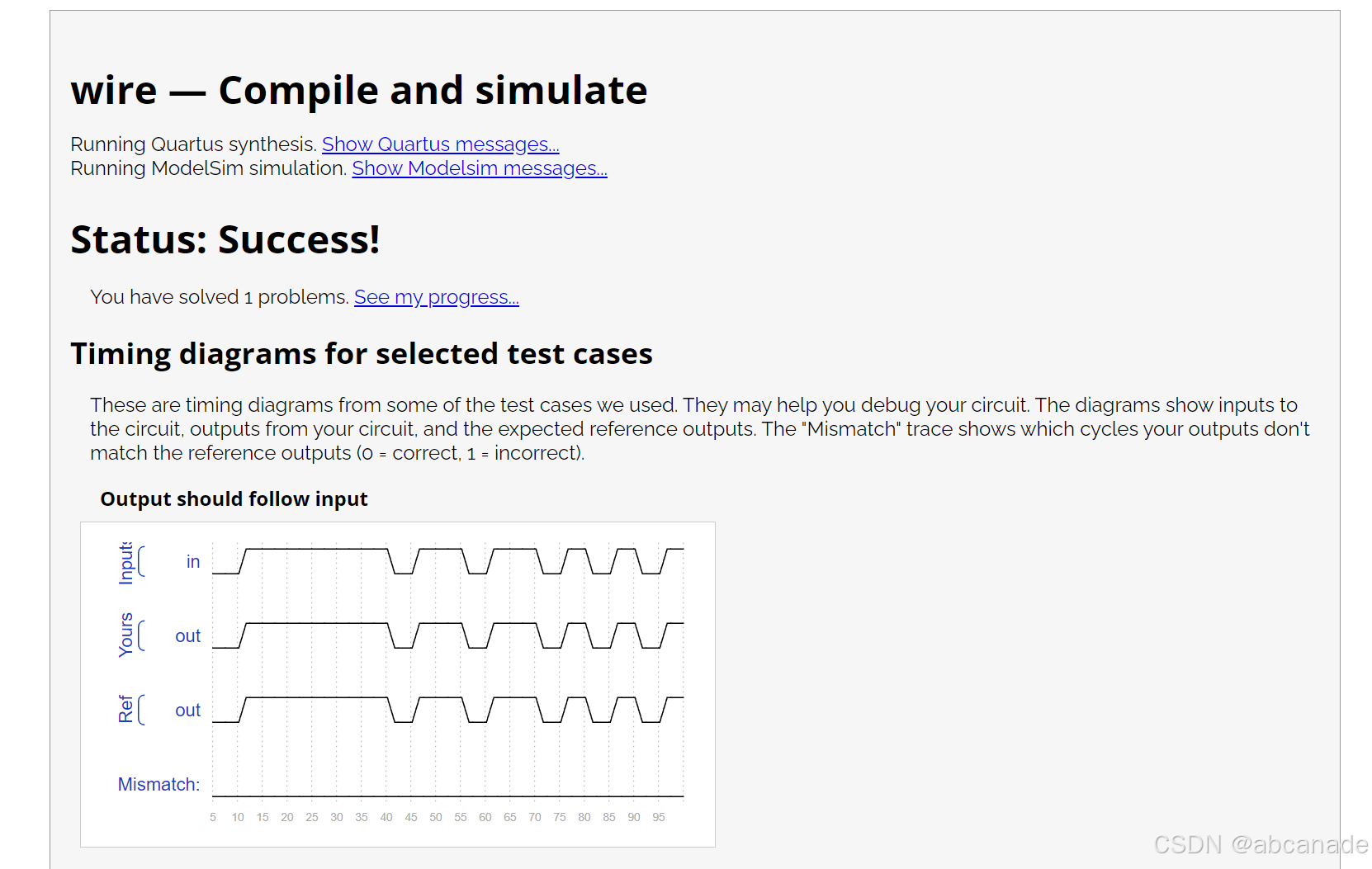

1.Wire

创建一个具有一个输入和一个输出的模块,其行为类似于电线。

与物理导线不同,Verilog 中的导线(和其他信号)是定向的。这意味着信息只在一个方向上流动,从(通常是一个)源到接收器(该源通常也称为将值驱动到导线上的驱动程序)。在Verilog"连续赋值"(assign left_side = right_side;)中,右侧信号的值被驱动到左侧的导线上。分配是"连续的",因为即使右侧的值发生变化,分配也会一直继续。连续分配不是一次性事件。assign left_side = right_side;

模块上的端口也有一个方向(通常是输入或输出)。输入端口由模块外部的东西驱动,而输出端口则驱动外部的东西。从模块内部查看时,输入端口是驱动器或源,而输出端口是接收器。

下图说明了电路的每个部分如何对应于Verilog代码的每个位。模块和端口声明创建电路的黑色部分。您的任务是通过添加要连接到 的语句来创建一条线路(绿色)。开箱即用的部件不是您关心的问题,但您应该知道,通过将测试线束的信号连接到顶部_模块的端口,可以测试您的电路。

module top_module( input in, output out );

assign out = in;

endmodule

2 Four wires

创建一个具有 3 个输入和 4 个输出的模块,其行为类似于建立这些连接的电线:

a -> w

b -> x

b -> y

c -> z

下图说明了电路的每个部分如何对应于Verilog代码的每个位。从模块外部,有三个输入端口和四个输出端口。当您有多个赋值语句时,它们在代码中的显示顺序无关紧要。与编程语言不同,赋值语句(“连续赋值”)描述事物之间的连接,而不是将值从一个事物复制到另一个事物的操作。现在也许应该澄清的一个潜在的混淆来源是:这里的绿色箭头代表电线之间的连接,但本身不是电线。模块本身已经声明了 7 条导线(命名为 a、b、c、w、x、y 和 z)。这是因为,除非另有说明,否则声明实际上声明了一条线。写 input wire a 写 input a 是一样的.。因此,这些语句不是在创建导线,而是在已经存在的 7 根导线之间创建连接。

module top_module(

input a,b,c,

output w,x,y,z );

assign w = a;

assign x = b,y = b;

assign z = c;

endmodule

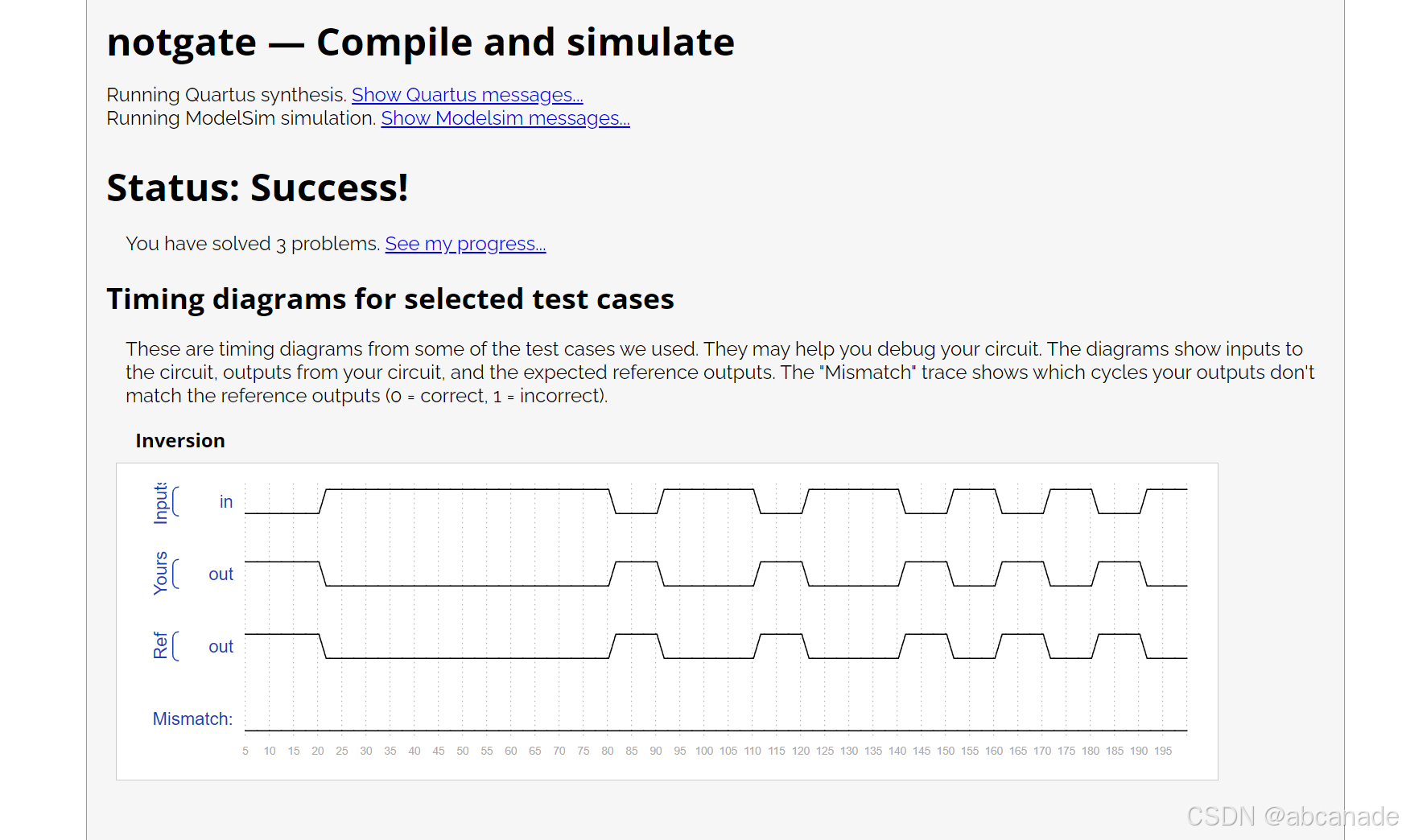

3 Inverter

创建一个实现 NOT 门的模块。该电路类似于线,但略有不同。当从电线连接到电线时,我们将实现逆变器(或"非门")而不是普通电线。使用assign语句。assign语句将持续将in的非转换为out。

module top_module( input in, output out );

assign out = ~in;

endmodule

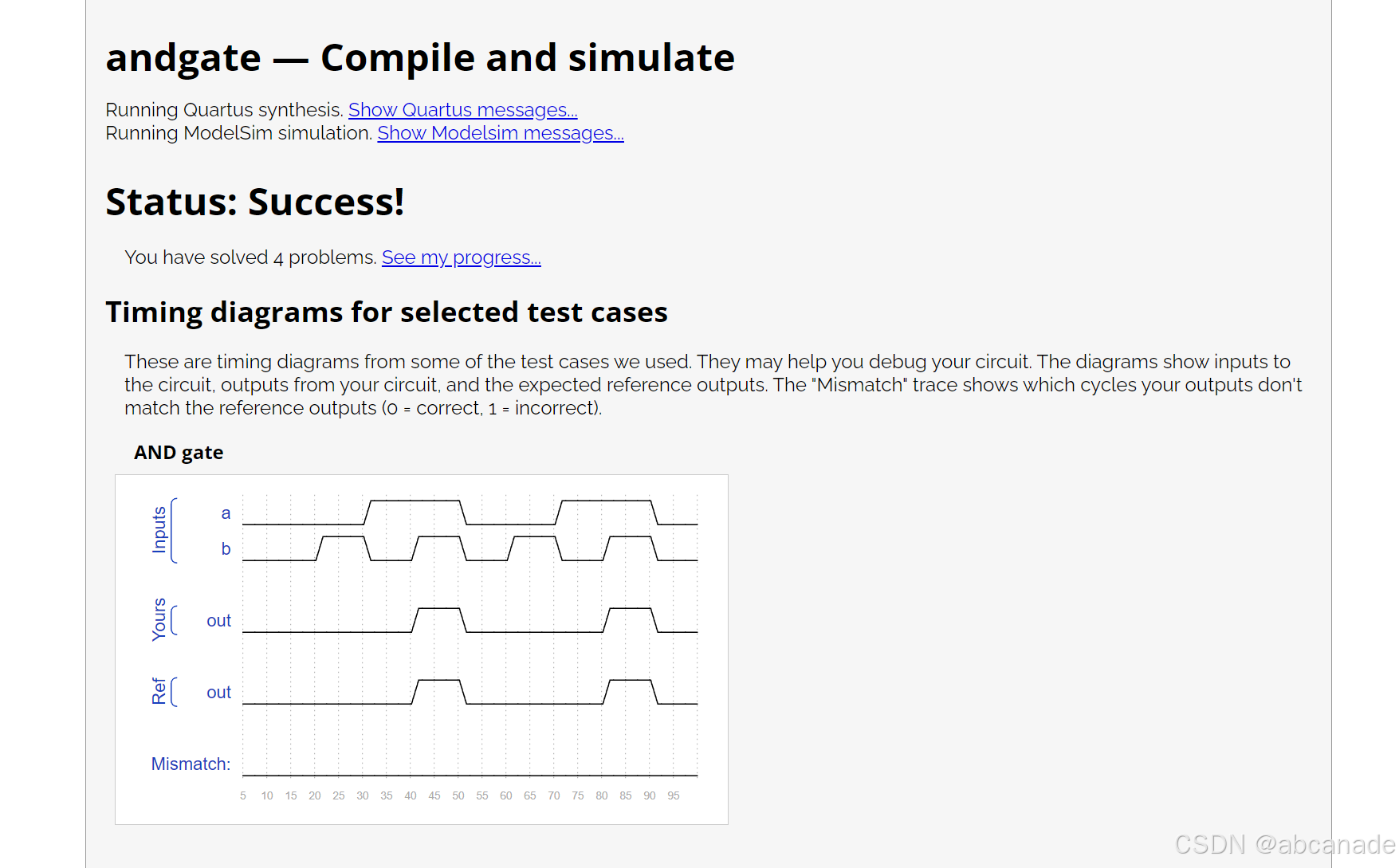

4 AND gate

创建实现 AND 门的模块。

该电路现在有三条导线(a、b和out)。导线a和b已经具有由输入端口驱动的值。但wire out目前并不是由任何因素驱动的。写一个assign语句,用a和b的AND信号输出。

请注意,该电路与NOT门非常相似,只是多了一个输入。如果听起来不一样,那是因为我已经开始描述信号是被驱动的(已知值由附加到它的某个东西决定)还是不是被某个东西驱动的。输入线由模块外部的东西驱动。assign语句将把一个逻辑电平驱动到一条线上。正如您所料,一条导线不能有多个驱动器(如果有,其逻辑级别是多少?),没有驱动程序的导线将有一个未定义的值(在合成硬件时通常被视为0)。

module top_module(

input a,

input b,

output out );

assign out = a & b;

endmodule

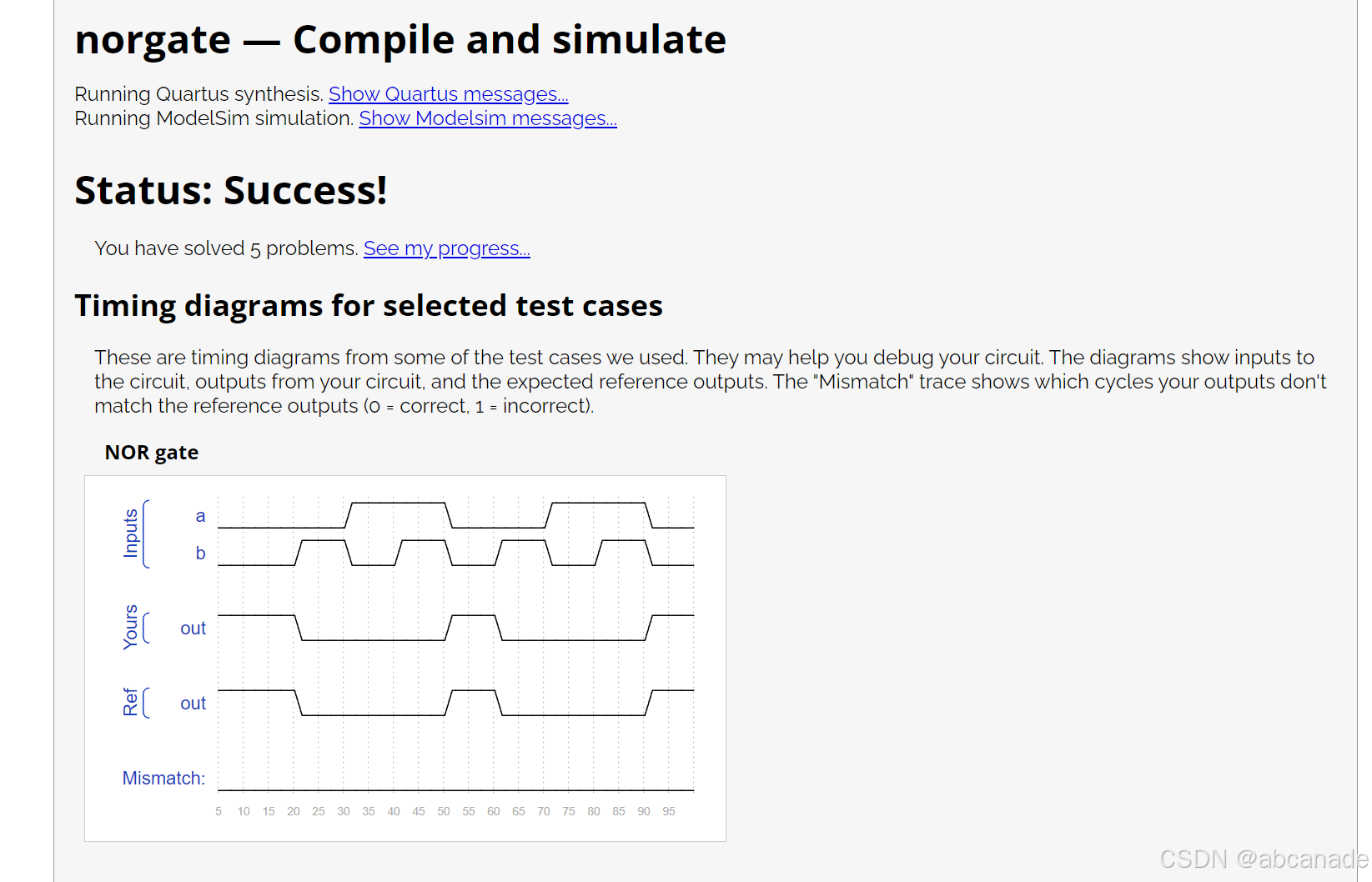

5 NOR gate

创建一个实现或非门的模块。或非门是输出反转的或门。在Verilog中编写NOR函数时需要两个运算符。

assign语句用一个值驱动一条线(或者更正式地称为“网”)。该值可以是任意复杂的函数,只要它是组合函数(即无内存、无隐藏状态)。assign语句是一种连续赋值,因为每当其任何输入发生变化时,都会“重新计算”输出,就像一个简单的逻辑门一样。

module top_module(

input a,

input b,

output out );

assign out = ~(a | b);

endmodule