RISC-V 是一种开源的可扩展指令集架构 (ISA),在过去几年中广受欢迎。RISC-V 的主要特性之一是它采用整体架构中性设计,支持浮点运算、加载存储架构、符号扩展加速和多路复用器简化。这使得 RISC-V 成为 FPGA 上软处理器的经济实惠的选择。自 RISC-V ISA 推出以来,支持 Linux 的 RISC-V CPU 一直备受关注,GitHub上出现了一些非常棒的选项,例如 CORE-V CVA6 。

CORE-V CVA6是一款六级、单发射、有序 CPU,可实现 64 位 RISC-V 指令集。该 CPU 实现了三个特权级别(M、S、U),以完全支持类 Unix 操作系统(如 Linux),并符合外部调试规范草案 0.13。CVA6 核心的目标是以合理的速度和 IPC(每周期指令数)运行完整的操作系统。

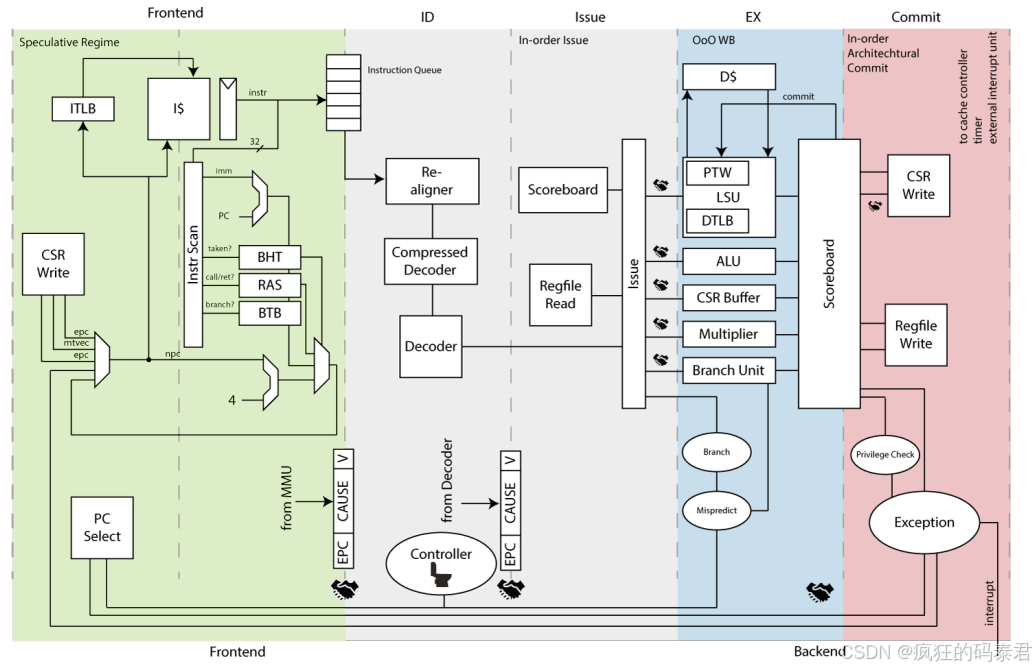

CORE-V CVA6(也称为 Ariane CPU)通过六级流水线设计实现了这一目标(在上面的块设计图中从左到右):

PC Gen 阶段— PC 生成是流水线中的前端阶段,负责生成下一个程序计数器,并使用握手信号与指令获取 (IF) 阶段进行通信。IF 通过断言就绪信号来表示其就绪状态,而 PC Gen 通过断言有效信号来表示有效请求。

IF 阶段— 流水线中的另一个前端阶段是指令提取阶段 (IF),它从 PC Gen 阶段获取信息,用于分支预测、当前程序计数 (PC) 以及请求是否有效。然后,IF 阶段请求 MMU 转换请求 PC 上的地址,并控制指令内存接口。

ID 阶段— 指令解码阶段是处理器后端的第一个流水线阶段。它从 IF 阶段获得的数据流中提取指令并解码,然后将其发送到发出阶段。

发出阶段——发出阶段接收解码后的指令,然后将其发送到各个功能单元,例如 ALU、CSR、LSU、乘法器等。发出阶段还跟踪所有发出的指令、功能单元状态,并接收来自执行阶段的写回数据。

EX 阶段— 执行阶段是一个逻辑阶段,它封装了所有功能单元 (FU),即 ALU、分支单元、加载存储单元 (LSU)、乘法器和 CSR 缓冲区。CVA6 架构中的每个 FU 都没有单元间依赖性,并且彼此独立地执行所有操作。

提交阶段——这是最后阶段,负责获取传入的指令以更新架构状态,管理各种异常源,并控制处理器的整体停顿。

此外,CPU 还具有记分板功能,可通过发出与数据无关的指令来隐藏数据缓存的延迟,从而提高设计的整体 IPC。L1 指令缓存的访问延迟为命中时的一个周期,而 L1 数据缓存的访问延迟为命中时三个周期。

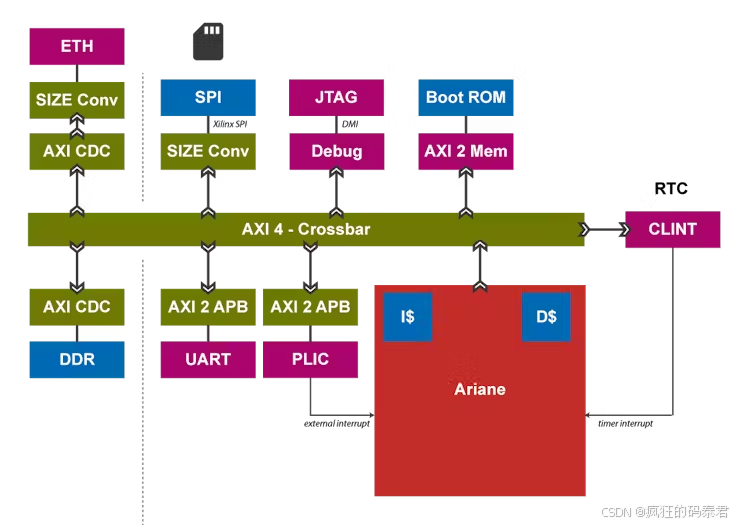

CORE-V CVA6 目前已在 Digilent 的基于Genesys 2 Kintex 的 FPGA 开发板上运行。Ariane CPU 通过 AXI-4 和两个输入中断连接到 FPGA 的外围设备。以太网控制器目前仍在开发中,因此 Ariane CPU 还不具备联网能力,但预计很快就会有更新。

负责开发 Ariane CPU 的OpenHW 集团在提供有关如何在 CPU 上开始运行用户空间应用程序、在 FPGA 上进行模拟以及后续调试技巧的文档方面做得非常出色。

存储库的问题部分也得到了开发人员的大量关注,因此这肯定会成为当前和未来项目需要牢记的 RISC-V 软处理器选项。