目录

1 一位加法器

1.1 半加器

半加器是实现两个1位二进制进行相加,并且输出这两个数的和以及进位的数字电路。半加器不需要考虑低位的进位。

考虑如何用电路来实现1位加法。输入的是有两个数为二进制数A、B,它们的和为1位二进制数S,如果产生进位为二进制C,那么存在如下枚举:

- 如果A=0、B=0,则S=0。

- 如果A=0、B=1,则S=1。

- 如何A=1、B=0,则S=1。

- 如何A=1、B=1,那么S=0,而产生一个进位CO=1。

真值表如下所示:

| A | B | S |

CO |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

通过真值表可以判断半加器的逻辑式如下所示:

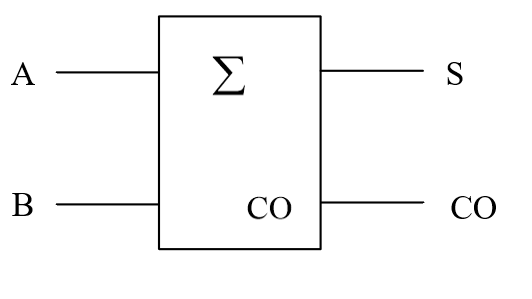

半加器的符号形式为:

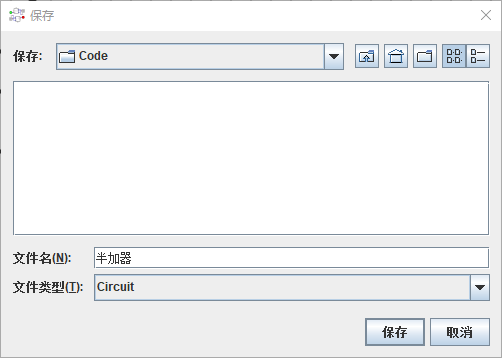

下面使用Digital软件来构建半加器。这个半加器电路会在之后的全加器电路中作为子电路,因此首首先点击文件选项栏中的新建子电路,半加器的电路图如下所示:

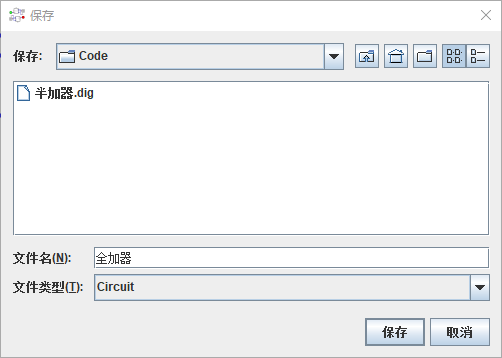

可以将这个半加器保存,作为之后全加器的使用的组件,保存示意图如下所示:

1.2 全加器

当多于1位的二进制数相加时,除了最低位以外,其他位置可能会有低位的进位,此时这个加法器被称为全加器。

如下所示为1位全加器的真值表:

| CI | A | B | S | CO |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

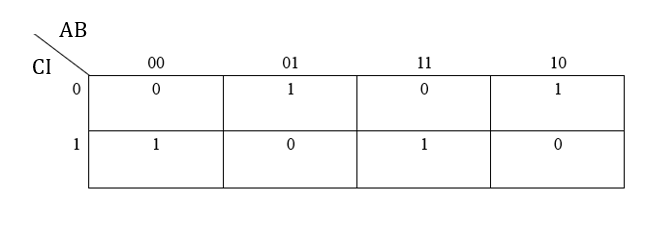

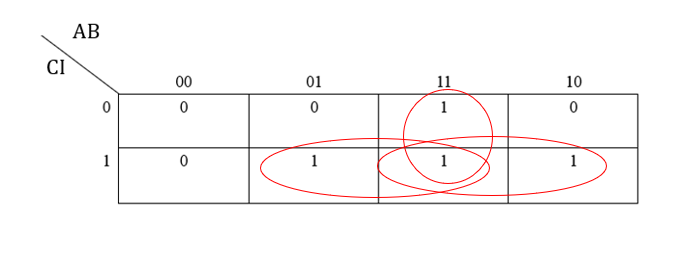

输出变量S卡诺图如下所示:

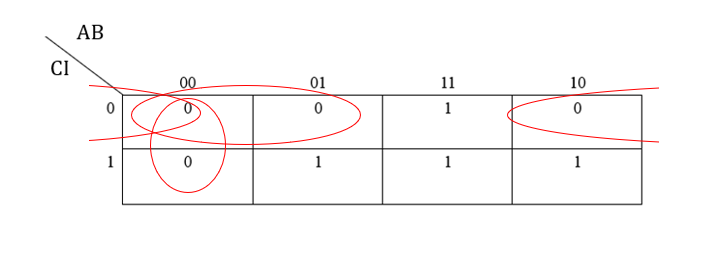

输出变量CO的卡诺图如下所示:

上图中是圈出卡诺图带1的项,另一种画法是圈出卡诺图中带0的项,如下所示:

输出变量S的逻辑式为:

输出变量C的逻辑式为:

或者为:

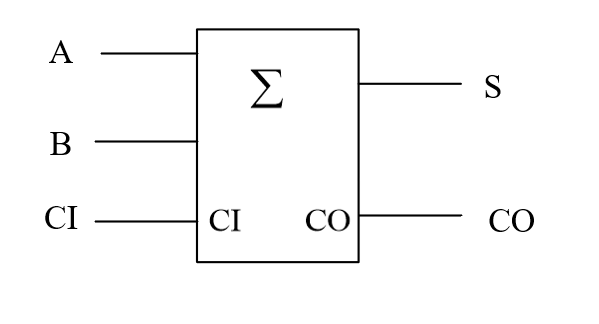

全加器的简化符号如下所示:

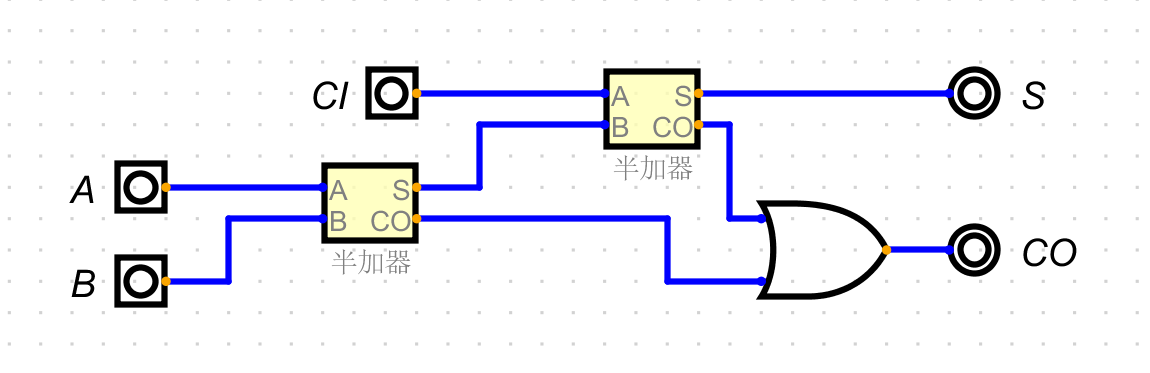

下面使用Digital软件模拟全加器,利用之前的半加器来构建全加器,电路图如下所示;

将其保存为全加器:

此电路可以作为多位加法器的子电路。

2 多位加法器

2.1 多位加法器简介

2.1.1 串行进位加法器

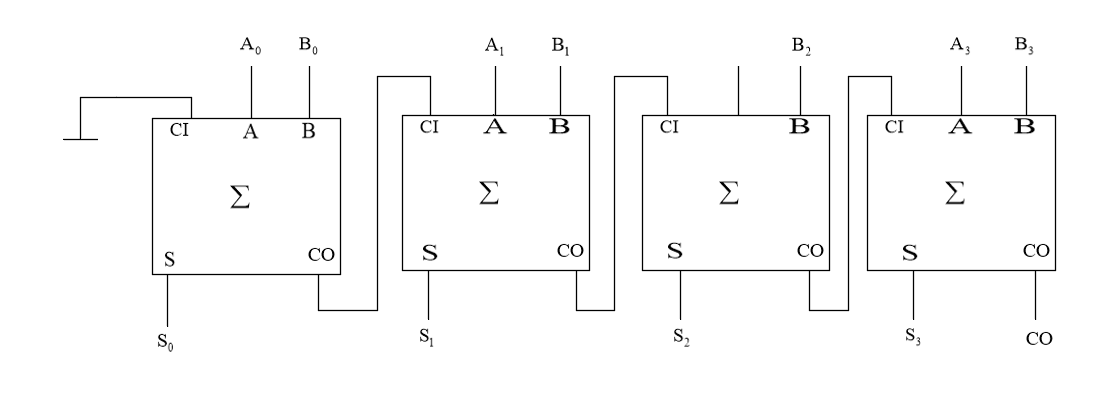

将加法器串联起来就是多位加法器。电路图如下所示:

串行加法器其核心原理是将多个全加器按位串联,依次处理每一位的相加和进位。每个全加器接收两个输入数的对应位及低位的进位信号,输出当前位的和并向高位传递进位。这种方式结构简单、硬件开销小,适用于低位宽和对速度要求不高的情况。

这种电路的优点为简单、复用性好,缺点为当输入发生变化时输出不可信,(传播延迟)特别高,

(导通延迟)特别短。

`2.1.2 超前进位加法器

超前进位加法器是放弃了串行进位的方式,改用并行进位的一种加法器。与传统的串行加法器对比,显著减少了因为低位等待而产生的延迟,超前进位加法器适合大宽位的计算。

对于第i位的输出变量CO,可以表示为:

而又可以写为:

因此输出变量CO可以推为:

通过这种方式第i位的可以用

、

和

来表示。

对于第i位的输出变量S,可以表示为:

而又可以写为:

因此输出变量S可以推为:

通过这种方式第i位的S可以用、

和

来表示。

对于四位二进制的超前进位加法器的实例:

、

和

可以依次推出,这里省略。

由上面的计算结果可以看到,使用这种超前进位的加法器相对于串行进位的加法器来说,显著提升了电路的复杂程度,但是两个加数送到输入端到完成加法运算只需要三级门电路的传输延迟时间,从而获得进位输出信号仅需要一级反相器和一级与非门的传输延迟时间。

2.2 使用Digital软件来实现多位加法器。

在Digital软件实现多位加法器,一共有两个输入变量A和B以及输出变量S,这里输入变量CI和输出变量CO统一使用C来 表示。

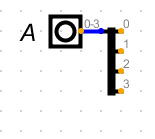

可以使用分裂器/合并器来实现输入和输出,例如对于四位变量A,如下所示:

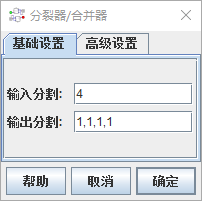

将输入A连接分裂器/合并器,并且如下设置:

设置之后如下所示:

在电路中,使用分裂器/合并器来完成四位的输入与输出,只需将输入信号的输入分割设置为4,然后将输出分割设置为1,1,1,1,这样设置的目的是输入的十进制转换为对应的二进制数的输入。需要主要的是与输出信号S相连的分裂器/合并器与输入信号的输入分割、输出分割是相反的,输出信号S的输入分割为1,1,1,1,输出分割为4,如下所示:

同时需要注意的是对于输入变量A、B和输出变量S来说,数据位数都要设置为4,直接右键点击输入变量和输出变量进行设置即可。

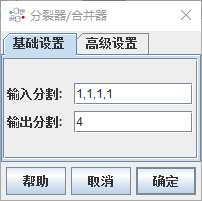

然后开始连接隧道,点击组选项栏中选择导线,然后在导线选项栏中选择隧道,放置到分裂器/合并器旁边,并且设置标签,例如一般将输入变量A的四个隧道分别设置为,并且将四个隧道复制放置在四个加法的引脚A旁边,并且连接引脚A。最终如下所示:

如果将第一个加法认为是最低位,那么可以将第一个加法器引脚CI连接低电平,然后引脚CO连接下一个加法器的引脚CI,依次连接,最后一个加法器的引脚CO连接输出变量CO。

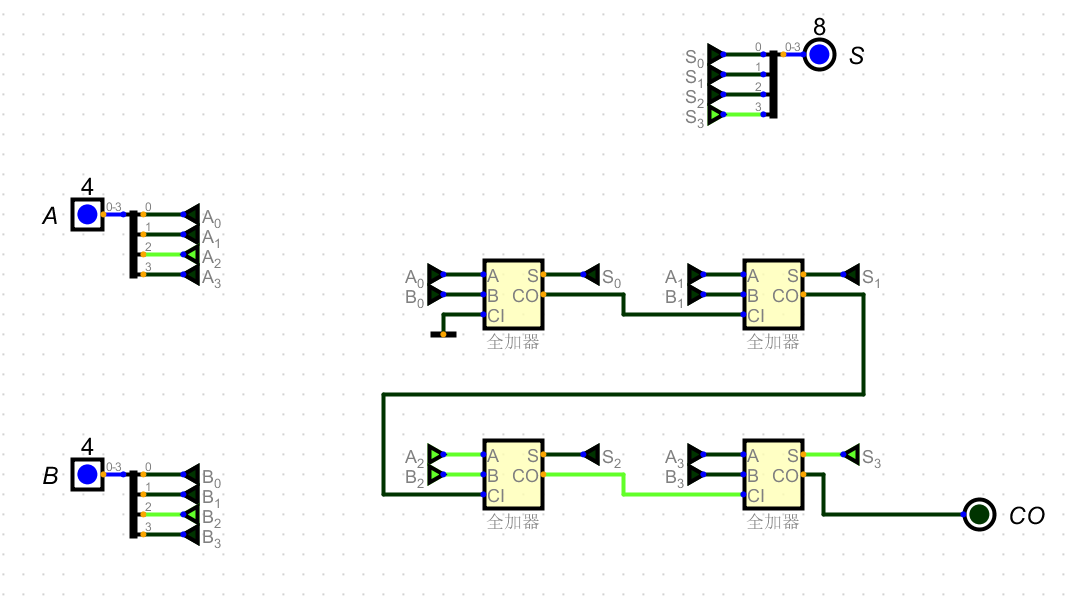

最终电路图如下所示:

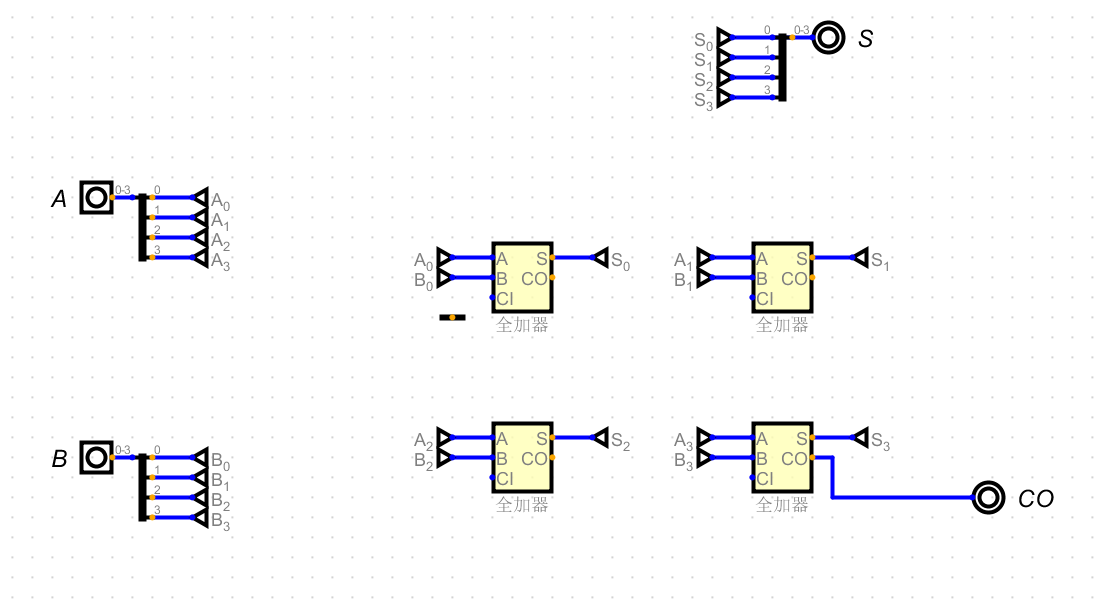

运行该电路,当A输入为4,B输出为5时,此时电路如下所示:

可以看到输出为9,符合相加结果。

当A输入为4,B输入为4时:

可以看到输出结果为8,符合加法器运算结果。

另一种画法是直接使用Digital软件中的组件,点击组选项栏中点击运算器,在运算器选项栏中点击加法器,最终电路如下所示:

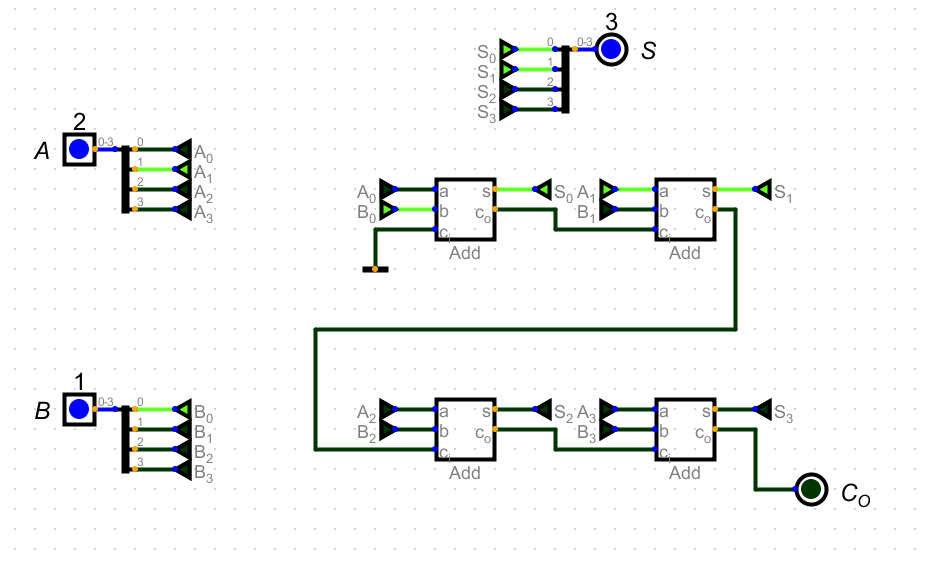

运行该电路,当A输入为2,B输入为1时:

此时电路输出为3,符合加法运算。

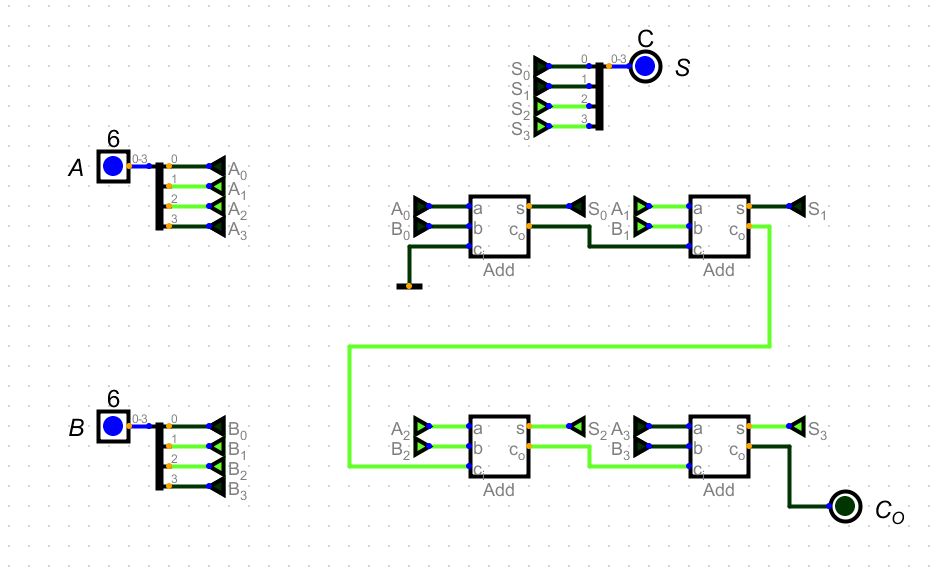

当A输入为6,B输入为1时:

可以看到输入为十六进制的C,即为十进制的12,符合加法运算。

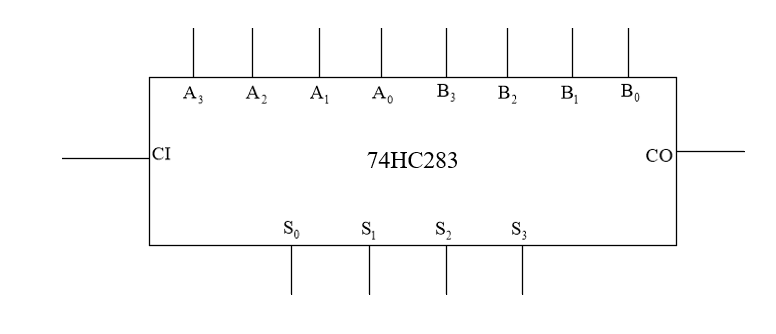

3 74HC283芯片介绍

74HC283芯片是一种超前进位的加法器,能够快速完成两个加法器之间的进位运算,并且支持进位输入和进位输出,其超前进位机制显著提升了运算速度,是复杂加法器的理想选择,74HC283芯片的电路图如下所示:

其逻辑框图如下所示: