目录

前言

一、设计流程

1.1 需求理解

1.2 模块划分

1.3 测试验证

二、模块分工

2.1 RGMII→GMII(接收方向,rgmii_rx 模块)

2.2 GMII→RGMII(发送方向,rgmii_tx 模块)

三、代码实现

3.1 顶层模块 rgmii_to_gmii

3.2 接收模块 rgmii_rx

3.3 发送模块 rgmii_tx

3.4 测试平台模块 tb

四、逻辑分析

4.1 双向转换的关键逻辑实现

4.2 双向转换逻辑的逻辑验证

五、注意事项

5.1 时钟处理

5.2 数据转换

5.3 测试验证

六、本文总结

七、更多操作

前言

在现代网络通信系统中,为了减少引脚数量并提高传输速率,RGMII 被广泛应用。在 FPGA 开发中,RGMII 和 GMII 是常见的网络接口标准。RGMII 接口具有信号线少、传输效率高的特点,而 GMII 接口则相对更易于理解和处理。在实际应用中,如与传统设备兼容时,常常需要在这两种接口之间进行数据转换。这里将详细介绍 RGMII 到 GMII 接口转换的设计流程、代码实现以及注意事项。

RGMII(Reduced Gigabit Media Independent Interface):简化的千兆媒体独立接口

GMII(Gigabit Media Independent Interface):千兆介质专用接口

更多 GMII RGMII 解析,请看

一、设计流程

1.1 需求理解

在进行接口转换设计之前,需要明确 RGMII 和 GMII 接口的特点和差异。RGMII 接口采用双沿数据传输,而 GMII 接口采用单沿数据传输。因此,设计的核心是实现双沿数据和单沿数据之间的转换。

1.2 模块划分

根据功能需求,将整个设计划分为三个主要模块:

- 顶层模块

rgmii_to_gmii - 接收模块

rgmii_rx - 发送模块

rgmii_tx

顶层模块负责连接各个子模块,接收模块将 RGMII 的双沿数据转换为 GMII 的单沿数据,发送模块将 GMII 的单沿数据转换为 RGMII 的双沿数据。

1.3 测试验证

设计完成后,需要编写测试平台对整个系统进行功能验证,确保接口转换的正确性。最后,通过tb(Test Bench)模块,对设计模块(如 rgmii_to_gmii)进行功能验证,确保接口转换的逻辑正确性。

二、模块分工

各模块核心作用:

| 模块 | 转换方向 | 核心功能 |

|---|---|---|

rgmii_to_gmii |

双向(RGMII↔GMII) | 顶层整合模块,实例化 rgmii_rx 和 rgmii_tx,实现 RGMII 与 GMII 接口的双向转换:- 连接 RGMII 侧(PHY)与 GMII 侧(MAC)的时钟、数据、控制信号 - 传递接收方向(RGMII→GMII)和发送方向(GMII→RGMII)的数据流 - 统一管理时钟同步(如将 GMII 时钟映射为 RGMII 发送时钟) |

rgmii_rx |

RGMII → GMII(接收) | 将 RGMII 的双沿数据(4 位,上下沿各 2 位)和控制信号转换为 GMII 的单沿数据(8 位,仅上升沿有效): - 利用 IDDR 原语提取时钟双沿的信号- 时钟处理( BUFIO/BUFG)确保 GMII 时钟质量- 控制信号转换(双沿有效 → 单沿使能) |

rgmii_tx |

GMII → RGMII(发送) | 将 GMII 的单沿数据(8 位,仅上升沿有效)和控制信号转换为 RGMII 的双沿数据(4 位,上下沿各 2 位): - 利用 ODDR 原语生成双沿数据和控制信号- 时钟同步(直接复用 GMII 时钟作为 RGMII 发送时钟) |

tb(Test Bench) |

无(测试验证) | 测试平台模块,不参与实际接口转换,仅用于仿真验证: - 生成时钟激励(125MHz,50% 占空比) - 驱动输入信号(RGMII 接收数据、GMII 发送数据)递增变化 - 验证输出信号是否符合双向转换逻辑(如双沿数据拼接 / 拆分的正确性) |

双向转换的核心模块:

| 模块 | 转换方向 | 核心功能 |

|---|---|---|

rgmii_rx |

RGMII → GMII(接收) | 将 RGMII 的双沿数据(4 位,上下沿各 2 位)和控制信号转换为 GMII 的单沿数据(8 位,仅上升沿有效)。 |

rgmii_tx |

GMII → RGMII(发送) | 将 GMII 的单沿数据(8 位,仅上升沿有效)和控制信号转换为 RGMII 的双沿数据(4 位,上下沿各 2 位)。 |

2.1 RGMII→GMII(接收方向,rgmii_rx 模块)

- 输入(RGMII 侧):

- 时钟

rgmii_rxc(PHY 提供,双沿同步) - 双沿数据

rgmii_rxd[3:0](上升沿传高 2 位[3:2],下降沿传低 2 位[1:0]) - 控制信号

rgmii_rx_ctrl(RXDV 和 RXER 的异或,双沿有效)

- 时钟

- 输出(GMII 侧):

- 时钟

gmii_rxc(经时钟缓冲处理,供 GMII 使用) - 单沿数据

gmii_rxd[7:0](rgmii_rxd双沿数据拼接:上升沿数据放低 4 位,下降沿数据放高 4 位?需结合代码逻辑,实际代码中IDDR的 Q1 对应上升沿,Q2 对应下降沿,拼接为[i]和[4+i],即 0-3 位为上升沿采样,4-7 位为下降沿采样) - 使能信号

gmii_rx_en(由双沿控制信号相与生成,确保数据有效时持续高电平)

- 时钟

2.2 GMII→RGMII(发送方向,rgmii_tx 模块)

- 输入(GMII 侧):

- 时钟

gmii_txc(FPGA 内部时钟,125MHz,单沿驱动) - 单沿数据

gmii_tx_data[7:0](仅上升沿有效,高 4 位和低 4 位分别对应 RGMII 双沿的上下沿) - 使能信号

gmii_tx_en(单沿有效,控制数据发送)

- 时钟

- 输出(RGMII 侧):

- 时钟

rgmii_txc(与gmii_txc同频,供 PHY 使用) - 双沿数据

rgmii_data[3:0](gmii_tx_data高 4 位[7:4]对应上升沿,低 4 位[3:0]对应下降沿,通过ODDR双沿输出) - 控制信号

rgmii_tx_ctrl(由gmii_tx_en双沿驱动,确保上下沿数据均有效)

- 时钟

125M的时钟,一个时钟8ns,4ns反转一次就可以。

三、代码实现

3.1 顶层模块 rgmii_to_gmii

`timescale 1ns / 1ps

module rgmii_to_gmii(

//rgmii接口

input wire rgmii_rxc ,//由phy提供的时钟

input wire rgmii_rx_ctrl ,//由en和error的异或值组成

input wire [3:0] rgmii_rxd ,//由phy芯片提供的双沿数据

output wire rgmii_txc ,//发送给phy芯片的时钟

output wire rgmii_tx_ctrl ,//由en、error的异或值组成

output wire [3:0] rgmii_data ,//双沿数据

//gmii接口

output wire gmii_txc ,//fpga的时钟,125Mhz,可以用phy提供的时钟,需要做约束处理

input wire gmii_tx_en ,//使能---高有效

input wire [7:0] gmii_tx_data ,//单沿数据

output wire gmii_rxc ,//经过buf处理后的时钟

output wire gmii_rx_en ,//使能信号

output wire [7:0] gmii_rxd //经过单双沿源语处理后的单沿数据

);

// 将gmii_txc赋值为gmii_rxc

assign gmii_txc = gmii_rxc;

// 实例化接收模块

rgmii_rx rgmii_rx_u(

. rgmii_rxc (rgmii_rxc ) ,//由phy提供的时钟

. rgmii_rx_ctrl(rgmii_rx_ctrl) ,//由en和error的异或值组成

. rgmii_rxd (rgmii_rxd ) ,//由phy芯片提供的双沿数据

. gmii_rxc (gmii_rxc ) ,//经过buf处理后的时钟

. gmii_rx_en (gmii_rx_en ) ,//使能信号

. gmii_rxd (gmii_rxd ) //经过单双沿源语处理后的单沿数据

);

// 实例化发送模块

rgmii_tx rgmii_tx_u(

. gmii_txc (gmii_txc ),//fpga的时钟,125Mhz,可以用phy提供的时钟,需要做约束处理

. gmii_tx_en (gmii_tx_en ),//使能---高有效

. gmii_tx_data (gmii_tx_data ),//单沿数据

. rgmii_txc (rgmii_txc ),//发送给phy芯片的时钟

. rgmii_tx_ctrl(rgmii_tx_ctrl),//由en、error的异或值组成

. rgmii_data (rgmii_data ) //双沿数据

);

endmodule

逻辑实现流程:

- 首先将

gmii_txc赋值为gmii_rxc,确保两者时钟一致。 - 实例化

rgmii_rx模块,将 RGMII 接口的接收数据传递给该模块进行处理。 - 实例化

rgmii_tx模块,将 GMII 接口的发送数据传递给该模块进行处理。

此模块负责整合接收和发送功能。

3.2 接收模块 rgmii_rx

`timescale 1ns / 1ps

//gmii to rgmii----双沿转单沿数据

module rgmii_rx(

input wire rgmii_rxc ,//由phy提供的时钟

input wire rgmii_rx_ctrl ,//由en和error的异或值组成

input wire [3:0] rgmii_rxd ,//由phy芯片提供的双沿数据

output wire gmii_rxc ,//经过buf处理后的时钟

output wire gmii_rx_en ,//使能信号

output wire [7:0] gmii_rxd //经过单双沿源语处理后的单沿数据

);

wire [1:0] gmii_rx_ctrl;//寄存rgmii_rx_ctrl双沿的数据

//----------时钟处理

wire rgmii_rxc_bufio;//经过io时钟资源的输入时钟

wire rgmii_rxc_bufg ;//经过全局时钟网络资源的输入时钟

// 将gmii_rxc赋值为经过全局时钟网络资源处理后的时钟

assign gmii_rxc = rgmii_rxc_bufg;

// 使用BUFIO原语处理输入时钟

BUFIO BUFIO_inst (

.O(rgmii_rxc_bufio), // 1-bit output: Clock output (connect to I/O clock loads).

.I(rgmii_rxc) // 1-bit input: Clock input (connect to an IBUF or BUFMR).

);

// 使用BUFG原语处理输入时钟

BUFG BUFG_inst (

.O(rgmii_rxc_bufg), // 1-bit output: Clock output

.I(rgmii_rxc) // 1-bit input: Clock input

);

//--------ctrl的双单沿转换

// 将gmii_rx_en赋值为gmii_rx_ctrl的两个位相与的结果

assign gmii_rx_en = gmii_rx_ctrl [0] & gmii_rx_ctrl[1];

// 使用IDDR原语进行控制信号的双单沿转换

IDDR #(

.DDR_CLK_EDGE("SAME_EDGE_PIPELINED"), // "OPPOSITE_EDGE", "SAME_EDGE"

// or "SAME_EDGE_PIPELINED"

.INIT_Q1(1'b0), // Initial value of Q1: 1'b0 or 1'b1

.INIT_Q2(1'b0), // Initial value of Q2: 1'b0 or 1'b1

.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) IDDR_inst_rx_ctrl (

.Q1(gmii_rx_ctrl[0]), // 1-bit output for positive edge of clock

.Q2(gmii_rx_ctrl[1]), // 1-bit output for negative edge of clock

.C(rgmii_rxc_bufio), // 1-bit clock input

.CE(1'b1), // 1-bit clock enable input

.D(rgmii_rx_ctrl), // 1-bit DDR data input

.R(1'b0), // 1-bit reset

.S(1'b0) // 1-bit set

);

//----------数据的双单沿转换

genvar i;

// 使用generate语句进行数据的双单沿转换

generate

for (i = 0;i < 4 ;i = i + 1 ) begin:iddr_rxd

IDDR #(

.DDR_CLK_EDGE("SAME_EDGE_PIPELINED"), // "OPPOSITE_EDGE", "SAME_EDGE"

// or "SAME_EDGE_PIPELINED"

.INIT_Q1(1'b0), // Initial value of Q1: 1'b0 or 1'b1

.INIT_Q2(1'b0), // Initial value of Q2: 1'b0 or 1'b1

.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) IDDR_inst_rxd (

.Q1(gmii_rxd[i]), // 1-bit output for positive edge of clock

.Q2(gmii_rxd[4 + i]), // 1-bit output for negative edge of clock

.C(rgmii_rxc_bufio), // 1-bit clock input

.CE(1'b1), // 1-bit clock enable input

.D(rgmii_rxd[i]), // 1-bit DDR data input

.R(1'b0), // 1-bit reset

.S(1'b0) // 1-bit set

);

end

endgenerate

endmodule

逻辑实现流程:

- 时钟处理:使用

BUFIO和BUFG原语对输入时钟rgmii_rxc进行处理,确保时钟信号的质量,并将处理后的时钟输出给gmii_rxc。 - 控制信号转换:使用

IDDR原语在时钟的上升沿和下降沿分别采集rgmii_rx_ctrl的值,将这两个值存储在gmii_rx_ctrl中,然后将gmii_rx_ctrl的两个位相与得到gmii_rx_en。 - 数据转换:使用

generate语句和IDDR原语将rgmii_rxd的双沿数据转换为gmii_rxd的单沿数据。

3.3 发送模块 rgmii_tx

`timescale 1ns / 1ps

//GMII to RGMII---单沿转双沿数据

module rgmii_tx(

input wire gmii_txc ,//fpga的时钟,125Mhz,可以用phy提供的时钟,需要做约束处理

input wire gmii_tx_en ,//使能---高有效

input wire [7:0] gmii_tx_data ,//单沿数据

output wire rgmii_txc ,//发送给phy芯片的时钟

output wire rgmii_tx_ctrl,//由en、error的异或值组成

output wire [3:0] rgmii_data //双沿数据

);

// 将rgmii_txc赋值为gmii_txc

assign rgmii_txc = gmii_txc;

//--------ctrl的单双沿转换

// 使用ODDR原语进行控制信号的单双沿转换

ODDR #(

.DDR_CLK_EDGE("SAME_EDGE"), // "OPPOSITE_EDGE" or "SAME_EDGE"

.INIT(1'b0), // Initial value of Q: 1'b0 or 1'b1

.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) ODDR_tx_ctrl (

.Q(rgmii_tx_ctrl), // 1-bit DDR output

.C(gmii_txc), // 1-bit clock input

.CE(1'b1), // 1-bit clock enable input

.D1(gmii_tx_en), // 1-bit data input (positive edge)

.D2(gmii_tx_en), // 1-bit data input (negative edge)

.R(1'b0), // 1-bit reset

.S(1'b0) // 1-bit set

);

//--------数据的单双沿转换

genvar i;//定义循环变量,只能在generate这个循环语句中使用

// 使用generate语句进行数据的单双沿转换

generate

for (i = 0;i < 4 ;i = i + 1 ) begin:gmii_txd //定义标签,作为generate循环语句中的实例名称

ODDR #(

.DDR_CLK_EDGE("SAME_EDGE"), // "OPPOSITE_EDGE" or "SAME_EDGE"

.INIT(1'b0), // Initial value of Q: 1'b0 or 1'b1

.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) ODDR_tx_data (

.Q(rgmii_data[i]), // 1-bit DDR output

.C(gmii_txc), // 1-bit clock input

.CE(1'b1), // 1-bit clock enable input

.D1(gmii_tx_data[i]), // 1-bit data input (positive edge)

.D2(gmii_tx_data[4 + i]), // 1-bit data input (negative edge)

.R(1'b0), // 1-bit reset

.S(1'b0) // 1-bit set

);

end

endgenerate

endmodule

逻辑实现流程:

- 将

rgmii_txc赋值为gmii_txc,确保发送时钟一致。 - 控制信号转换:使用

ODDR原语将单沿的gmii_tx_en转换为双沿的rgmii_tx_ctrl。 - 数据转换:使用

generate语句和ODDR原语将单沿的gmii_tx_data转换为双沿的rgmii_data。

3.4 测试平台模块 tb

`timescale 1ns / 1ps

module tb();

// Parameters

// Ports

reg rgmii_rxc = 0;

reg rgmii_rx_ctrl = 0;

reg [3:0] rgmii_rxd;

wire rgmii_txc;

wire rgmii_tx_ctrl;

wire [3:0] rgmii_data;

wire gmii_txc;

reg gmii_tx_en = 0;

reg [7:0] gmii_tx_data;

wire gmii_rxc;

wire gmii_rx_en;

wire [7:0] gmii_rxd;

// 实例化顶层模块

rgmii_to_gmii

rgmii_to_gmii_dut (

.rgmii_rxc (rgmii_rxc ),

.rgmii_rx_ctrl (rgmii_rx_ctrl ),

.rgmii_rxd (rgmii_rxd ),

.rgmii_txc (rgmii_txc ),

.rgmii_tx_ctrl (rgmii_tx_ctrl ),

.rgmii_data (rgmii_data ),

.gmii_txc (gmii_txc ),

.gmii_tx_en (gmii_tx_en ),

.gmii_tx_data (gmii_tx_data ),

.gmii_rxc (gmii_rxc ),

.gmii_rx_en (gmii_rx_en ),

.gmii_rxd ( gmii_rxd)

);

initial begin

// 初始化输入信号

rgmii_rxc = 0 ;

rgmii_rx_ctrl = 1 ;

rgmii_rxd = 0 ;

gmii_tx_en = 1 ;

gmii_tx_data = 0 ;

end

// 生成时钟信号

always #4 rgmii_rxc = ~rgmii_rxc;

// 当gmii_rx_en有效时,rgmii_rxd在时钟的上升沿和下降沿加1

always@(posedge rgmii_rxc or negedge rgmii_rxc)begin

if(gmii_rx_en)begin

rgmii_rxd <= rgmii_rxd + 1;

end

end

// 当gmii_rx_en有效时,gmii_tx_data在时钟的上升沿加1

always@(posedge rgmii_rxc )begin

if(gmii_rx_en)begin

gmii_tx_data <= gmii_tx_data + 1;

end

end

endmodule

逻辑实现流程:

- 初始化输入信号,包括时钟信号、控制信号和数据信号。

- 生成时钟信号

rgmii_rxc,周期为 8ns。 - 当

gmii_rx_en有效时,rgmii_rxd在时钟的上升沿和下降沿加 1。 - 当

gmii_rx_en有效时,gmii_tx_data在时钟的上升沿加 1。

四、逻辑分析

4.1 双向转换的关键逻辑实现

① 双沿数据与单沿数据的映射关系

RGMII→GMII(接收方向):

- 数据转换:每个 RGMII 时钟周期传输 4 位(上下沿各 2 位),通过

IDDR原语在上升沿采样高 2 位(存入gmii_rxd[i]),下降沿采样低 2 位(存入gmii_rxd[4+i]),最终拼接为 8 位单沿数据(如rgmii_rxd[3:2]→gmii_rxd[0:1],rgmii_rxd[1:0]→gmii_rxd[4:5]?需注意代码中i的索引,实际代码中i从 0 到 3,Q1对应gmii_rxd[i],Q2对应gmii_rxd[4+i],即 0-3 位为上升沿采样,4-7 位为下降沿采样)。 - 控制信号:

rgmii_rx_ctrl在上下沿分别采样,通过IDDR得到两位信号,相与后作为 GMII 的使能信号gmii_rx_en(确保双沿数据均有效时才输出高电平)。

- 数据转换:每个 RGMII 时钟周期传输 4 位(上下沿各 2 位),通过

GMII→RGMII(发送方向):

- 数据转换:GMII 的 8 位单沿数据需拆分为 RGMII 的 4 位双沿数据,其中

gmii_tx_data[3:0]对应下降沿数据(存入rgmii_data[i]的下降沿输入D2),gmii_tx_data[7:4]对应上升沿数据(存入rgmii_data[i]的上升沿输入D1),通过ODDR原语在时钟上下沿分别输出。 - 控制信号:

gmii_tx_en单沿信号通过ODDR转换为双沿信号rgmii_tx_ctrl,确保 RGMII 侧上下沿数据均被使能。

- 数据转换:GMII 的 8 位单沿数据需拆分为 RGMII 的 4 位双沿数据,其中

② 时钟处理与同步

- 接收方向(RGMII→GMII):

- RGMII 时钟

rgmii_rxc由 PHY 提供,通过BUFIO和BUFG原语优化时钟路径,确保 GMII 侧时钟gmii_rxc的低抖动和低延迟,满足 GMII 接口的时序要求。

- RGMII 时钟

- 发送方向(GMII→RGMII):

- FPGA 内部时钟

gmii_txc直接作为 RGMII 时钟rgmii_txc,需通过时序约束(如时钟频率、占空比)确保与 PHY 的兼容性(通常为 125MHz,50% 占空比)。

- FPGA 内部时钟

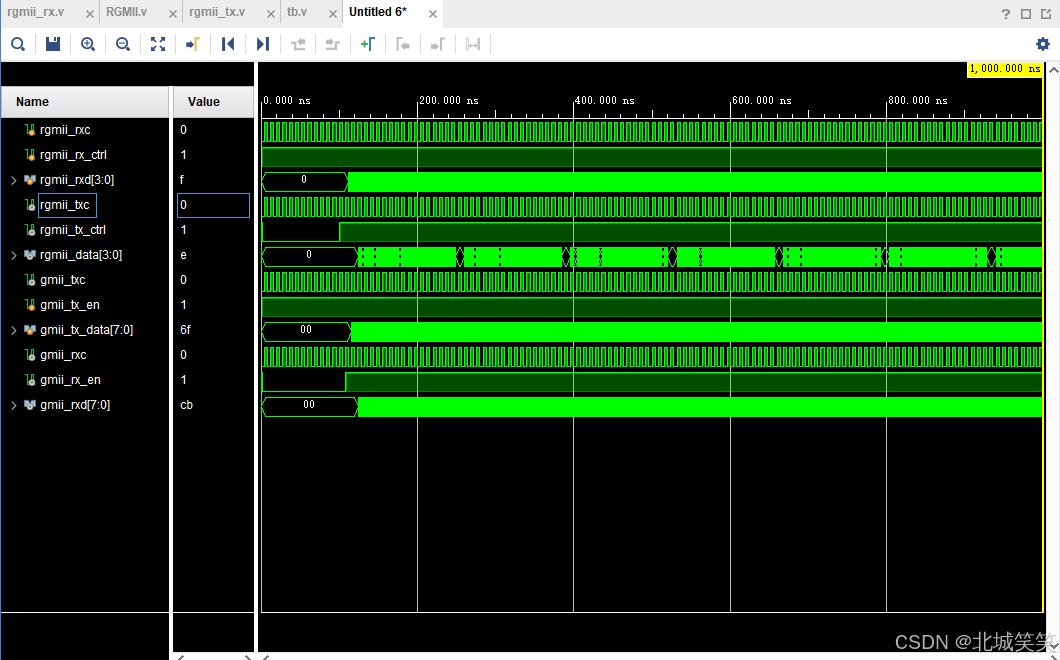

4.2 双向转换逻辑的逻辑验证

双向转换的验证逻辑,也就是tb 模块。测试平台通过以下方式验证双向转换的正确性:

- 时钟激励:生成 125MHz 时钟(周期 8ns),模拟 RGMII 和 GMII 的同步时钟。

- 数据递增:

- 当

gmii_rx_en有效时,RGMII 接收数据rgmii_rxd在上下沿递增(模拟 PHY 发送的双沿数据),验证 GMII 输出gmii_rxd是否正确拼接为 8 位单沿数据(如rgmii_rxd=0x5(二进制0101)时,上升沿01对应gmii_rxd[1:0]=01,下降沿01对应gmii_rxd[5:4]=01,最终gmii_rxd=0x15?需根据实际索引确认)。 - GMII 发送数据

gmii_tx_data在上升沿递增,验证 RGMII 输出rgmii_data是否正确拆分为双沿数据(如gmii_tx_data=0xA(二进制1010)时,上升沿数据10对应rgmii_data[3:2]=10,下降沿数据10对应rgmii_data[1:0]=10,最终rgmii_data=0xA)。

- 当

- 控制信号联动:确保

gmii_rx_en和rgmii_tx_ctrl在数据有效时保持高电平,无数据时拉低,避免无效数据传输。

五、注意事项

5.1 时钟处理

在进行接口转换时,时钟的处理非常重要。使用 BUFIO 和 BUFG 原语可以确保时钟信号的质量,避免时钟抖动和延迟对数据传输的影响。

5.2 数据转换

在进行双沿数据和单沿数据转换时,需要注意数据的对齐和时序关系。使用 IDDR 和 ODDR 原语时,要正确设置参数,确保数据的正确转换。

5.3 测试验证

在设计完成后,一定要进行充分的测试验证。可以使用仿真工具对测试平台进行仿真,观察各个信号的波形,确保接口转换的正确性。同时,还可以进行硬件测试,将设计下载到 FPGA 开发板上进行实际测试。

六、本文总结

本文围绕 FPGA 中 RGMII 与 GMII 接口的转换设计,详细阐述了从需求分析到代码实现的完整流程,重点解决了双沿数据与单沿数据之间的转换问题。通过模块化设计,将功能划分为顶层模块、接收模块(RGMII 转 GMII)和发送模块(GMII 转 RGMII),并利用 FPGA 的 IDDR/ODDR 原语实现双沿数据的采样与生成,确保了接口时序的严格对齐。

在接收模块中,通过 BUFIO 和 BUFG 原语优化时钟路径,使用 IDDR 提取时钟双沿的控制信号和数据,最终拼接为 GMII 所需的 8 位单沿数据;发送模块则通过 ODDR 将 GMII 的单沿数据映射到 RGMII 的双沿信号,实现高效的数据传输。测试平台通过时钟激励和数据递增逻辑,验证了接口转换的功能正确性。

设计中需特别注意时钟质量优化、双沿数据的时序对齐以及跨时钟域处理(如需),确保满足 IEEE 标准和硬件时序约束。该方案为 FPGA 网络接口设计提供了可复用的模板,适用于千兆以太网等高速数据传输场景,具有较强的工程实践价值。通过合理的模块划分和原语应用,可有效简化开发流程,提升系统稳定性。实际部署建议结合Xilinx的UltraScale Architecture PCB Design Guide进行板级优化,并通过Tcl脚本实现自动化时序检查。

七、更多操作

完整FPGA系列,请看

FPGA系列,文章目录![]() https://blog.csdn.net/weixin_65793170/article/details/144185217

https://blog.csdn.net/weixin_65793170/article/details/144185217