一、基本的版图层次

1. 金属层(Metal Layers)

- 金属层主要起到互连的作用,完成基本电路器件的连接

- 金属线的材质通常是铝或者铜,一般在线条比较粗的情况下,即特征尺寸比较粗的,一般是用铝制作的。在先进工艺(90nm以下)是采用铜制成的。

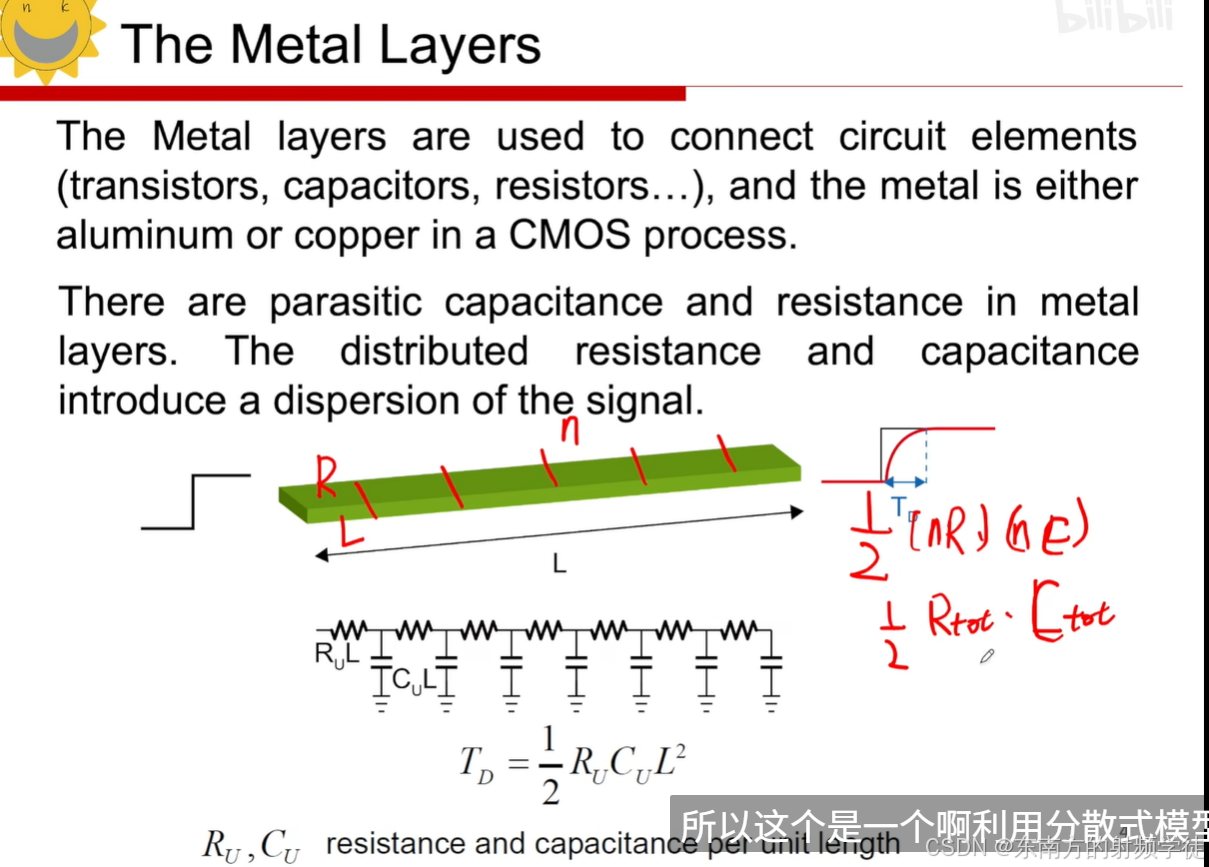

- 实际上加工出来的金属线是具有一定厚度的(大致为0.5um),它是会存在着寄生电容和电阻的。金属线与周围的金属线之间,无论是侧壁还是表面,都会形成平行板电容器的结构,所以会有寄生电容的现象。由于其是金属材质,也是会存在电阻的。因此这样的导线是不理想的。

- 所以用这样的金属线去传递一个阶跃信号,实际出来是会有很大失真的,相对于输入信号是有一定的延时。这样的信号传递就会引起信号的分散(dispersion)。也就是说,因为有了寄生电容和电阻的存在,这样的金属线对信号不同频率成分的响应速度是不一样的,导致输出端的信号会有一个延时的畸变。

- 这样的延时会采用分布式的电阻和电容模型去计算。分布式就是把长的金属线切成若干段,每一段都可以计算一下其寄生电阻和电容。总的延时可以采用1/2RtotalLtotal

- Ru和Cu表示单位长度的寄生电阻和电容

寄生电阻

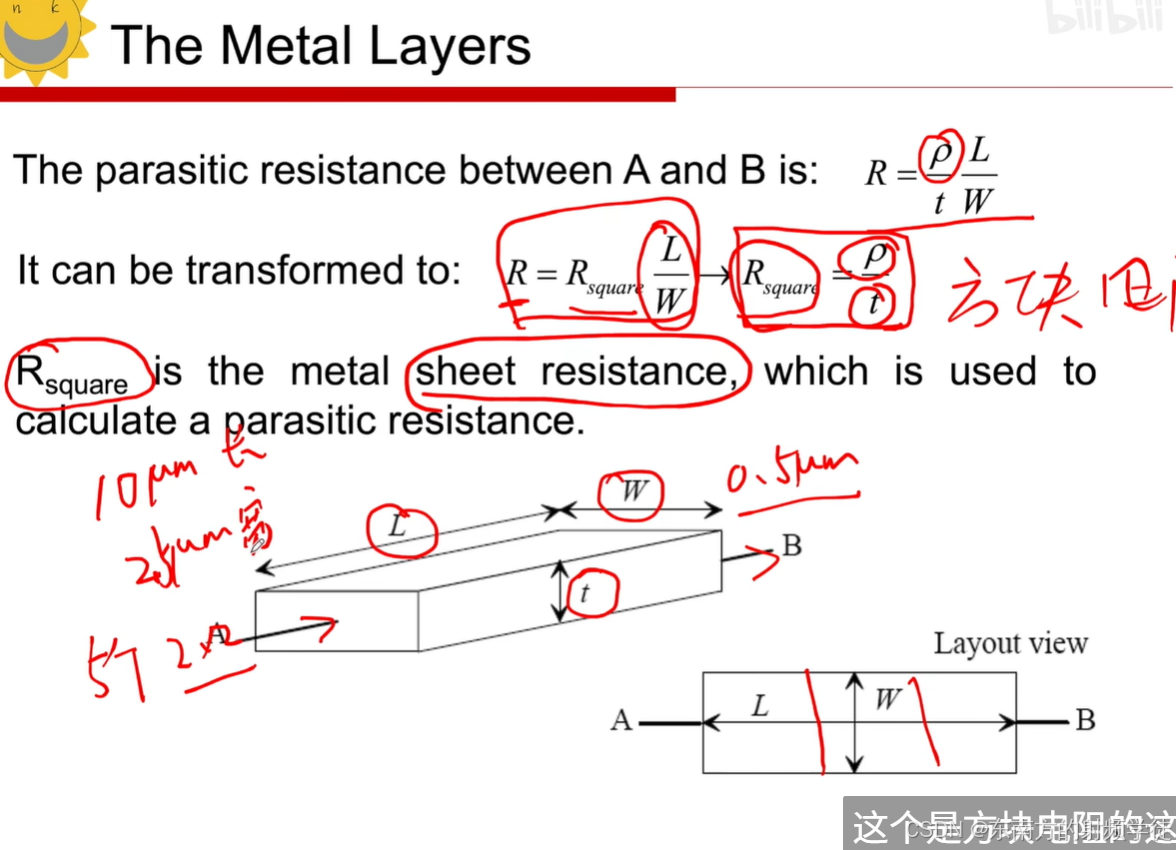

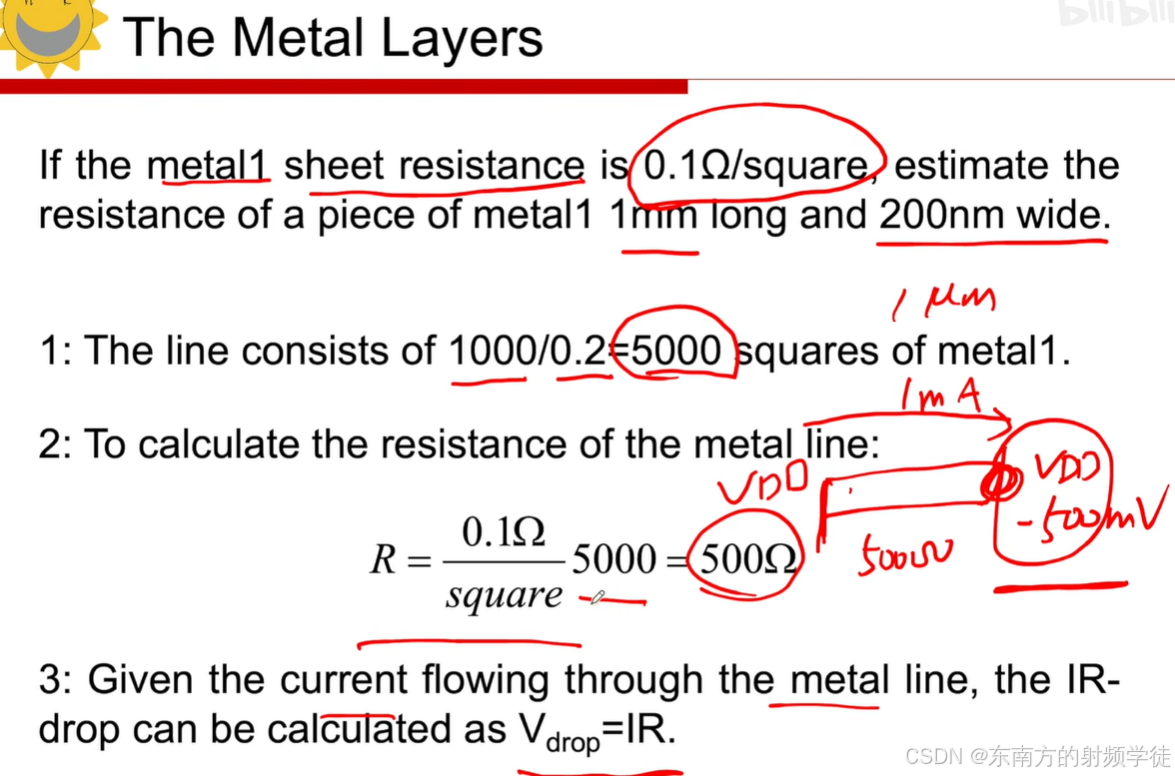

- 估算延时信息,就是计算其电阻和电容

- 在集成电路中,估算电阻用到的是sheet resistance(方块电阻)

- 实际加工出来的金属线是一个长方体,其长度为L,宽度是W,厚度为t。这样的长方体的电阻可以有下式子计算得到

R = ρ t L W ⏟ R=\underbrace{\frac{\rho}{t}\frac{L}{W}} R= tρWL - 其中ρ是电阻率

- 这里我们设定方块电阻Rsquare

R s q u a r e = ρ t R_{square}=\frac{\rho}{t} Rsquare=tρ - 用这样的方块电阻可以简单的计算金属线的寄生电阻的情况。对于特定工艺下的金属线,其材质(电阻率)和金属厚度是固定的,所以Rsquare也是一个定值。在集成电路工艺参数说明文件中,它会提供每层金属的Rsquare的值。所以我们在去计算金属线的寄生电阻值的时候,就可以采用下式计算

R = R s q u a r e L W R=R_{square}\frac{L}{W} R=RsquareWL - 用L/W得到导线内部的方块个数,不用考虑其厚度的问题。

- 用Metal1去绘制的金属线,通过计算得到的寄生电阻,在通过流过金属线的电流,可以得到流过金属线产生的压降Vdrop。

- 假设流过电流是1mA,那么其压降是500mV。电路设计者会给出这样宽度的导线所能承受的最大电压,那么对于版图设计者就会知道了这样的线应该画多宽才能满足电路的要求。画的线越宽,方块个数越小。防止因导线宽度不够,导致电路的压降太大而电路供电不足的问题。

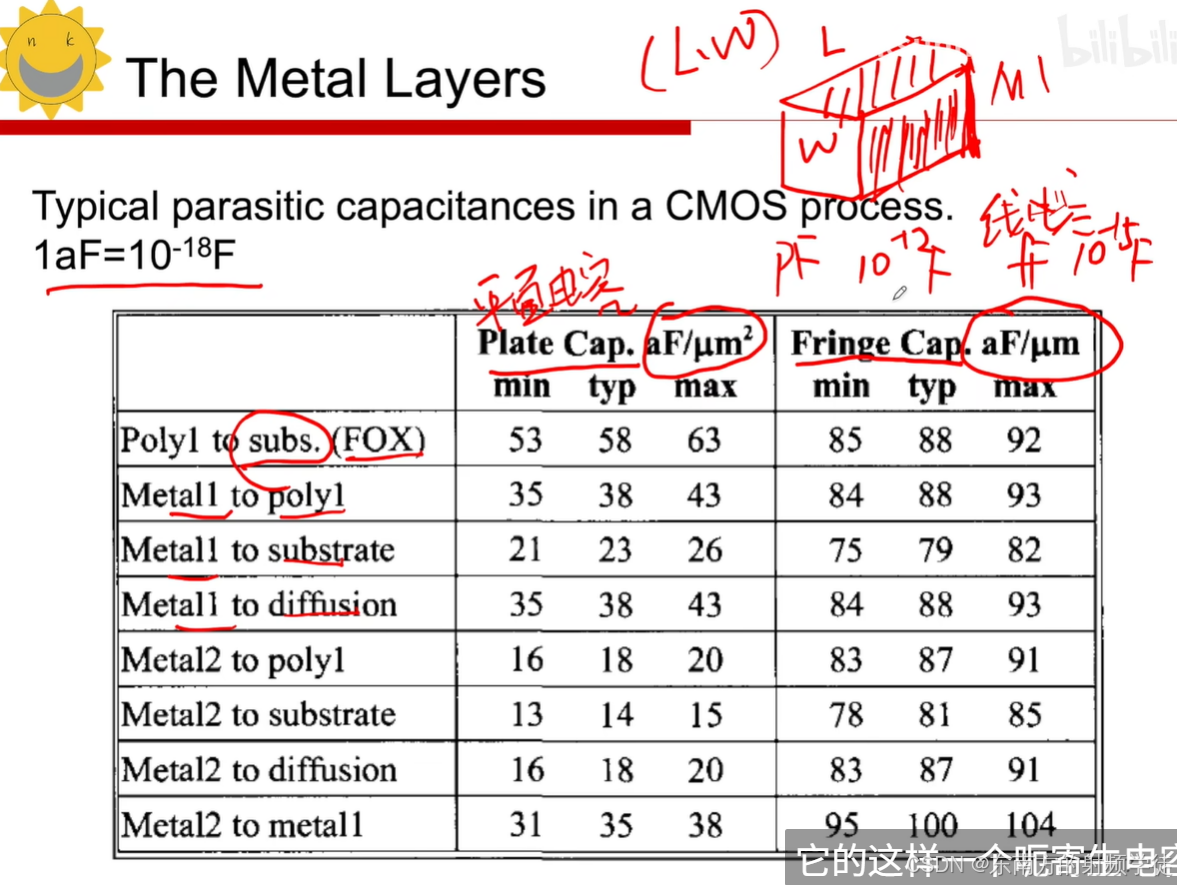

寄生电容

- 金属线相邻侧壁之间会有一些寄生的现象。存在两种寄生

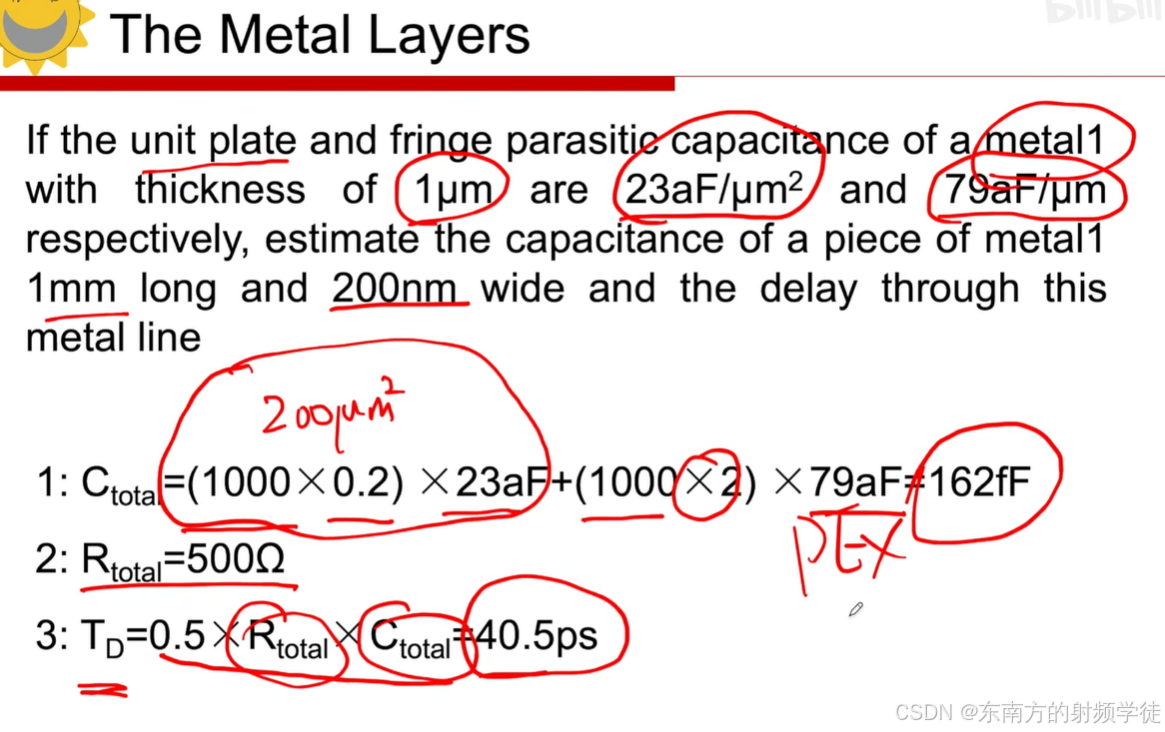

- 第一种是平面寄生(plate cap),它是导线的上表面或者下表面也其他金属表面形成的寄生电容,类似平行板电容器的结构。这可以用单位面积下的寄生电容去计算(aF:10E-18,比fF还要低的电容单位),然后乘以其面积。虽然数量级下比较小,但是这个寄生是不容忽视的。一旦金属线走的特别长,它的寄生也会非常大。但凡有两个相邻的平面,都会产生寄生电容

- 第二种是边缘寄生电容(fringe cap),其是金属的侧表面贡献的。由于其侧面的高度(也就是导线的厚度)是固定的,所以只需要其侧面的长度即可计算得到对应的寄生电容

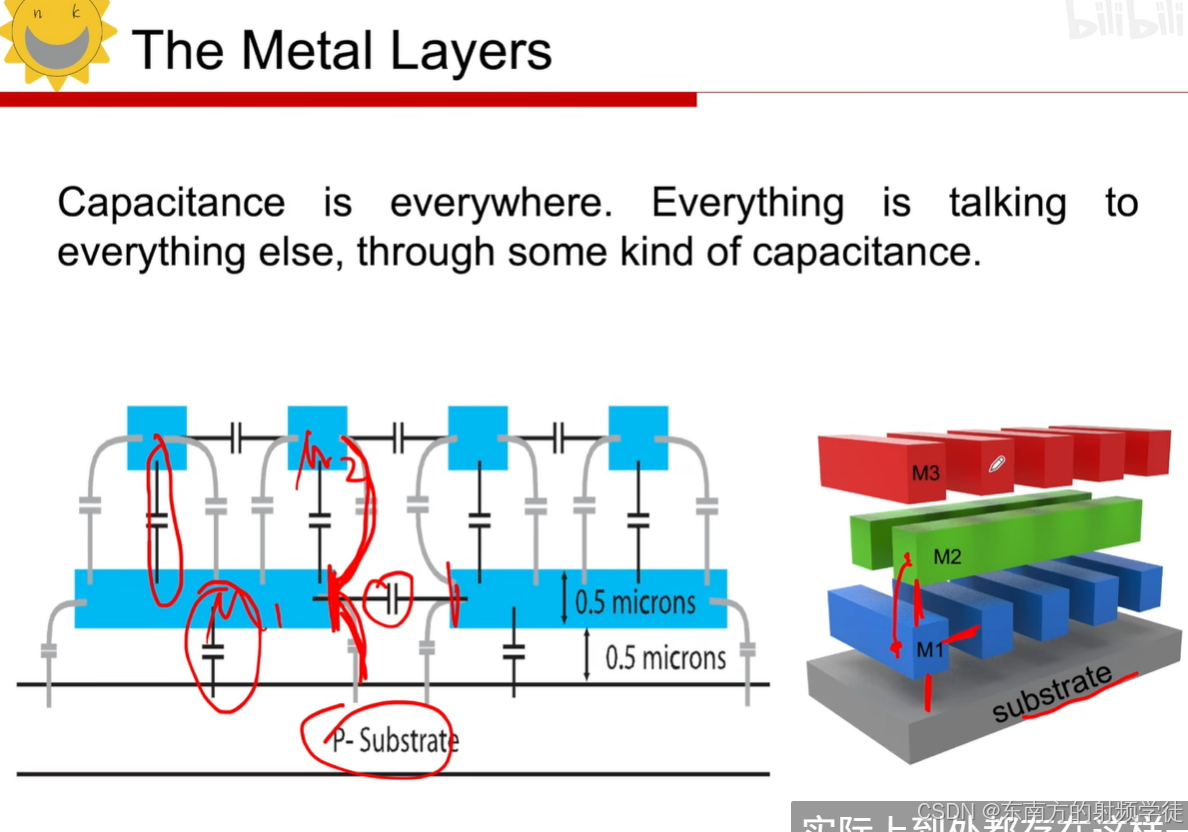

- 集成电路中会存在大量的寄生电容,会导致信号之间形成大量的信号串扰,就会影响到信号的纯净程度,导致电路出现一些性能的下降。

- 比如像左图这样的电路,底下的p衬底。M1金属线的下表面和上表面都会和其他的表面产生寄生(plate cap),M1的侧面与其他表面也会有寄生(Fringe cap)

- 下面这些计算都是粗略的估算,最后还是要通过PEX后提取把真实的寄生情况提取出来,得到更真实的分布模型去发推到原理图中去做后仿真,这样才能最终确定出来这个导线的延迟程度

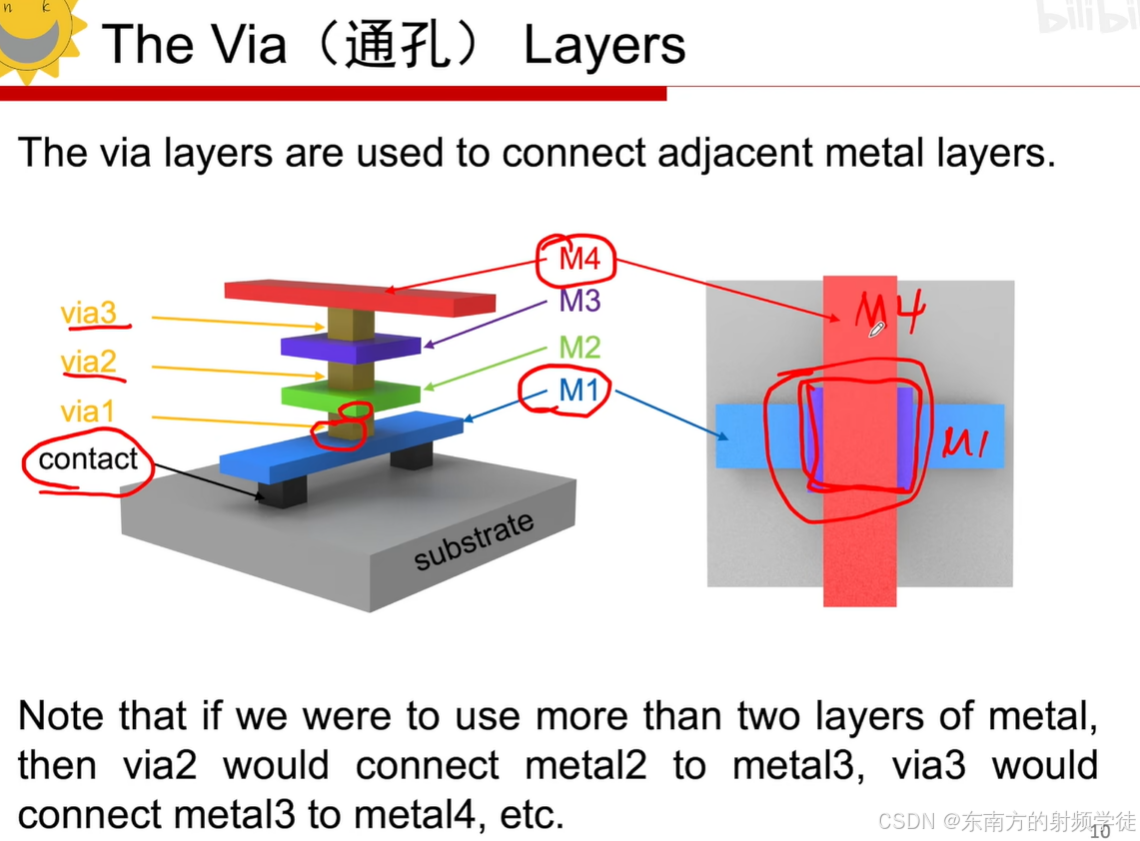

2. 通孔(via)

- 通孔的作用是连接不同层次的金属线。

- contact(CT)是用于衬底连接到第一层金属M1,或者是掺杂到金属M1,或者gate到金属

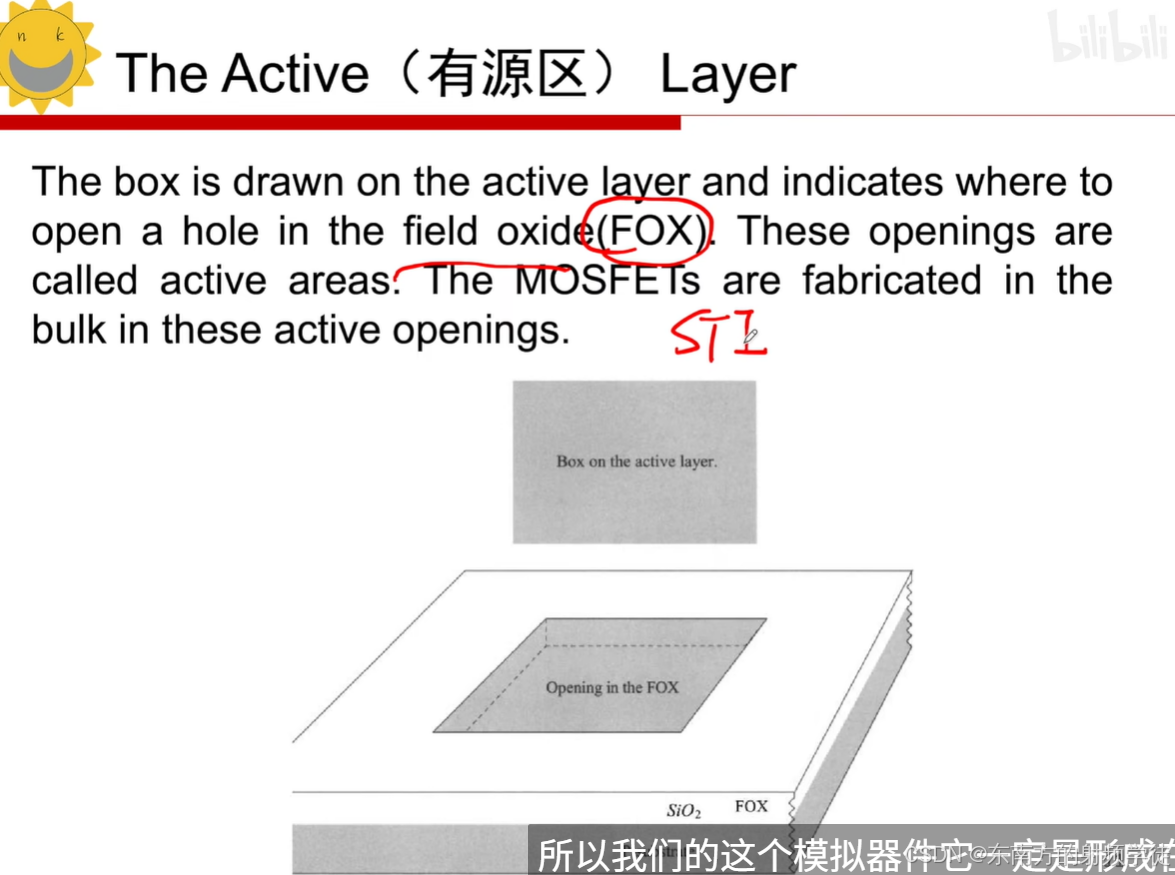

3. 有源区(active layer)

- 有源区的作用是用于绘制器件,或者衬底到接触的位置,都需要用有源区来定义

- 由于整个电路中,除了器件以外的位置,都是FOX(field oxide)场氧化层;先进工艺会使用STI(shallow transfer information)浅沟槽隔离。只有有源区的位置才是没有这种隔离的,在这个区域才能去加工有源器件。

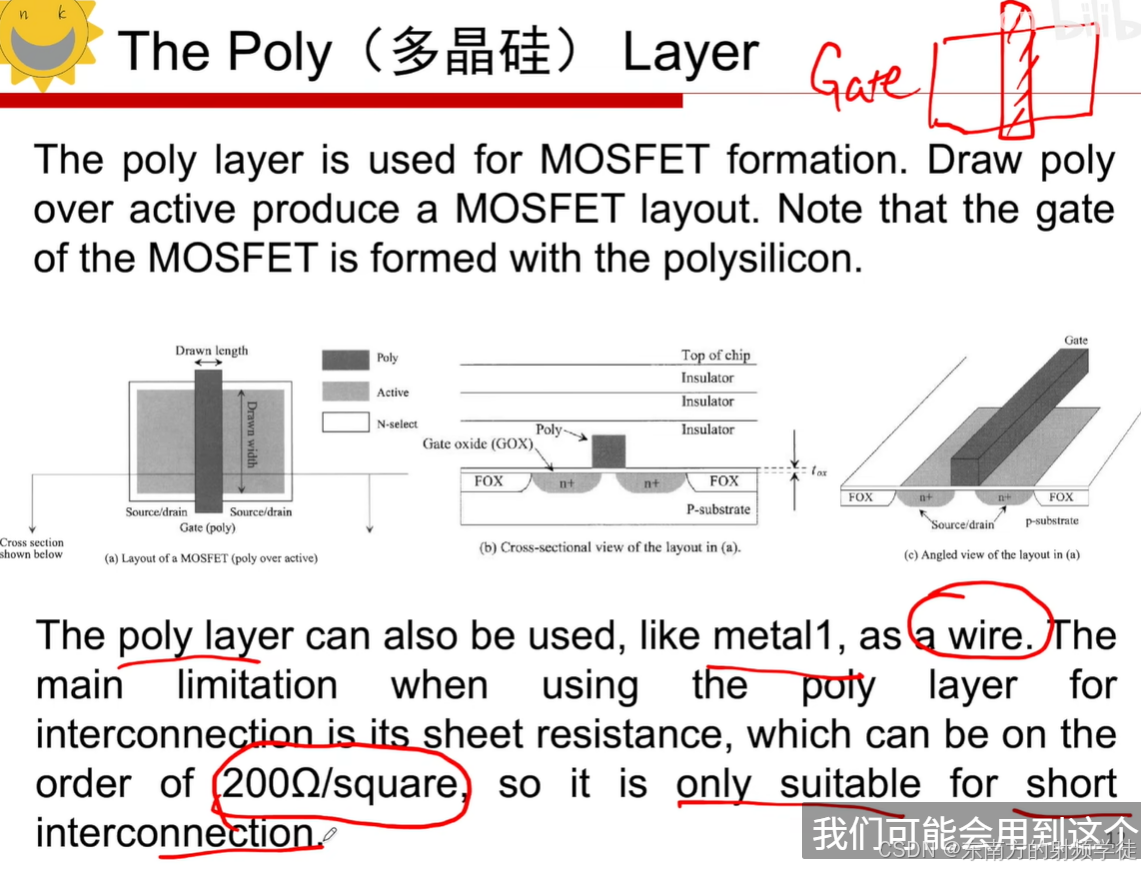

4. 多晶硅层(Poly)

- poly的第一个的作用就是形成mosfet的gate栅极。多晶硅层连接到M1也是通过contact连接的

- 多晶硅的第二个作用也可以充当信号互连线,类似M1,也可以充当导线来用。但问题是,其寄生电容会比较大,会达到每个方块200欧姆,金属线的寄生一般是每个方块0.1欧姆,它们之间差了两千倍的数量接情况。如果不是在迫不得已的情况下,一般是不会用poly做互连线的。但有的时候为了节省面积,并且这个信号的互连距离非常短,信号传递非常慢的情况,才可以用poly去做互连线,但不可以做长距离的互连线,只适合短距离的互连线。

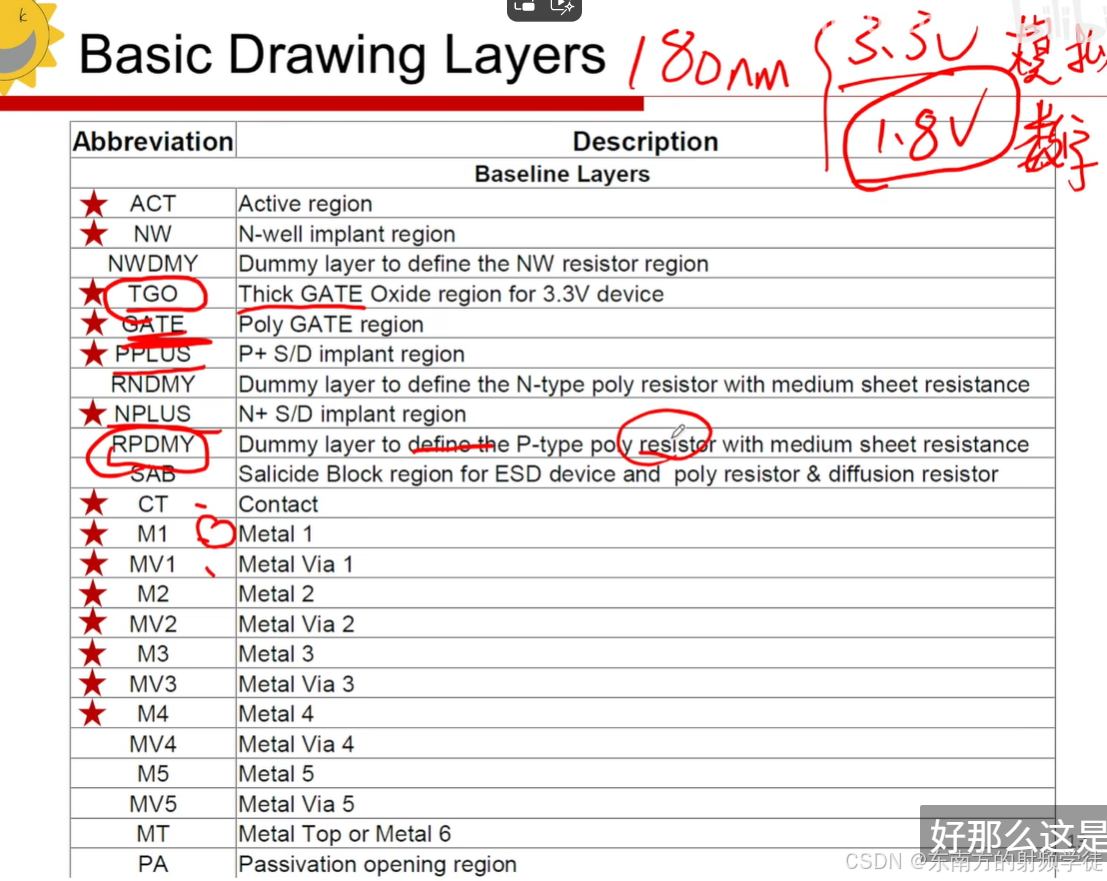

基本的layer层

- ACT:有源区

- NW:N阱

- TGO:Thick gate oxide主要用于定义厚氧化层的。在一般的CMOS工艺下,会提供两种供电电压的模型器件,比如180nm的工艺,会提供3.3v的器件或者1.8v的器件。

- 1.8v的器件可以使用更小的尺寸,这样可以去做一些数字电路;模拟电路不追求很小的沟道长度,因为沟道长度特别小的话,整个电路的特性都会变得很差,由于沟道长度调制效应,其阻抗也不会做的很高,模拟电路不喜欢用小沟道的尺寸,而喜欢用长沟道的器件,这样栅氧也会比较厚,供电电压也会比较高;供电电压高的好处是信号摆幅会比较大,信噪比的强度也会高一些。

- 这样也意味着同一个平台wafer上,既要加工一个3.3v的器件,也要技工1.8v的器件,这两个器件的gate oxide栅氧厚度是不一样的,因此需要有一个层次来区分这些东西,这就是TGO

- GATE:poly层,形成栅极,也可以做短距离的互连

- PPLUS:P+的注入

- NPLUS:N+的注入

- CT/MV1:通孔

- M1:金属线

- 除了这些层次layer以外,在一个工艺里面还会提供其他很多辅助的层次。其中有一些层次是有真实的掩膜板与之对应的(下图中画红色星号的层次layer),还有一些事辅助层次,比如RPDMY,是用来定义电阻器件的,它的作用更多是为了让这个软件如LVS/DRC去识别这是一个电阻器件,而不是poly,这些层次是没有真实掩膜板对应的,只是用于辅助版图设计

二、电路失效机制

- 我们在设计版图的时候,一定要注意这些失效机理,否则会导致版图设计的不够好,最终加工出来的电路是失效的。

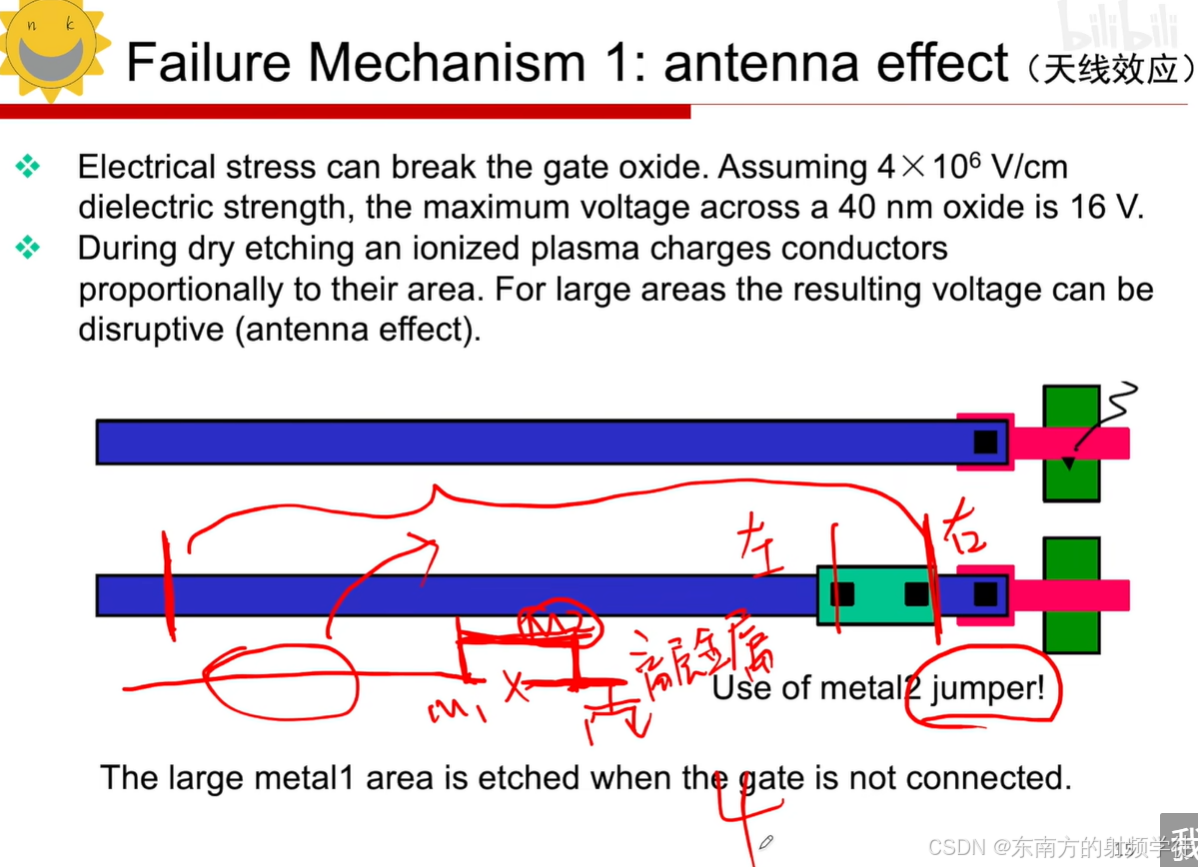

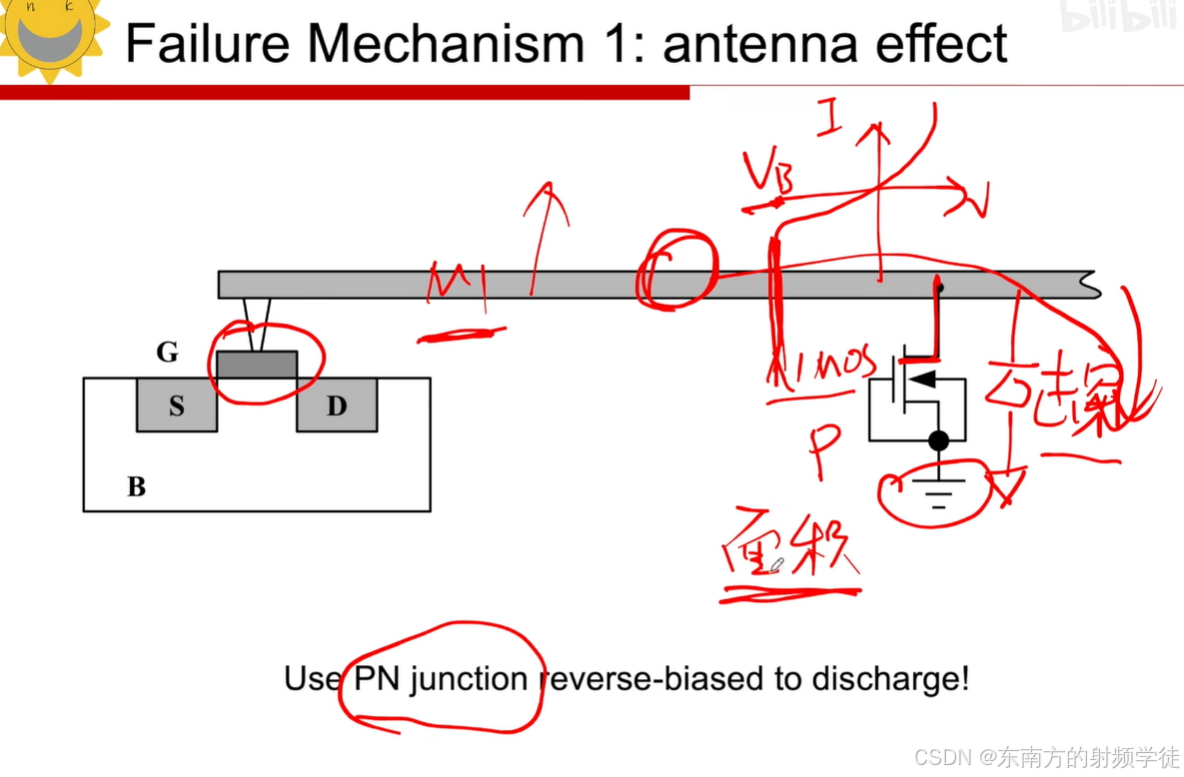

1. 天线效应(antenna effect)

- 首先在右侧绘制了一个mosfet,红色是栅极gate,绿颜色是源漏区,然后通过黑色正方形的contact连接到蓝色的M1上,但是这条金属线M1画的特别长,或者说面积特别大。这样会导致的现象时,当我们去加工的时候,在刻蚀的过程中会有等离子体(带电粒子)被金属所吸收,意味着这个金属线就会有一个电压,当这个电压比较高的时候,如果超过了一定的阈值,就会超过gate所能承受的电场强度。

- 假设其承受的最高电场强度为4E6V/cm,一旦超过了这个值,栅氧就会被击穿,所承受的电压应力太大了,如果栅氧是40nm厚度,那么承受的电压应力就是16v,超过了这个值,栅氧就会被击穿,那么器件在加工过程中就已经失效了。

- 前期设计的时候一定要规避gate的互连金属线特别长的情况,有的工艺DRC会单独检查天线效应的文件。

- 如果就是想给gate的金属互连线很长,有两种方法

- 第一种是跳线(jumper),一定是往高层次去跳线(与加工顺序相关),在临近栅极的位置将M1给切断,这样就会导致左边的M1和右边的M1是没有连接的,然后通过M2的桥接,把信号给连接上。

- 这是因为,在加工过程中,一旦把M1加工完刻蚀之后,需要通过一些手段把整个芯片上的金属电荷给引出来的,导出之后金属上的电压就降下来了;然后再去加工下一层金属,再去吸收下一层金属引起的电荷

- 左侧的M1金属线会很长,这些位置会吸收大量的电荷,这些位置电压的上升,并不会直接连到gate上,因为中间是断开的没有连接,不会对gate产生影响。而直接连接到gate上的金属又特别的短,其引起的电压上升又不足以引起gate被击穿。所以一定要在临近gate的地方将其切断。

- 当我们加工完M1之后,M1层金属线上的电荷会通过某种手段给他释放掉,这样M1的电压就会降下来,又变成了零。

- 然后再加工M2,其也会吸收电荷,但是M2的跳线(jumper)特别的短,它所吸收的电荷会特别的少,也不会引起gate的击穿。通过这样的方式,把天线效应给解决掉了。

- 如果是顶层金属M4有问题了,特别长,这就要借助另一种办法,加入PN结

- 第二种方法,加入PN结,在M1金属线上连接一个反偏的二极管(阳极接地,阴极接M1上),实际上是用mos管的源极或者是漏极代替这样的PN结,比如用nmos的漏端接到金属线上,栅极衬底都接到地上,其漏端是N型,衬底是P型,漏和衬底之间就是会存在有寄生的PN结。

- 这里使用到了PN结的击穿特性。当M1金属线积累大量电荷,电压急剧上升。由于金属线上还连接有PN结,其反偏电压特别大,达到击穿电压Vbreak时候,电流就会激增,导线上积累的大量正电荷都会被PN结给释放掉到地,降低了金属线上的电压,保护了栅氧,相当于加了一个保护器件,通过其可以将大量的电荷引导出去。

- 但是这对于二极管的面积是有一定要求的,当金属线的面积特别大的时候,二极管的面积也要有相应的提升才可以。

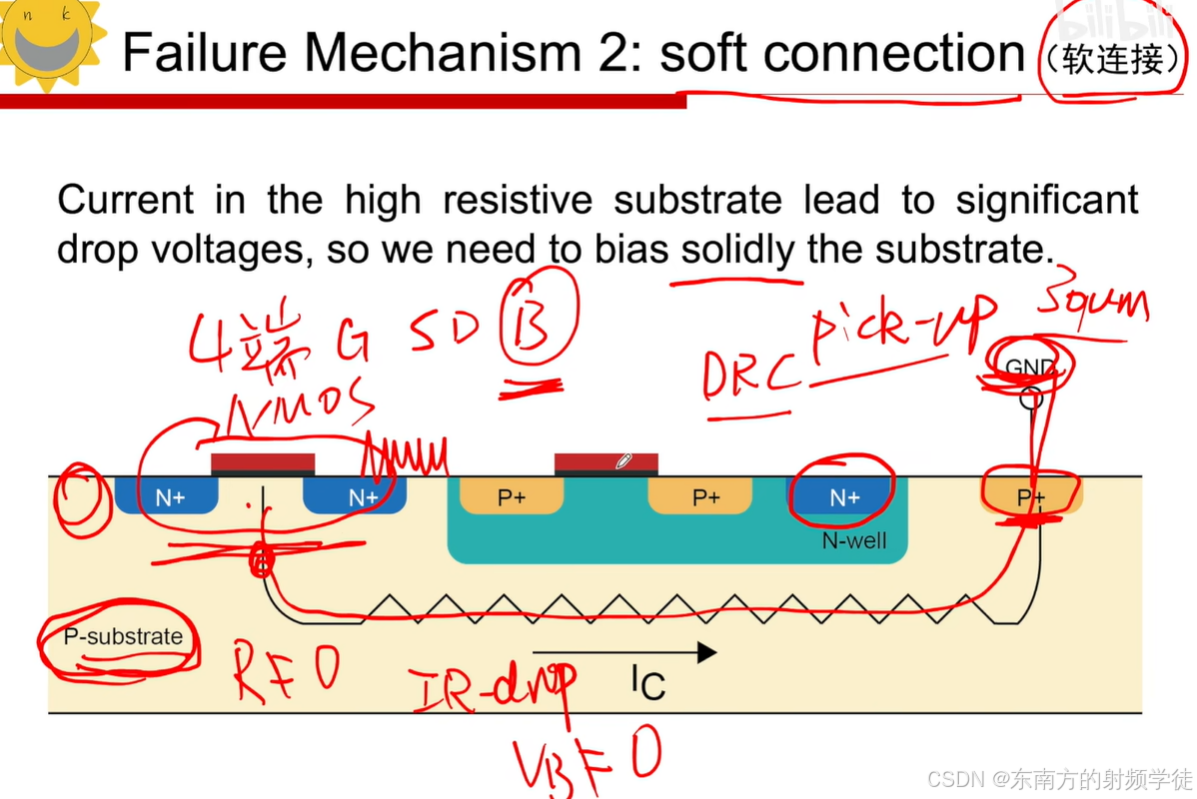

2. 软连接(soft connection)

- MOS管是四端口器件(G\B\S\D),在画mos管的版图的时候,往往会忽略衬底的存在,忘记画衬底接触端口,就会出现软连接

- 假如一个nmos画好了源漏栅极,但是旁边没有画衬底接触(衬底是Psub),而在其他位置上可能会有衬底接触,理想情况下好像整个衬底都偏置到了零(地)上了,但实际上不代表其他位置上的衬底都是零电位,因为衬底的电阻并不是理想的零,是有一定的寄生电阻的,这个电位由于IR drop的问题,衬底也不会处处等于零电位,只有在明确接了衬底接触的位置,其电位才会是零,其他位置的电位有可能会发生变化。

- 比如mos管作为反相器,频繁的进行开关的动作,就会对衬底注入一个瞬间的电流,这个电流肯定会顺着衬底流向最低电位零上,但由于衬底位置上有寄生电阻,所以衬底的电压就不等于零了,甚至有可能会波动起来,因为电流是非恒定的,会有抖动,流过电阻就会产生抖动的电压。

- 这就会造成衬底的电位上升,同时电位来回的波动,干扰器件的工作

- 这种现象就是软连接,即看似连接上了,但是连接的并不可靠,很软。所以我们要对器件进行solidly connect实连接,即画了mos管之后,在其附近一定要有一个可靠的衬底接触。

- 这个软连接的问题DRC是可以做检查的,一般会说明在一个器件多少um以内,一定要有一个pick-up

- N-well也会有这样的问题,需要做一个N+的接触。所以PMOS附近一定要有N+的注入

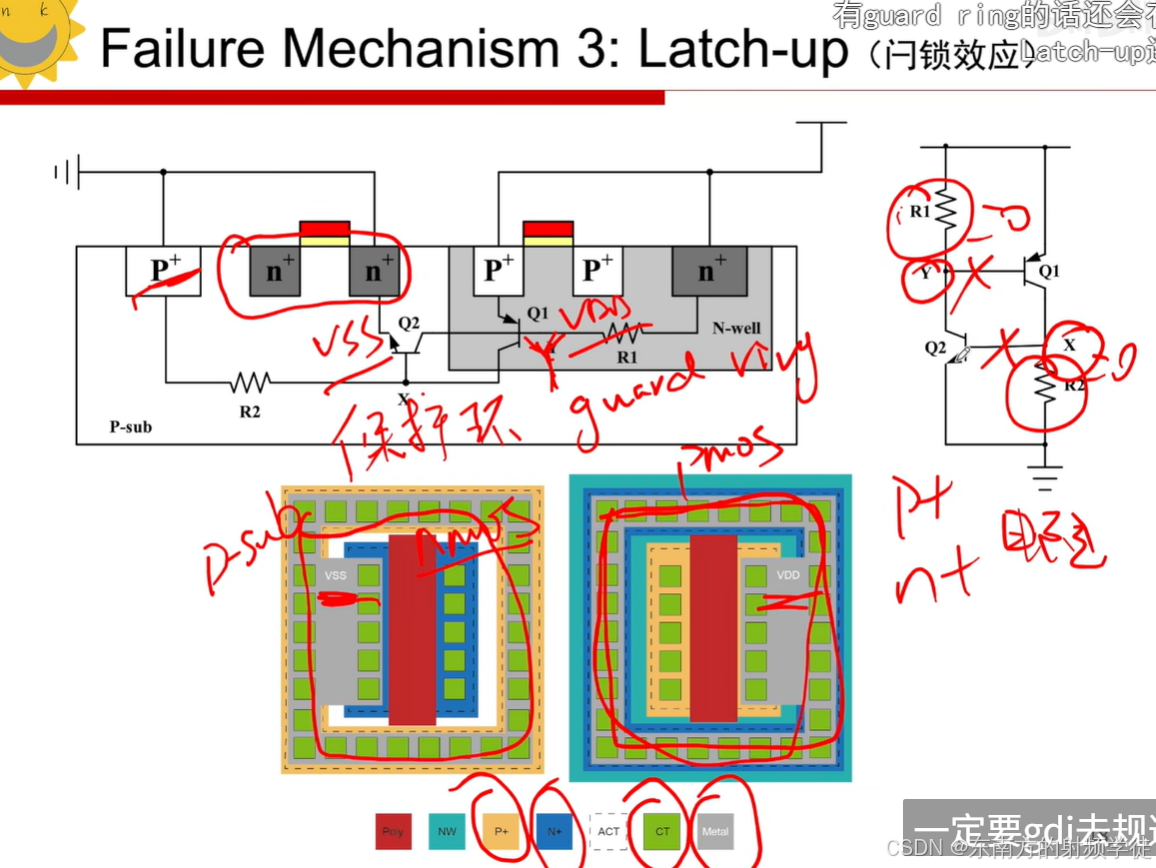

3.闩锁效应(latch-up)

- 这个效应通常会出现在,绘制了nmos和pmos且尺寸非常大的情况下。

- 最典型的情况就是反相器。特别大的反相器可以用来做buffer缓冲器,即缓冲一个数字信号的时候,比如负载特别大的时候,需要一个尺寸特别大的输出电流能力特别强的反相器(宽长比较大)。

- 这种设计如果不是很可靠的话,就会出现latch-up。一旦出现这种现象,会导致的后果很严重,会导致这个器件甚至芯片直接被烧毁了

- 首先在p衬底左边绘制了nmos,右边绘制了pmos,这两个器件会形成寄生结构,其电路图如右图所示。

- R1是电源连接到Y点,其是N阱的寄生电阻,是从N+接触注入,一直连接到PMOS的核心区域上

- P+与n阱与衬底形成了PNP的三极管(Q1)结构,基极就是Y点,发射极是连接到电源,集电极是P衬底。

- P衬底连接到P+的接触端,还会有寄生电阻R2,

- N+与n阱与衬底形成NPN结构的三极管(Q2),其基极就是衬底X,发射极连接到源极S上,也就是地。

- 如果nmos和pmos挨得很近,就会形成这样的寄生结构。

- 如果衬底没有任何电流的话,这个寄生结构不会工作。

- 而如果在工作的时候,信号剧烈跳动,就会对衬底注入电流,衬底一旦流过寄生电阻,导致右图中的电路图的X点电位上升,Q2管的基极电压上升,导致VBE在上升,使Q2管开启,就会在集电极上流过电流,导致R1有电流流过,就会产生IR drop,导致Y点电压下降,Q1管的基极电压就会低于VDD,导致Q1管导通,Q1的集电极也会出现电流。这些电流会在X点汇合在一起,加剧R2上的电流,使得X点电压上升。这个过程是一个正反馈的过程,不停地加强电流,最终导致无论是R1还是R2的电流都会特别大,表示电源到地会有一个通路短路了,等效电阻会非常小。

- 一旦短路电流比较大的时候,有可能会导致器件烧毁。

- 有两种方法可以规避这种效应

- 第一种是降低R1和R2。因为R1和R2闩锁效应的开启条件,如果R1和R2都等于0,那么就不会有开启,无论如何注入,X点都是稳定的0v,Y永远是VDD,这样Q1和Q2永远都开启不了(最主要的采用方式)

- 工艺上会通过外延的方式,将R1和R2的电阻率降低一些,使得寄生电阻比较小。

- 通常不会发生latch-up的问题,但可能器件特别大,注入的电流特别大,仍然会导致其开启。

- 第二种方式是降低Q1和Q2的放大倍数,这是跟工艺相关的

- 第一种是降低R1和R2。因为R1和R2闩锁效应的开启条件,如果R1和R2都等于0,那么就不会有开启,无论如何注入,X点都是稳定的0v,Y永远是VDD,这样Q1和Q2永远都开启不了(最主要的采用方式)

- 从版图设计的角度来说,避免latch-up,就是要加guarding保护环

- 如左下图为nmos器件,右下图为pmos器件。

- 将nmos用衬底接触(psub)围成一圈(P+),pmos也是一样,用衬底接触围成一圈(N+)。加上后还要加上一圈金属metal(M1),并且需要通过contact(ct)等间距的铺开。目的是让这些衬底接触都有可靠的电位连接。因为P+和N+本身也是有电阻的,如果单纯靠自身去供给电源和地的话,自身会形成压降。这样意味着nmos器件周围都是P+注入,连接到GND上,pmos器件周围都是N+注入,连接到VDD上了。一旦有电流注入,立马就会有VSS和VDD给吸收掉了

- 所以我们在画比较大的nmos和pmos同时出现的时候,一定要用guardring去规避latchup的问题。

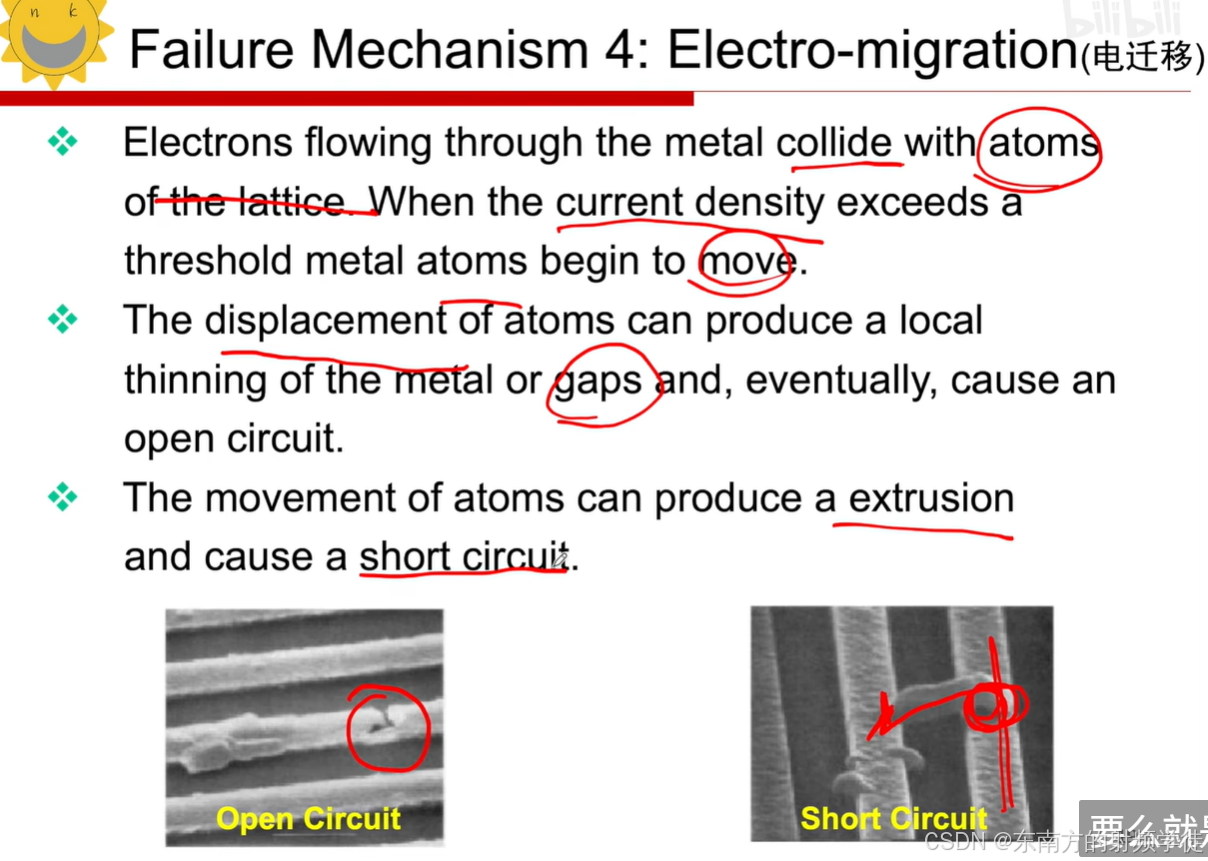

4. 电迁移(Electro-migration)

- 电迁移就是,金属线里面流过的电流特别大,出现了烧断或者短路现象。

- 电流(电子的流动)过金属会撞击金属的原子,当电流较小的时候,撞击不会很严重,不会对原子产生显著的影响。一旦电流密度(current density)超过了一定的阈值,电流特别强,就会使得金属的原子发生移动。

- 这种移动有可能会使原子的丢失(displacement),(原本存在的金属原子会被高速运动的离子撞击走,导致这个位置的原子没了),没了之后会导致金属出现gap(空隙),当空隙足够大的时候,就会出现断路(open circuit)

- 还有一种可能,原子被撞走之后,就会跑到别的位置上,就可能出现原子的堆积挤出(extrusion),然后就可能会和旁边的金属线出现交叠,最后导致短路(short circuit)

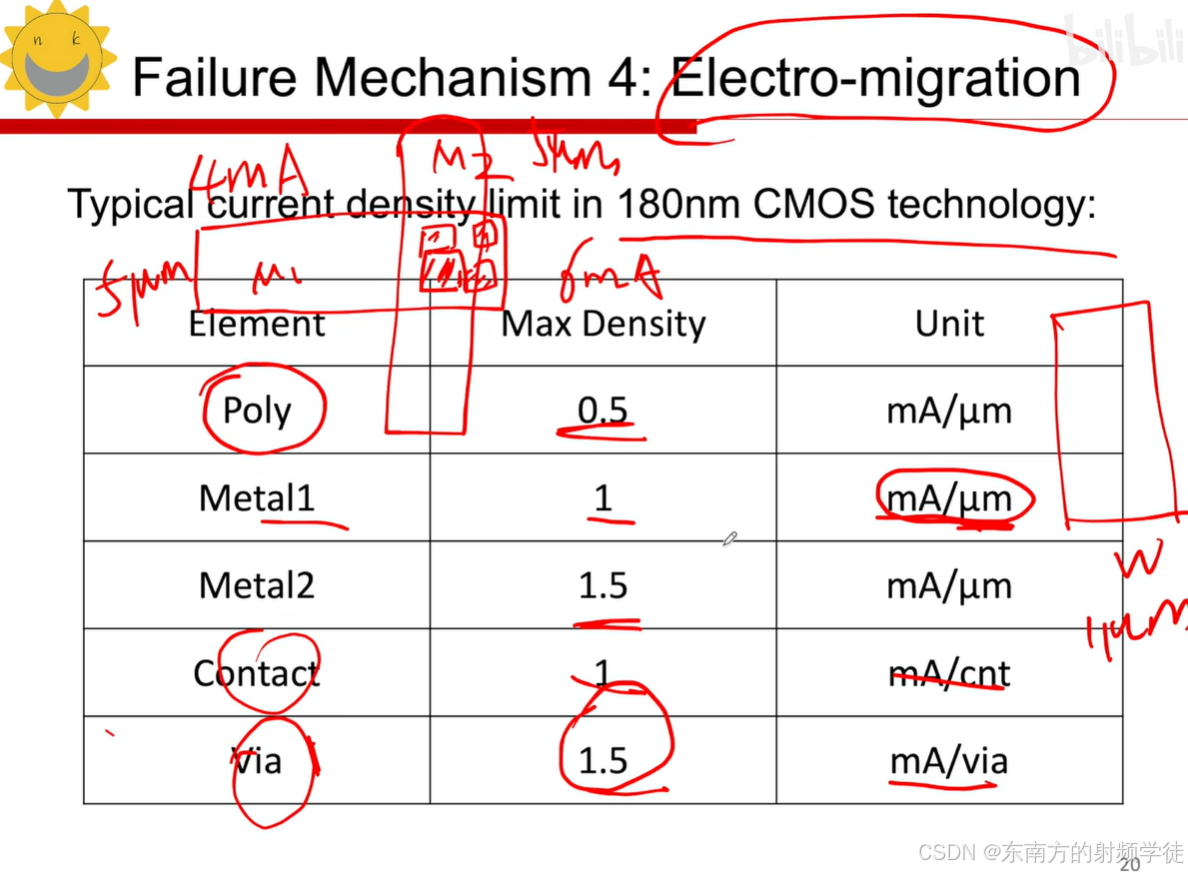

- 所以我们在设计版图的时候,要清楚这些互连线和通孔能够承受的电流密度是多少,要考虑走线的时候走过的电流大小,再去考虑能否承受这么大的电流。

- 我们只需要看单位宽度的电流密度即可,一般层次越高的金属所能承受的电流密度越宽一些,因为其厚度会变厚。所以一般会用顶层金属去做总的电源线,来去做top metal,用它去供电会比较可靠。

- 对于contact,是按照个数去计算的,每个contact所能承载的电流。

- 此外还要注意,不要按照极限去设计,比如4mA的电流,M1就画4um,这样的可靠性不是很高,电路的工作寿命也会有所降低。所以要预留一些余量。

高频大电流

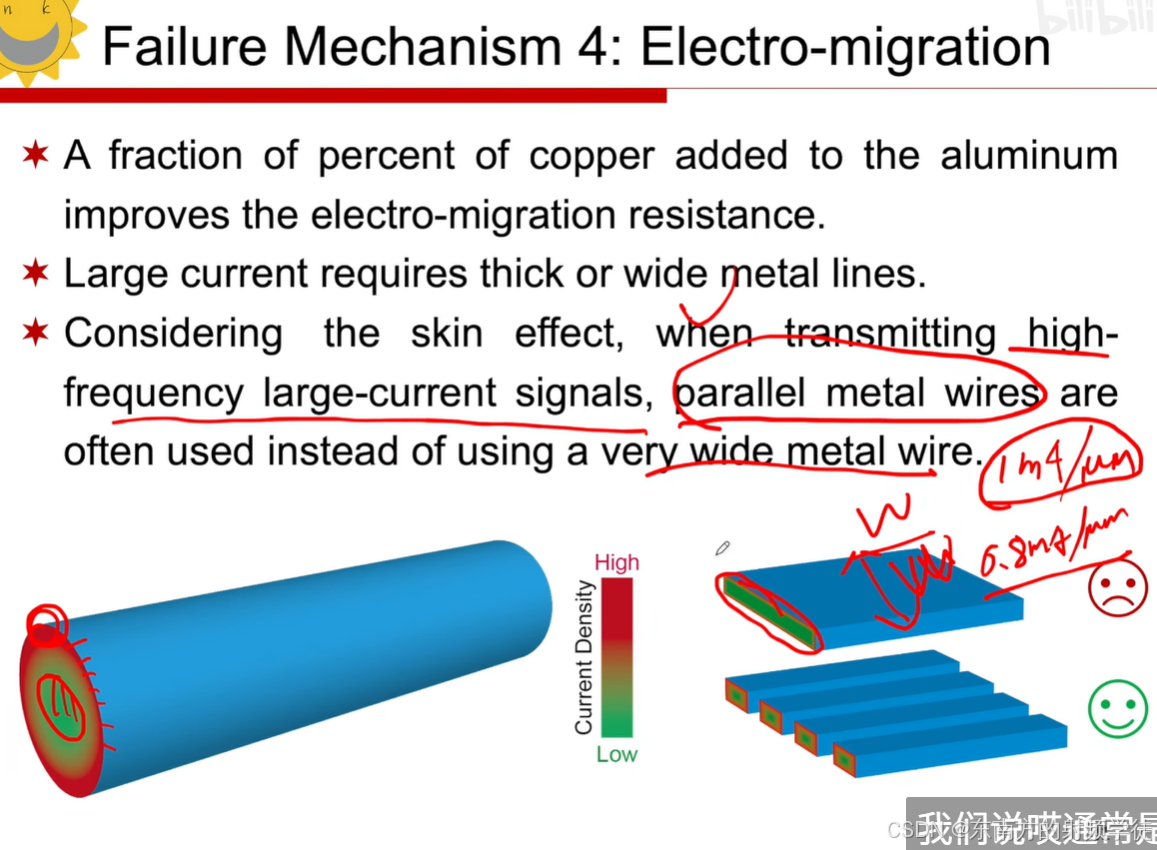

- 解决电迁移的办法就是加宽线的宽度,实际上在工艺上也会有一些办法。比如在铝制品里面去加一些铜的话,其电迁移的问题就会得到很大的改善,因为铜能够承受的电流密度要比铝要大一些。

- 对于版图设计来说,能够改变的只有宽度和厚度,在走大电流的时候,要有足够宽的金属和足够厚的金属

- 对于宽度,比如1mA的电流走2um的线宽。

- 对于厚度,我们可以采用并联的方式。比如我们要传递10mA的电流,要走12um的线,但是发现版图空间上画不下12um,由于布局的问题。我们就可以采用并联的方式,从立体的形式解决,先画6um线宽的M1,再画6um线宽的M2,中间用Via1连接在一起,两根金属线并联在一起,相当于导线的厚度加强了。假如M1能承受1mA电流密度,M2能承受1.5mA的电流密度,那么它们并联的走就可以承受2.5mA的电流密度。

- 趋肤效应,在传递高频大电流信号的时候,通常用大量的并联导线,而不是用比较宽的金属线。这可以是不同层次的并联,也可以同一层次的并联,把它拆开成若干条。

- 如果用一个很粗的金属线去传递高频信号的话,由于趋肤效应的存在,电流往往会集中在金属表面处,金属边缘的密度会非常大,而中心区域的电流密度非常低,也就是电流基本在金属表面去传递,而中心区域基本没用上。这样虽然截面积非常大,但是能够有效利用的界面并没有那么大,这种线会影响金属线的传递效果,还是很容易烧断。一旦出现趋肤效应,所能承受的单位宽度下的电流密度在下降。

- 可以把宽的金属,拆成若干条宽度较小的金属线,就可以缓解趋肤效应带来的电流密度问题。

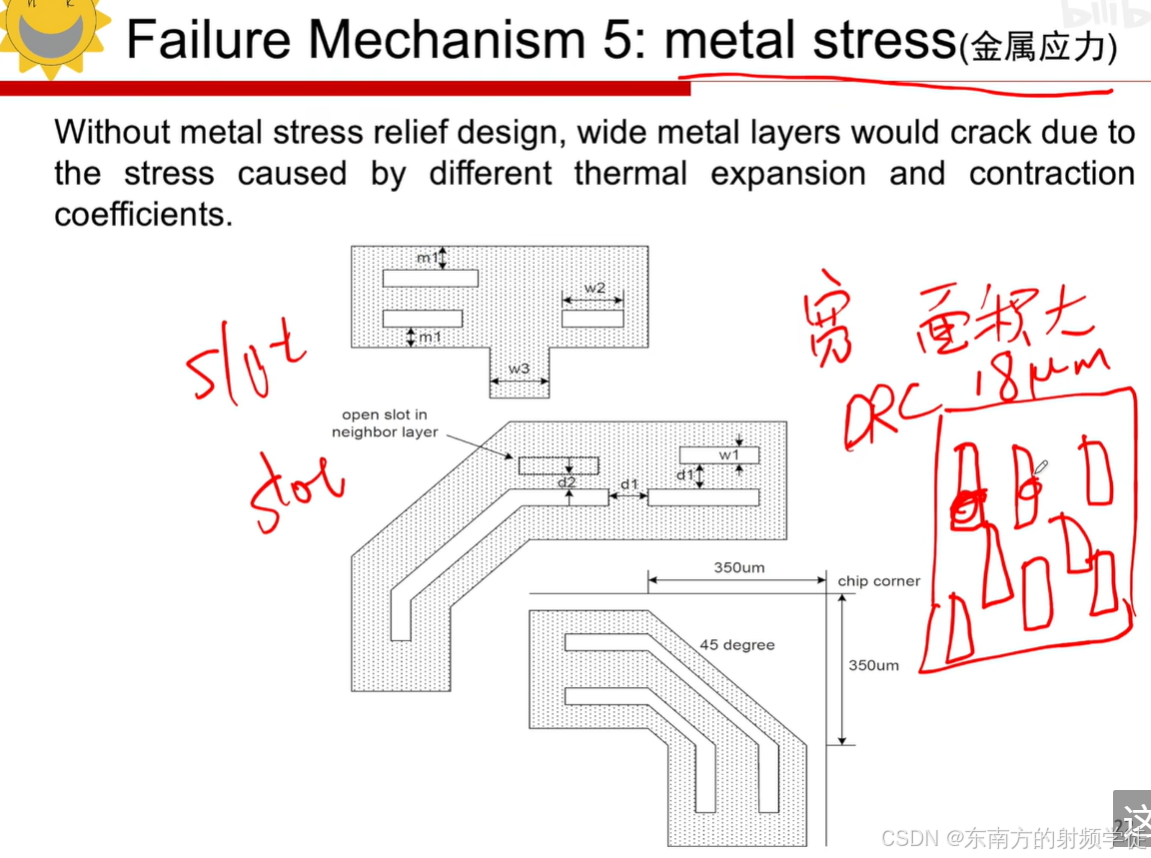

5. metal stress(金属应力)

- 当我们在画特别宽面积特别大的金属,尤其是在做电源供给线的时候,金属线会画的非常宽,因为要考虑电流密度的问题。

- 但实际上加工出来的是一个薄板金属片,这么大的薄金属片覆盖在硅上,由于加工过程中会出现各种温度的变化,还有各种的材料,不同材料之间热胀冷缩的系数是不一样的,会不停地出现拉伸压缩,这样就会对金属产生拉拽的影响,会导致金属出现被扯断或者褶皱的现象,即金属会承受一定的应力,导致金属出现断路或短路的问题。

- 为了避免出现这种问题,对于比较宽的金属要打成一些slot(狭缝),这样特别宽的金属会做的跟金属网似的(很多空洞),不同工艺的打洞方式会有不同的要求(design rule会有说明),这样大面积的金属做DRC的时候会被检查出来(比如说金属超过一定宽度了,就要打slot)

- 金属片打出的slot,就是给金属留出了一定的变形空间,无论是拉伸还是压缩,会缓解金属的应力,避免出现断路或者短路的问题

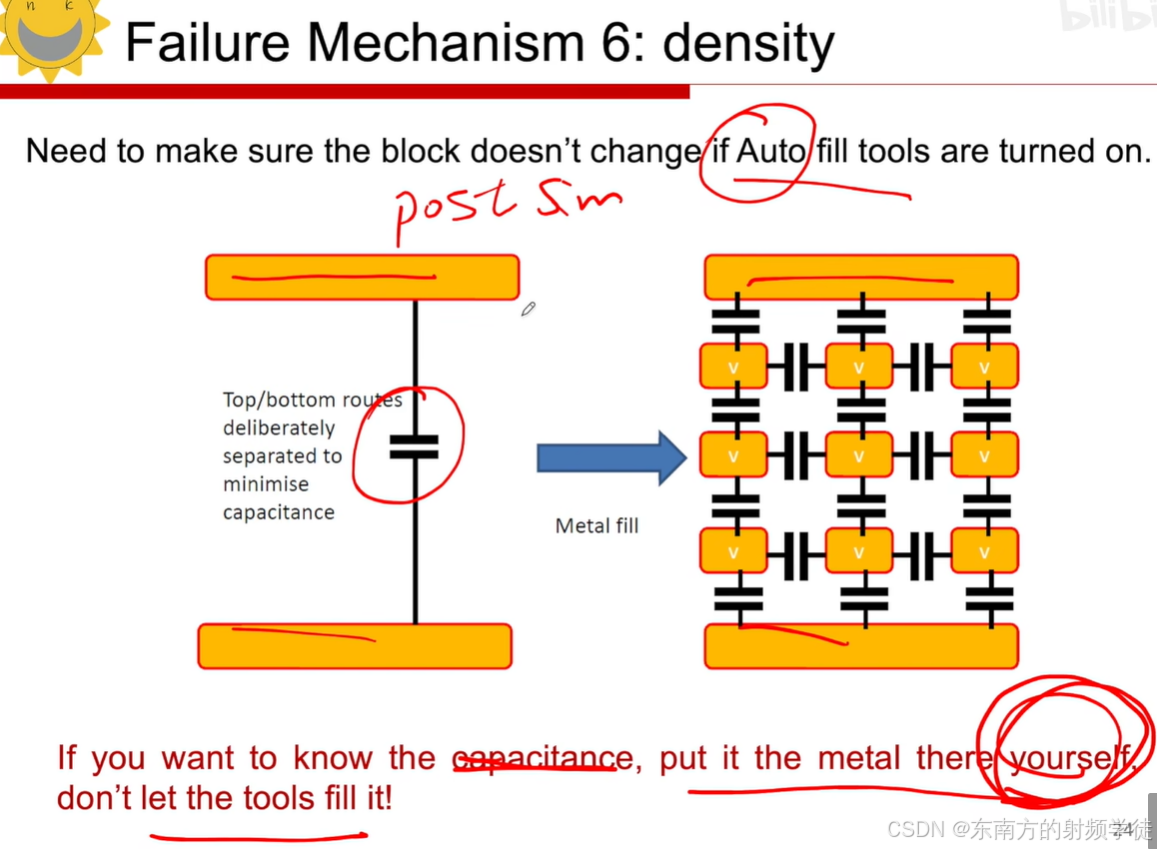

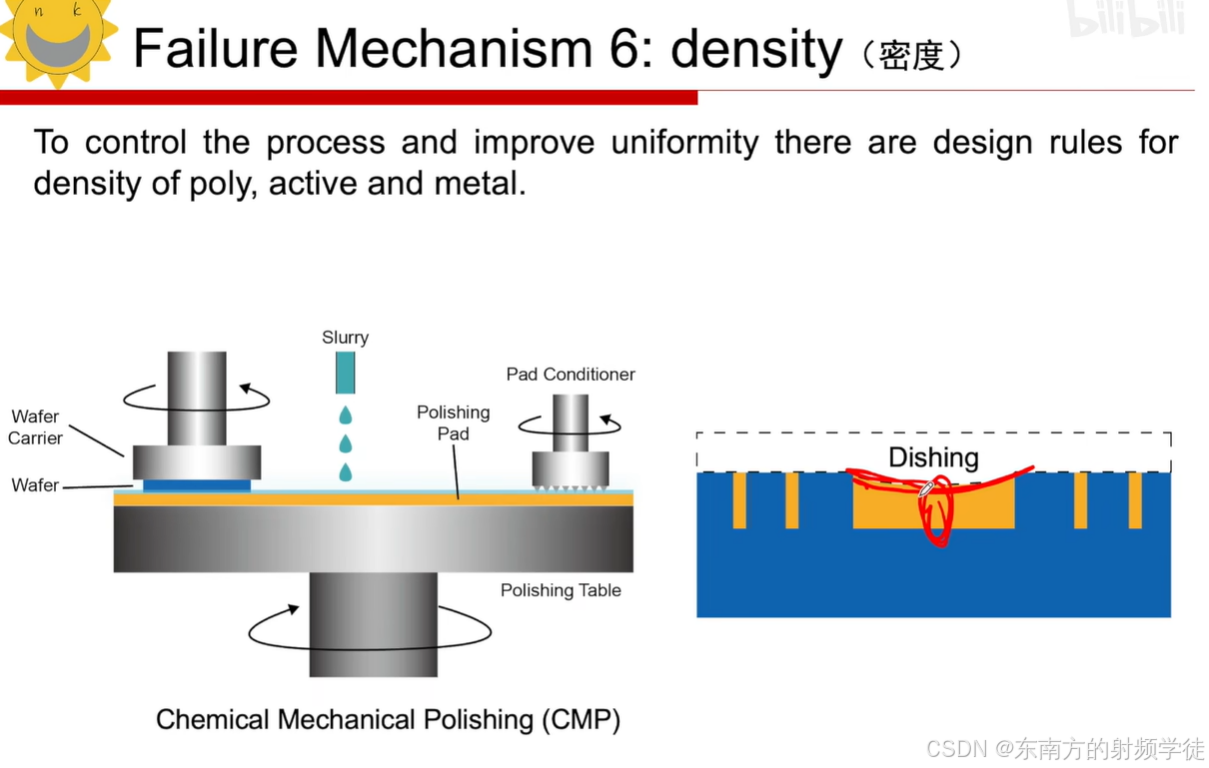

6. 密度(density)

- 为了保证工艺的一致性,design rule里面一般都会要求poly,有源区,金属层达到一定的密度要求。

- 这是因为在工艺过程中,使用到一个化学机械抛光(CMP)的工艺,这是一个平整化的过程,就是把表面给磨平,无论是STI还是金属做好之后,都是会给金属表面做平整化的过程,即化学机械抛光。

- 如左图所示,会有一个转盘,通过真空的方式将wafer吸附在下面的吸盘上,然后下面会有抛光垫,垫子上会放抛光液(slurry),这样就会不停的磨wafer表面,

- 但是在磨的过程中会出现一个问题,即不同材料的硬度是不一样的,二氧化硅会比硅要硬,而金属是最软的,那么抛光机在磨的速度也是不一样的,金属多的地方磨的比较快。

- 这样会出现dising(凹陷)问题,由于金属磨的比较多,在金属区会形成小盘子凹进去了,更严重一点可能会把金属区给磨断

- 所以才要有一定的密度要求,金属的覆盖的密度一定要很均匀,密度要足够高,到处都有这样的金属,整体磨起来速度才会比较均匀。无论对于金属,还是有源区还是poly都会存在这样的问题,导致一致性变差,甚至会出现失效的问题。

- 如何避免这样的问题?我们要让各个层次的密度比较均匀。

- 比如在画版图的时候,两条同层金属线的距离比较大,中间空的比较多,没有金属。

- 工艺产会提供Auto fill的工具去给你自动填充,会计算中间空的比较多的区域金属密度不够,空间很富裕,会用比较小的金属方块把中间都填充上金属,这样就解决了密度的问题。

- 但是要注意,假如了这些补充的方块后,寄生的环境就会发生变化。原先两个金属线的距离是比较远的,寄生电容会比较小,但是贴了这么多金属之后,这些填充金属会和正常导线之间都会存在着大量的寄生电容,使得整个寄生环境变得复杂了,就会影响电路的特性,所以一定要注意填充的电容,对于关键位置最好是自己去填充,而不要用工具去填充。填充完之后一定要做后仿真来验证填充的金属是否影响电路的性能。