同步数字通信总线传统上依赖于与信号调制和最大似然采样相关的两个基本原则。简而言之,数字信息传输始于用数据比特表示信息,然后将这些比特编码为电压势或电子电流等物理量。此类物理量通过金属导体或自由空间等物理介质传输。类似地,在接收数据比特时,接收器需对感测到的物理量进行量化,并在噪声、衰减和干扰存在时最小化量化误差的概率。

多导体传输解决方案的通用化

在计算机、消费电子设备或数据中心服务器等数字子系统中,编码过程传统上几乎完全依赖于两电平脉冲幅度调制(PAM)方案,而接收器采样则常采用正反馈锁存器(用于量化)结合同步时钟信号实现最大似然采样。例如,逻辑1比特用高电压编码,逻辑0比特用低电压编码。自集成电路发明以来,这一基础方案已衍生出多种变体,包括利用差分电压信号实现抗电磁干扰和接地反弹、通过数字字编码实现直流平衡和基线漂移防护,以及基于锁相环(PLL)的前向时钟和嵌入式时钟技术以减少引脚数量或降低误码率。

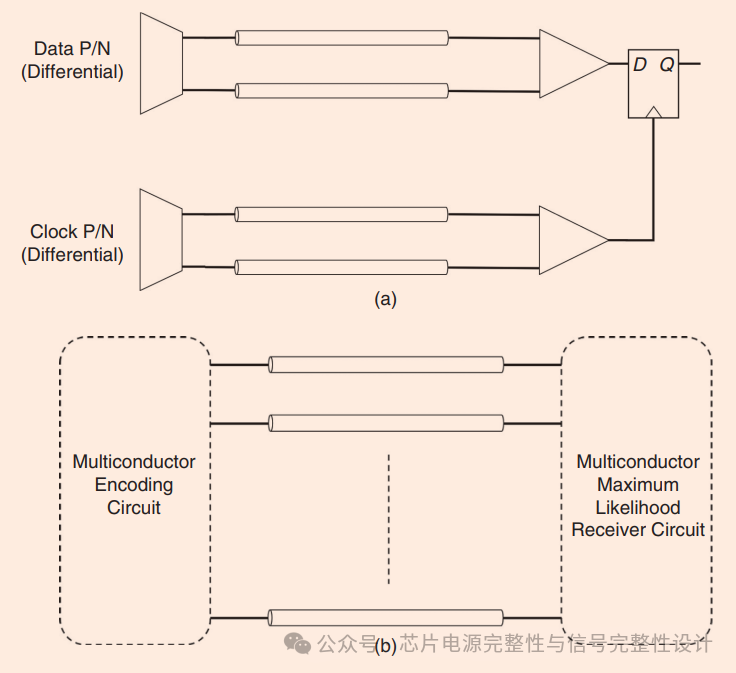

接下来将介绍MIPI C-PHY接口标准,这是一种部署于智能手机、虚拟现实/增强现实头显和物联网设备等高速低功耗应用场景的新型同步数字通信总线。C-PHY标准通过通用化多导体传输方案,在单位时间间隔(UI)内通过单根物理导体传输更多数据比特,从而与传统数字总线形成显著差异。如图1(a)所示,典型数字通信链路包含用于编码传输数字比特的差分数据缓冲器和用于编码时序同步信号的差分时钟缓冲器。接收器通过时钟缓冲器的同步信号触发D触发器对数据比特进行采样。这种架构需使用四根独立导体(线缆)在单个UI内仅传输1比特数据。

图1: C-PHY 多导体传输解决方案 (a)典型的数字通信链路。(b)广义多导体传输解决方案。

C-PHY接口通过扩展图1(a)的前向时钟差分对架构,从根本上解决了线缆数量的低效问题。正如差分对利用两根线缆协同编码逻辑比特对应的物理量,C-PHY标准探索使用一组线缆(超过两根)协同编码/传输每UI超过1比特的数据。此抽象概念如图1(b)所示,称之为通用多导体传输解决方案。

在此通用化过程中,C-PHY接口采用了混合单端/差分信号方案和多电平信号调制等创新方法,与传统两电平差分电压调制架构显著不同。此外,其多相编码技术消除了前向时钟传输需求,进一步减少线缆数量。本文将从三相编码原理出发,逐步阐述驱动电路实现、接收器电路设计、时钟恢复机制,以及C-PHY的高层映射技术及其协议灵活性。

三相编码

作为其底层多相通信技术的首个实际应用,C-PHY通过三根线缆实现三相编码传输系统。在此系统中,三根线缆协同工作以创建同步数据链路,实现约2.3比特/UI的吞吐量。这已较传统差分数据链路的1比特/UI效率大幅提升,且使用更少线缆(三根而非四根)。

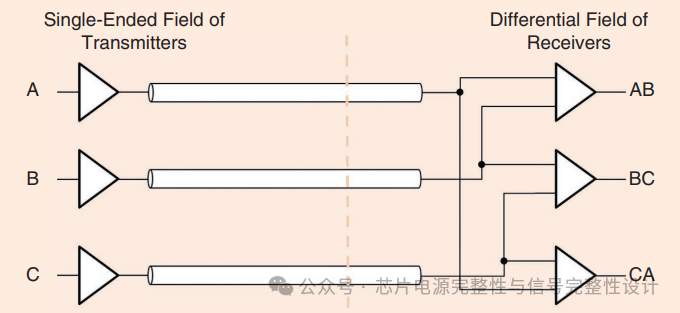

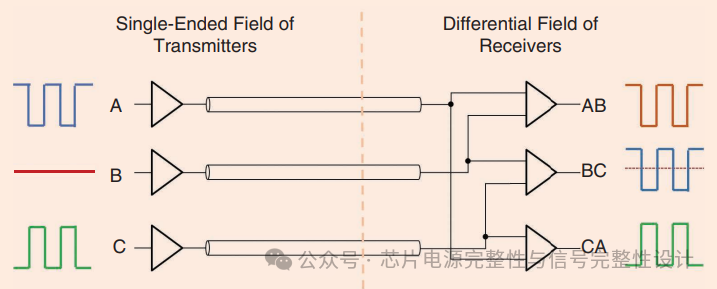

图2展示了三相编码C-PHY链路的电路示意图。C-PHY总线在发送端为单端结构,在接收端则为全差分结构。具体而言,发送端使用三个单端相位匹配驱动器调制传输介质(三根独立线缆)的电压势;接收端则由三个二进制差分放大器组成(术语“三线组”用于指代C-PHY中的通道,类似于差分通道中的P和N线对)。这些放大器的工作方式与图1(a)中的传统差分放大器相同,使得C-PHY能够继承传统系统的优异共模噪声抑制能力。

图2:三相编码链路中的发送器和接收器电路。

为使用常规二进制差分接收放大器,需在C-PHY链路的发送端应用编码规则。例如,若图2中的A和B驱动器在同一时间产生相同电压势,则对应的差分接收器(AB)将输出不确定值,由其输入参考偏移电压、驱动器间电压失配以及接收器中差分放大器/比较器的亚稳态行为共同决定。显然,C-PHY的首要编码规则是:任意UI内,两根线缆的电压势不得相同。此规则通过允许每个单端驱动器生成三电平调制(而非传统数字链路的两电平)实现。

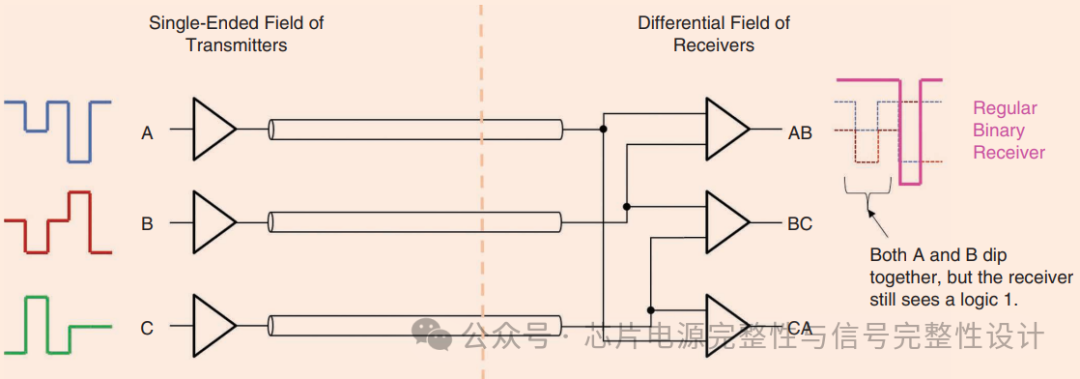

利用单端驱动器的这一通用化设计,可确保交叉连接的差分放大器永远不会看到不确定的差分电平。图3展示了示例:随着时间推移和数据被编码为调制电平,A、B和C驱动器的电压势始终保持不同。在图中左侧的第一个UI中,A处于高电平,B处于中电平,C处于低电平;在下一个UI中,A切换至中电平,但B切换至低电平,C切换至高电平,从而确保三根线缆的电压势始终不同步。

图3:从发射机到接收机缓冲区的三相单端调制转换为差分二进制调制。

在示波器上观察时,单端驱动器波形如图4所示。每根线缆在三个不同电平间切换,且仅在切换期间可能出现相同电压。三根线缆的瞬时平均电压始终名义恒定,此现象与差分信号中P和N线平均电压恒定的特性一致。此外,三根线缆的跳变相位/偏移严格匹配,这对C-PHY的正常运行至关重要,类似于传统SerDes链路中差分对的相位匹配要求。

图4:在发射机上看到的信号波形

观察图3右侧的差分放大器波形可得出关键结论:尽管每对差分放大器的输入线缆可能同时下降(如AB放大器所示),但其差值始终为有限正值或负值。图中显示的少数UI中,A和B线频繁切换,但量化后的差分波形(粗品红色)仅在其差值由正转负时发生一次跳变。

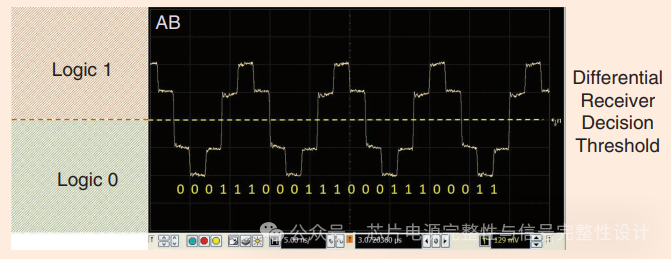

在示波器上观察时,C-PHY差分接收器输入波形如图5所示。该图展示了与图4模式对应的AB接收器波形。单端线缆的三电平在差分波形中转换为四电平,分别表示逻辑0和逻辑1的弱版本与强版本。最终,二进制差分接收器仅识别逻辑0或逻辑1。弱版本和强版本的逻辑0/1是三电平编码的产物(参见“注”关于C-PHY中多电平波形的讨论)。

图5:接收机看到的信号波形

驱动电路实现

作为高速通信链路,C-PHY需驱动电长传输线(即信号传播延迟超过上升时间),因此驱动器设计需考虑阻抗匹配和均衡。同时,C-PHY链路针对极低功耗应用优化,电路实现通常采用电压模式驱动器而非电流模式驱动器。业内共识是,电压模式驱动器通常具有低功耗和小尺寸的优势。

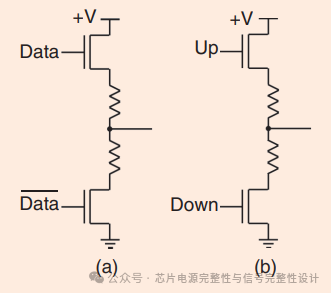

差分电压模式驱动器的单侧结构由一对晶体管、一对端接电阻和一个稳压电源轨构成(图6(a))。图中展示的是简单NMOS实现,但任何电压模式实现(无论是NMOS还是CMOS)均适用。类似地,端接电阻的构造方式不做限定,仅需强调驱动器的功能行为及其如何转换为C-PHY驱动器。具体而言,在差分电压模式驱动器中,上拉和下拉晶体管以互补方式驱动:若差分对的正侧半驱动器被数据位上拉,则负侧半驱动器被同一数据位下拉;同时,正侧被数据位的补码下拉,负侧被补码上拉。此配置产生真正平衡的互补差分对行为:当P输出编码高电平时,N输出同时编码低电平。单个预驱动器需生成单个数据位及其补码。而C-PHY预驱动器则向电压模式缓冲器发送两个独立比特(图6(b))。这两个比特可编码高、低或中电平,除此之外,C-PHY驱动器与差分驱动器的单侧结构完全相同。

图6:(a)差压模式驱动器 (b)三相编码三极管

然而,驱动中电平在C-PHY中提出了特殊挑战:电压模式驱动器是否需要主动驱动中电平(强制线缆电位)或让线缆浮空,从一阶分析看,无需主动驱动中电平,仅需浮空线缆(断开驱动器的上下晶体管)。原因是C-PHY要求接收端对传输线进行端接匹配以最小化反射,而接收端端接可确保生成中电平。更精确地说,前文描述的线缆编码机制保证:浮空驱动器的上下晶体管时,线缆将处于由A和B线端接电阻(RL)组合产生的中间电位。然而,浮空上下晶体管无法提供适当的反向端接匹配,可能导致实际系统中的严重回波损耗。因此,在高速应用中,主动驱动中电平始终更优。

关于端接与信号走线的说明

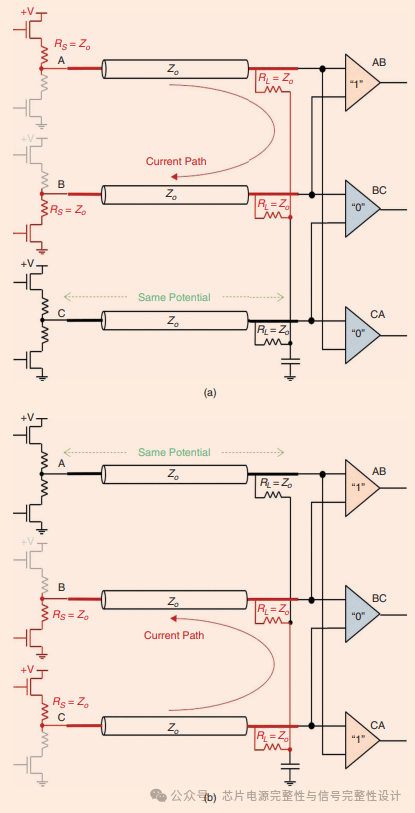

前文提到,C-PHY的线缆编码机制确保三根线缆的平均电平恒定,但未解释其电路实现原理或为何允许驱动器在中电平时浮空。本节通过图7阐述该主题。图7(a)展示了当A线拉高、B线拉低时,可假设此线对作为常规差分对工作。若每根线缆以等于传输线特性阻抗和驱动器源阻抗的浮空负载电阻(RL)端接,则可观察到两线缆端接电阻之间的中点将稳定至两线缆平均的共模电压(名义为+V/2)。此中点称为三线组的公共点。无论C线的上下晶体管是否驱动中电平,只要晶体管和电阻参数名义匹配,线缆上均无直流电流流动。

图7:传输线末端的负载电路,(a) a被拉高,B被拉低,C为中电平,(b) a为中电平,B被拉低,C被拉高时,信号电平如何在直流意义上平均为一个恒定值。

具体而言,若上下晶体管浮空,则驱动器侧无直流路径,线缆电位将由A和B线端接电阻RL共同拉至中间电位。类似地,若上下晶体管被驱动至中电平,则此电位将与A和B线RL电阻设定的电位相等,从而在一阶近似下无直流电流。从直流角度看,公共点端接与三线组平均电压恒定的三相编码方案一致。图7(b)展示了B线拉低、C线拉高时的驱动场景,可同理验证。

关于交流端接,如前所述,C-PHY需驱动电长传输线,因此需应用电磁波传播理论。每个单端驱动器的切换事件会沿传输线传播电磁波,其交流端接(反射抑制)需通过在公共点添加解耦/端接电容实现。该电容为入射波提供虚拟交流接地,吸收能量并防止其通过三线组反射回源端。

由于每个驱动器发送独立边沿且传输线通常以非耦合方式布线,此端接方案等效于单端通信链路。边沿在驱动器切换任意电平(低、中、高)时产生,因此C-PHY传输线边沿的幅度不一定相等(例如低→中与低→高)。

自时钟与时钟恢复

前文介绍了C-PHY信号发送及传输线端接电路。就接收器而言,仅描述了等同于传统差分对接收放大器的缓冲器设计。本节将阐述发送器与接收器电路的同步机制,详述接收路径和时钟恢复结构。

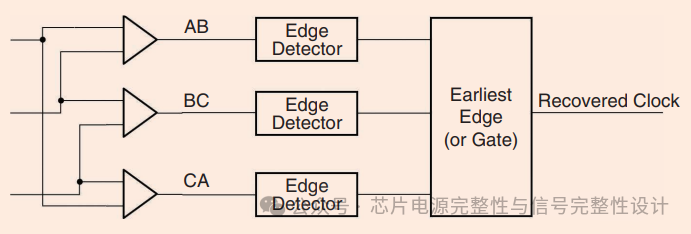

C-PHY的第二项关键信号规则启用了时钟恢复,其启发性描述如图8所示。简而言之,C-PHY编码器确保每个时钟周期内至少一个接收放大器检测到跳变,即使个别线缆长期保持稳定。例如,图8中B线可能保持恒定,但C-PHY要求互补线缆处于不同电平,且每个UI内至少发生一次跳变,因此至少一个接收器会在每个UI检测到边沿(图8右侧)。图中所有接收器在每个UI均显示边沿,但这仅是左侧条件的特例。一般而言,仅需一个差分放大器在每个UI产生边沿。

图8:在其中一根导线上具有恒定值的信号波形

此跳变要求使C-PHY无需复杂或高功耗的锁相环即可实现时钟恢复。链路通过UI边界处的强制跳变实现自时钟,接收器利用这些跳变恢复时钟。同时,恢复的时钟及数据采样电路需立即响应数据流中的跳变,采用负保持时间采样技术。

图9展示了C-PHY时钟数据恢复电路的功能示意图。每个放大器可能产生或不产生边沿,但均配备边沿检测电路。三个边沿检测输出中的首个被选为当前UI的采样时钟,驱动常规D触发器。需注意:边沿检测功能需谨慎设计。边沿检测器必然包含有限延迟,这会限制可采样的最小眼图宽度。若延迟过长,则可能导致边沿检测器和后续时钟门控单元采样错误眼图。这可能是C-PHY在成本敏感应用中大规模部署的最大挑战之一。

图9:C-PHY中时钟恢复电路

C-PHY字映射

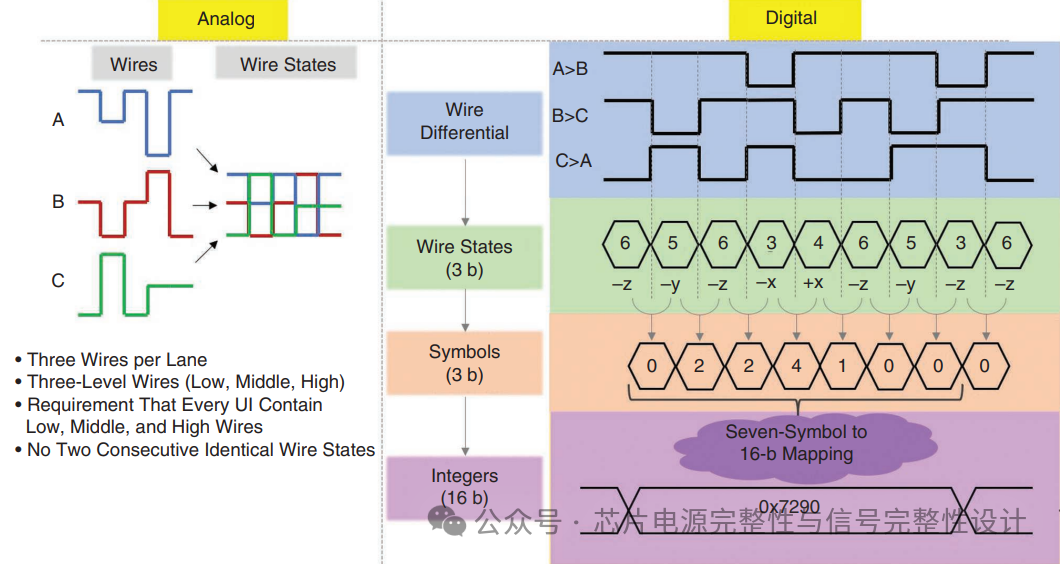

在不深入C-PHY协议层的情况下,理解三线组在每个UI传输的多比特符号如何转换为下游或上游逻辑可用的数字数据是有益的。为此,线缆状态定义为A、B、C三根线缆的电平组合。前文规则(任意UI内无两根线缆电平相同)意味着仅存在六种唯一线缆状态。类似地,每UI必须发生线缆状态跳变的规则意味着当前线缆状态需切换至其他五种状态之一。符号定义为线缆状态间的跳变,因此每个UI编码五种可能的符号之一。图10以摘要形式展示了这些概念。橙色面板(倒数第二层)表示数据传输,显示数据仅在状态跳变时传输。数据以符号而非比特传输,因为单个符号编码超过1比特信息(类似于PAM4中单个符号代表2比特)。

图10:C-PHY数据类型的总结。线路状态用数字1到6表示;符号是连接状态之间的转换,每个UI有五个可能的符号值;7个唯一符号的空间超过了16b的空间,可以完全表示一个16b的单词。

映射任务即将符号转换为数字字。为此,C-PHY采用一种字映射范式:每七个符号映射至唯一的16比特数字字。这意味着C-PHY可传输的字数量为5^7=78,125种,而16比特字包含65,536种组合,因此七个符号可完整表示16比特字。图10底层面板展示了将16比特字映射为七个符号的原理。实际实现中,这本质上是65,536个数字的一对一映射,因此每个符号编码约2.3(16/7)比特信息。

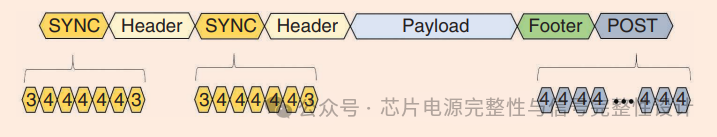

C-PHY存在大量未映射的七符号组合(78,125-65,536=12,589),这为协议层提供了独特机会。例如,传统SerDes链路因时序不确定性需使用对齐标记界定字和包边界,而C-PHY可通过发送未映射的七符号字(如SYNC头3444443)实现无歧义对齐(图11)。此类未映射字不表示任何16比特数字,可在数据流中随时发送。

图11:未映射的符号序列可用于在同一线路上传输边带消息

未映射字进一步支持通过同一组线缆传输边带信号。传统协议通常依赖I2C或SPI等额外总线实现控制或中断处理,但会增加引脚数量。C-PHY的未映射字允许在不影响主数据包传输的前提下发送边带消息,目前部分低功耗移动应用已利用此特性减少额外引脚需求。

结论

本文对C-PHY信号标准——一种通过多电平信号支持约2.3比特/UI信息量的新型多导体解决方案进行了介绍,其在受限传输通道中实现了高数据带宽效率。三相编码概念、电路实现技术、时钟恢复机制及高层映射要求(包括利用未映射字实现边带信令)均被详细阐述。C-PHY代表了一类突破传统信号模式的新型数字总线,通过结合单端与差分信号优势,在保持低引脚数的同时不牺牲抗电磁噪声能力。