1.嵌入式系统基础概述

嵌入式系统是以应用为中心、以计算机技术为基础,软硬件可裁剪的专用计算机系统。它会根据用户对功能、体积、可靠性等需求进行定制。

从组成来看,软件层面包含系统软件(如操作系统)和应用软件;硬件基本构成有运算器、控制器、存储器、输入设备、输出设备。

在嵌入式行业,存在多种核心处理单元:

- MPU(微处理器):偏向处理复杂任务,像高端嵌入式设备的核心计算。

- MCU(微控制器):集成了处理器、存储器等,常用于单片机类简单控制场景。

- DSP(数字信号处理器):专为高度复杂数学运算设计,在音频、图像处理等领域广泛应用。

- SoC(片上系统):是一个集成化的概念,将 MPU、MCU、GPU、DSP 等多种功能模块集成在一块芯片上,如同一个功能完备的 “城市”,让设备实现更丰富的功能且更小型化。

2.处理器架构与指令集

1.CISC 与 RISC 指令集

- CISC(复杂指令集计算机):指令集庞大且复杂,试图用一条指令完成多种操作,硬件结构复杂,指令执行周期长,但能实现丰富的功能。

- RISC(精简指令集计算机):选取使用频率高的简单指令,指令格式规整,每条指令可在一个时钟周期内完成,硬件实现相对简单,执行效率高,ARM、RISC - V 等架构采用这种指令集。

2.ARM 内核版本与系列:

- 核心架构版本:ARM1 - ARM11、ARM - A、ARM - R、ARM - M。

- 指令集版本:V1 - V9。

- 内核系列:Cortex - A(MPU,面向高性能应用)、Cortex - R(Realtime,实时应用)、Cortex - M(MCU,微控制器应用)。

3.冯・诺依曼与哈佛架构

1.冯・诺依曼架构中,程序指令和数据存放在同一存储空间,共享数据总线,取指令和取数据会产生冲突,执行效率受限,但结构简单、成本低。

2.哈佛架构则将程序存储器和数据存储器分开,有独立的指令总线和数据总线,可并行处理指令和数据,执行效率更高,适用于高速数据处理场景。ARM 内核既支持冯・诺依曼架构,也支持哈佛架构,部分高性能 ARM 内核(如 Cortex - A 系列)采用哈佛架构以提升性能。

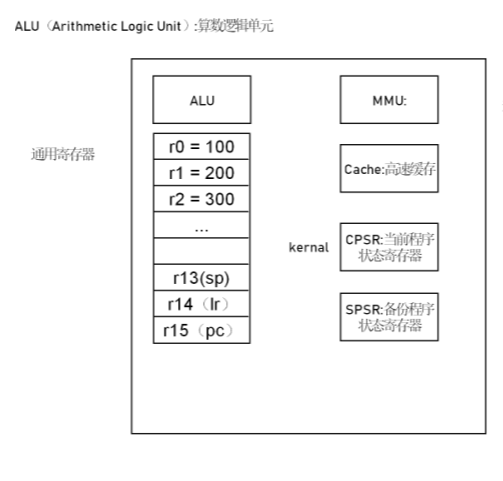

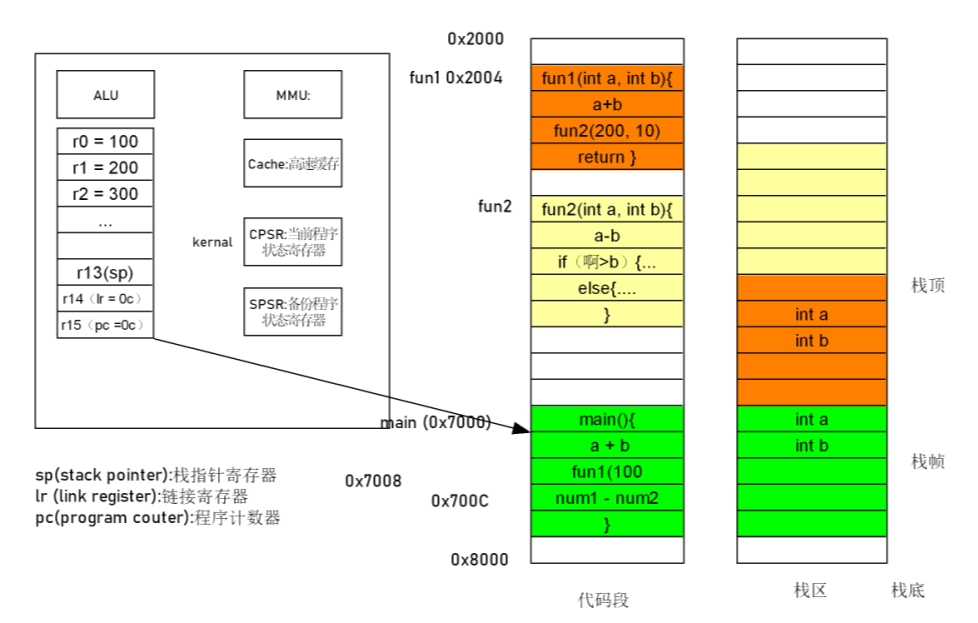

3.ALU 与寄存器

ALU(Arithmetic Logic Unit,算术逻辑单元):负责执行算术运算(如加、减、乘、除)和逻辑运算(如与、或、非、异或)。

- 通用寄存器:图中示例有 r0、r1、r2 等,用于暂存数据,如 r0 = 100、r1 = 200 等。

- 特殊寄存器:<三个寄存器配合使用>

- r13(sp):栈指针寄存器,指向栈顶,用于存储数据保护现场。

- r14(lr):链接寄存器,保存函数返回地址。

- r15(pc):程序计数器,存储下一条要执行的指令地址。

- 状态寄存器:

- CPSR(Current Program Status Register,当前程序状态寄存器):保存当前程序运行的状态信息,如标志位等。

- SPSR(Saved Program Status Register,备份程序状态寄存器):在异常发生时,用于备份 CPSR 的内容。

4.内存管理与缓存

- MMU(Memory Management Unit,内存管理单元):负责虚拟地址到物理地址的转换,实现内存保护、地址映射等功能。

- Cache(高速缓存):分为 data cache(数据缓存)和 instruction cache(指令缓存),用于缓存常用数据和指令,提高访问速度,且可控制其开启或关闭。

5.总线架构

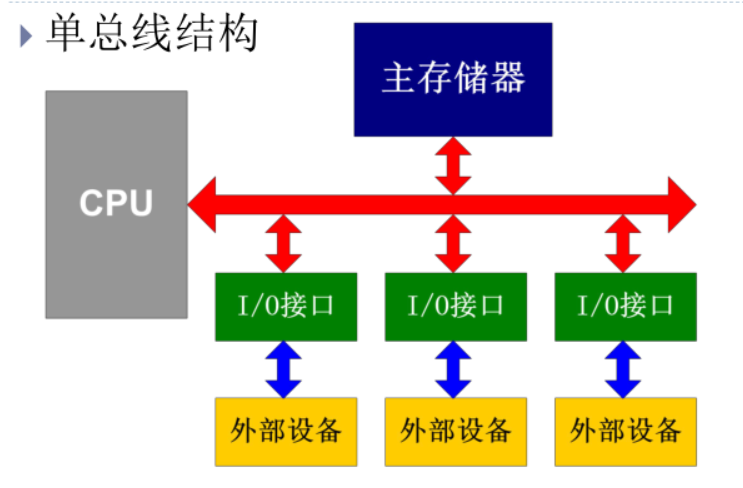

- 单总线:所有设备共享一条总线,结构简单但传输效率低,易产生冲突,示例:

int a = 100; int b = 200; a = a + b - c;可体现单总线在数据传输时的串行性。

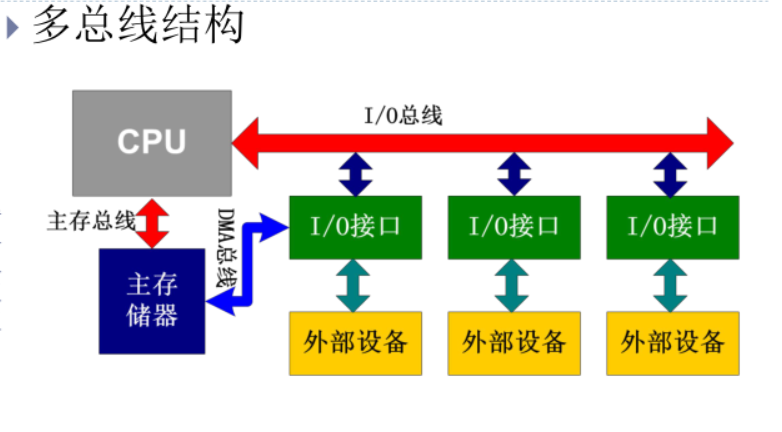

- 多总线(AHB、APB):

- AHB(Advanced High - performance Bus,高级高性能总线):用于高性能、高带宽的模块间通信,如 CPU 与内存、高性能外设之间。

- APB(Advanced Peripheral Bus,高级外围总线):用于低速外围设备通信,如 GPIO、timer、Uart 等外设。

注:图中IO总线就属于APB,主存总线属于AHB

6.ARM 开发相关

1.典型芯片与开发板

ARM920T、S3C2440A、ARM - Cortex - A7、ARMv7(如正点原子 IMX6ULL - Mini 开发板)

2.交叉编译工具链

因为嵌入式设备的处理器架构(如 ARM)与开发主机(如 x86 架构的 PC)不同,需要交叉编译器将代码编译成目标架构可执行的程序。

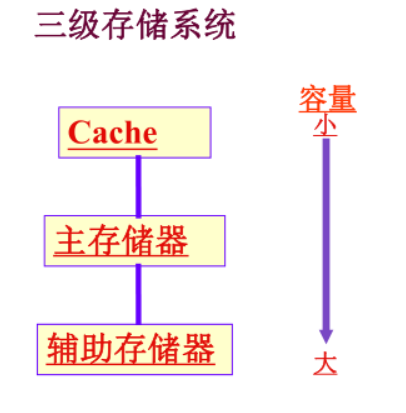

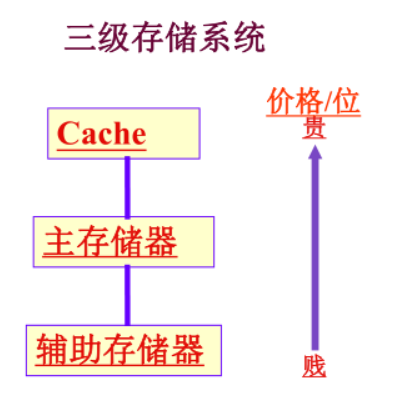

3.三级存储系统

主存储器:可由CPU直接访问,用来存放当前正在执行的程序和数据

辅助存储器:设置在主机外部,CPU不能直接访问,用来存放暂时不参与运行的程序和数据,需要时再传送到主存

高速缓冲存储器(Cache):CPU可以直接访问,用来存放当前正在执行的程序中的活跃部分,以便快速地向CPU提供指令和数据

4.控制器:流水线技术

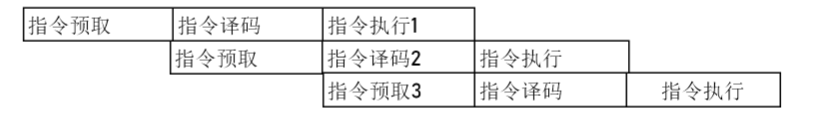

采用三级流水线(指令预取、指令译码、指令执行),使指令的不同阶段重叠进行,提高指令执行的吞吐量,示例中展示了多条指令在流水线中并行处理的情况。

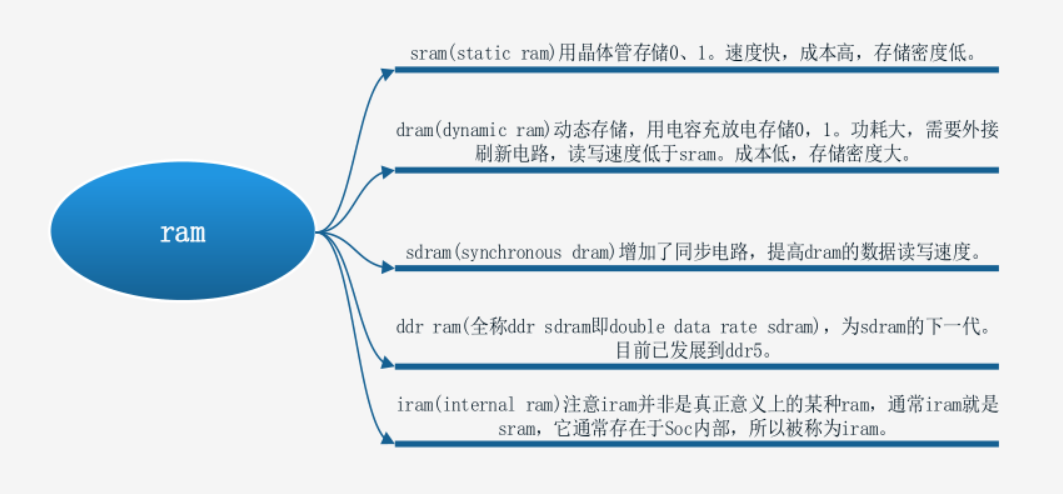

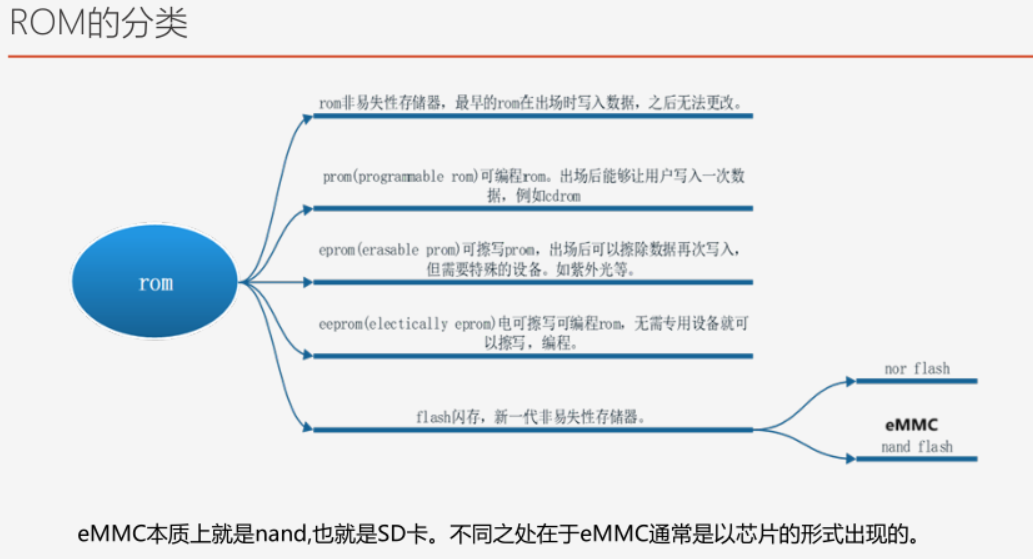

5.ram和rom