计算机内核分为

CISC: complex istruction set computer(复杂指令集)成本高,体积大,功耗大 产生2 8效应,在80%情况下只能有到20%的功能。(x86)

RISC:reduced istruction set computer 功能少,功耗下降,便携(ARM)

ARM先是ARM1,ARM2 ARM3.。。。。。到ARM11后分类变为

A Application(应用领域)

M Mircr(微控制领域)

R Real time(实时领域)

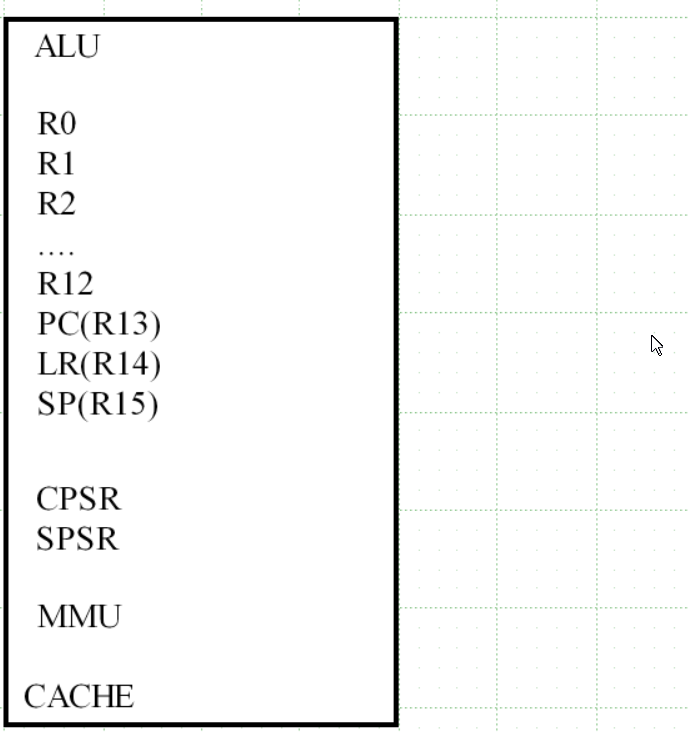

ALU(算数存储单元)负责执行加减、与或等运算,运算数据需先加载到通用寄存器中。

ARM通用寄存器:R0-R12十三个存储器,用来存储数据

PC program counter(程序寄存器)指向下一条指令的地址 (R15) ,

LR Link rigister(链接寄存器)(R14)

SP(stack pointer) 为了保证每个lr能被保存(R13)

CPSR当前程序状态寄存器

SPSR(备份状态寄存器)

MMU 内存管理单元 虚拟内存,提高物理内存的使用效率,实现虚拟内存到物理内存的映射,提高物理内存使用效率,是运行操作系统的必要硬件支持。

CACHE 高速缓存

冯诺依曼结构:把数据和指令打包放在一起

哈弗架构:把数据和指令分开来放

打开 instuction cache

关闭 data cache

ram:容易失性存储器

rom:非容易失性存储器(flash)

nor flash 每个数据都可以被寻址

设置不同模式下的站寄存器

ARM里面有37个寄存器

3.ARM有7个基本工作模式

User:非特权模式,大部分任务执行在这种模式

FIQ :当一个高优先级(fast)中断产生时将会进入这种模式

IRO:当一个低优先级(normal)中断产生时将会进入这种模式

Supervisor:当复位或软中断指令执行时将会进入这种模式

Abort:当存取异常时将会进入这种模式

Undef:当执行未定义指令时会进入这种模式

System:使用和User模式相同寄存器集的特权模式

Cortex-A特有模式:

Monitor:是为了安全而扩展出的用于执行安全监控代码的模式:也是一种特权模式

当异常产生时,ARM内核会做哪些工作?

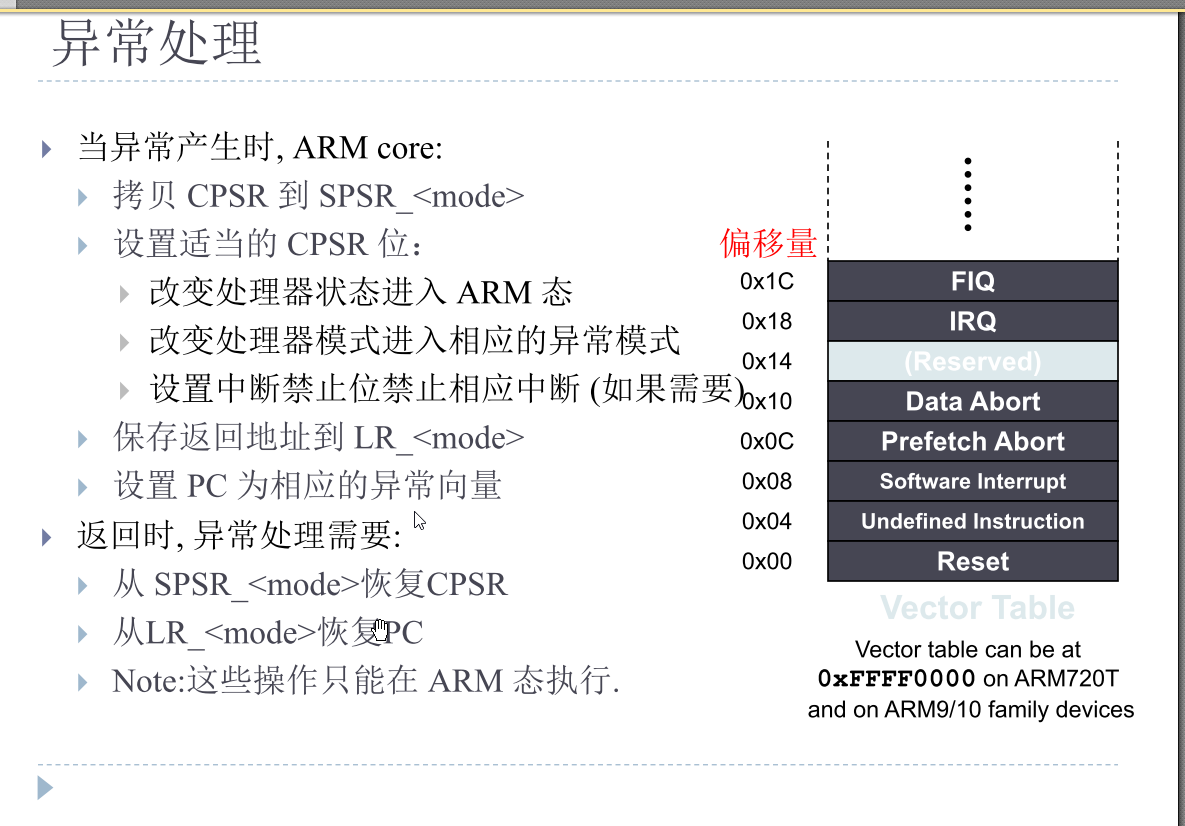

当异常产生时,ARM core:

拷贝CPSR到SPSR <mode>,

设置适当的 CPSR 位:

改变处理器状态进入 ARM 态

改变处理器模式进入相应的异常模式

设置中断禁止位禁止相应中断(如果需要)

保存返回地址到 LR<mode>

设置 PC为相应的异常向量

返回时,异常处理需要:

从SPSR <mode>恢复CPSR

从LR<mode>恢复PC

note:这些操作只能在 ARM 态执行。如图有7个异常

当处理器执行在ARM状态:

所有指令 32 bits 宽

所有指令必须 word 对齐

所以 pc值由bits[31:2]决定,bits[1:0]未定义(所以指令不能halfword /byte对齐).

当处理器执行在Thumb状态:

所有指令 16 bits 宽.

所有指令必须 halfword 对齐

所以 pc值由bits[31:1]决定,bits[0]未定义(所以指令不能 byte对齐).

当处理器执行在Jazelle状态:,

所有指令8bits 宽

处理器执行 word 存取一次取4条指令

复位以后ARM处理器出于复位异常状态

ROM 分类与演进

- 只读存储器(ROM)出厂时数据已固化,仅支持读取操作,典型代表为CD-ROM。

- 可编程ROM(PROM)允许用户一次性写入数据,常用于光盘刻录等场景,写入后不可更改。

- 可擦除可编程ROM(EPROM)支持紫外线照射擦除,实现重复编程,但擦除过程不便。

- 电可擦除可编程ROM(EEPROM)通过电信号完成擦写,操作便捷,广泛应用于家电设备中存储配置信息。

- 闪存(Flash)成为主流大容量非易失性存储技术,分为NOR Flash和NAND Flash两类:NOR Flash支持字节级寻址,适合代码执行;NAND Flash以块为单位读写,容量大、成本低,用于硬盘、SD卡等存储介质。