一、6ULL的GPIO使用

上一章我们编写了基于设备树的 LED 驱动,但是驱动的本质还是没变,都是配置 LED 灯所使用的 GPIO 寄存器,驱动开发方式和裸机基本没啥区别。 Linux 是一个庞大而完善的系统,尤其是驱动框架,像 GPIO 这种最基本的驱动不可能采用“原始”的裸机驱动开发方式,否则就相当于你买了一辆车,结果每天推着车去上班。 Linux 内核提供了 pinctrl 和 gpio 子系统用于GPIO 驱动,本章我们就来学习一下如何借助 pinctrl 和 gpio 子系统来简化 GPIO 驱动开发。

45.1 pinctrl 子系统

45.1.1 pinctrl 子系统简介

Linux 驱动讲究驱动分离与分层, pinctrl 和 gpio 子系统就是驱动分离与分层思想下的产物,驱动分离与分层其实就是按照面向对象编程的设计思想而设计的设备驱动框架,关于驱动的分离与分层我们后面会讲。本来 pinctrl 和 gpio 子系统应该放到驱动分离与分层章节后面讲解,但是不管什么外设驱动, GPIO 驱动基本都是必须的,而 pinctrl 和 gpio 子系统又是 GPIO 驱动必须使用的,所以就将 pintrcl 和 gpio 子系统这一章节提前了。

我们先来回顾一下上一章是怎么初始化 LED 灯所使用的 GPIO,步骤如下:

①、修改设备树,添加相应的节点,节点里面重点是设置 reg 属性, reg 属性包括了 GPIO相关寄存器。

② 、 获 取 reg 属 性 中 IOMUXC_SW_MUX_CTL_PAD_GPIO1_IO03 和(IOMUXC_SW_PAD_CTL_PAD_GPIO1_IO03 这两个寄存器地址,并且初始化这两个寄存器,这两个寄存器用于设置 GPIO1_IO03 这个 PIN 的复用功能、上下拉、速度等。

③、在②里面将 GPIO1_IO03 这个 PIN 复用为了 GPIO 功能,因此需要设置 GPIO1_IO03这个 GPIO 相关的寄存器,也就是 GPIO1_DR 和 GPIO1_GDIR 这两个寄存器。

总结一下,②中完成对 GPIO1_IO03 这个 PIN 的初始化,设置这个 PIN 的复用功能、上下拉等,比如将 GPIO_IO03 这个 PIN 设置为 GPIO 功能。③中完成对 GPIO 的初始化,设置 GPIO为输入/输出等。如果使用过 STM32 的话应该都记得, STM32 也是要先设置某个 PIN 的复用功能、速度、上下拉等,然后再设置 PIN 所对应的 GPIO。其实对于大多数的 32 位 SOC 而言,引脚的设置基本都是这两方面,因此 Linux 内核针对 PIN 的配置推出了 pinctrl 子系统,对于 GPIO的配置推出了 gpio 子系统。本节我们来学习 pinctrl 子系统,下一节再学习 gpio 子系统。

大多数 SOC 的 pin 都是支持复用的,比如 I.MX6ULL 的 GPIO1_IO03 既可以作为普通的GPIO 使用,也可以作为 I2C1 的 SDA 等等。此外我们还需要配置 pin 的电气特性,比如上/下拉、速度、驱动能力等等。传统的配置 pin 的方式就是直接操作相应的寄存器,但是这种配置方式比较繁琐、而且容易出问题(比如 pin 功能冲突)。 pinctrl 子系统就是为了解决这个问题而引入的, pinctrl 子系统主要工作内容如下:

①、获取设备树中 pin 信息。

②、根据获取到的 pin 信息来设置 pin 的复用功能

③、根据获取到的 pin 信息来设置 pin 的电气特性,比如上/下拉、速度、驱动能力等。

对于我们使用者来讲,只需要在设备树里面设置好某个 pin 的相关属性即可,其他的初始化工作均由 pinctrl 子系统来完成, pinctrl 子系统源码目录为 drivers/pinctrl。

45.1.2 I.MX6ULL 的 pinctrl 子系统驱动

1、 PIN 配置信息详解

要使用 pinctrl 子系统,我们需要在设备树里面设置 PIN 的配置信息,毕竟 pinctrl 子系统要根据你提供的信息来配置 PIN 功能,一般会在设备树里面创建一个节点来描述 PIN 的配置信息。打开 imx6ull.dtsi 文件,找到一个叫做 iomuxc 的节点,如下所示:

1、设置PIN的复用和电气属性。

2、配置GPIO的

一、pinctrl子系统

借助pinctrl来设置一个PIN的复用和电气属性。

打开imx6ull.dtsi:

1.1 IOMUXC SNVS控制器

iomuxc_snvs: iomuxc-snvs@02290000 {

compatible = "fsl,imx6ull-iomuxc-snvs";

reg = <0x02290000 0x10000>;

};

1.2 IOMUXC控制器

iomuxc: iomuxc@020e0000 {

compatible = "fsl,imx6ul-iomuxc";

reg = <0x020e0000 0x4000>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_hog_1>;

imx6ul-evk {

pinctrl_hog_1: hoggrp-1 {

fsl,pins = <

MX6UL_PAD_UART1_RTS_B__GPIO1_IO19 0x17059 /* SD1 CD */

MX6UL_PAD_GPIO1_IO05__USDHC1_VSELECT 0x17059 /* SD1 VSELECT */

MX6UL_PAD_GPIO1_IO09__GPIO1_IO09 0x17059 /* SD1 RESET */

>;

};

………

}

};

根据设备的类型,创建对应的子节点,然后设备所用PIN都放到此节点。

1.3 gpr控制器

gpr: iomuxc-gpr@020e4000 {

compatible = "fsl,imx6ul-iomuxc-gpr",

"fsl,imx6q-iomuxc-gpr", "syscon";

reg = <0x020e4000 0x4000>;

};

1.4 如何添加一个PIN的信息

pinctrl_hog_1: hoggrp-1 {

fsl,pins = <

MX6UL_PAD_UART1_RTS_B__GPIO1_IO19 0x17059 /* SD1 CD */

>;

};

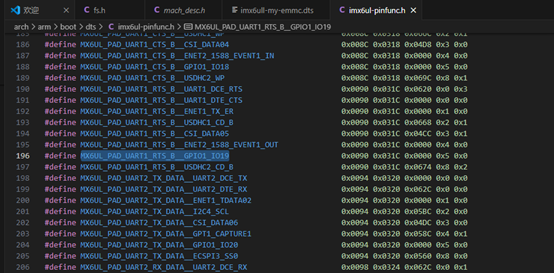

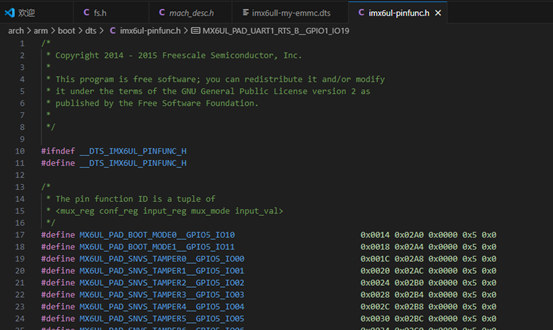

我们在imx6ul-pinfunc.h中找到:

MX6UL_PAD_UART1_RTS_B__GPIO1_IO19 0x0090 0x031C 0x0000 0x5 0x0

<mux_reg conf_reg input_reg mux_mode input_val>

0x0090 0x031C 0x0000 0x5 0x0

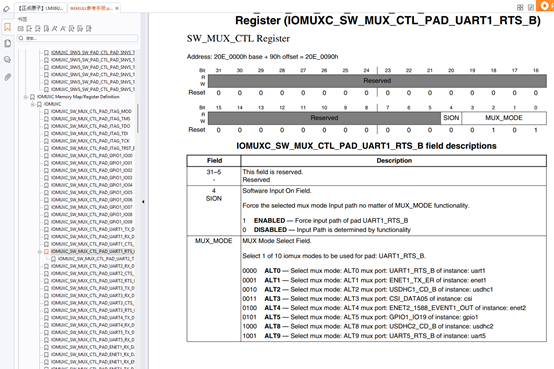

IOMUXC父节点首地址0x020e0000,因此UART1_RTS_B这个PIN的mux寄存器地址 就是:0x020e0000+0x0090=0x020e 0090。

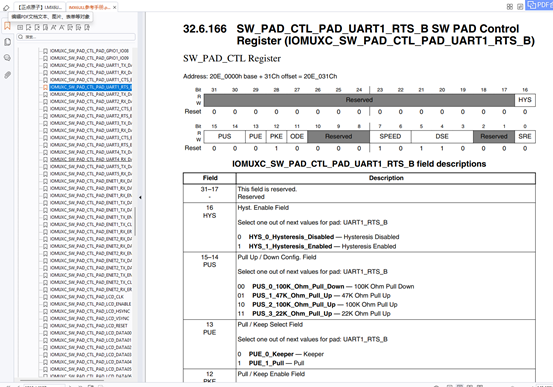

conf_reg:0x020e0000+0x031C=0x020e 031C,这个寄存器就是UART1_RTS_B的电气属性配置寄存器。

input_reg,便宜为0,表示UART1_RTS_B这个PIN没有input功能。

mux_mode:5表示复用为GPIO1_IO19,将其写入0x020e 0090

input_val:就是写入input_reg寄存器的值。

0x17059:为PIN的电气属性配置寄存器值。

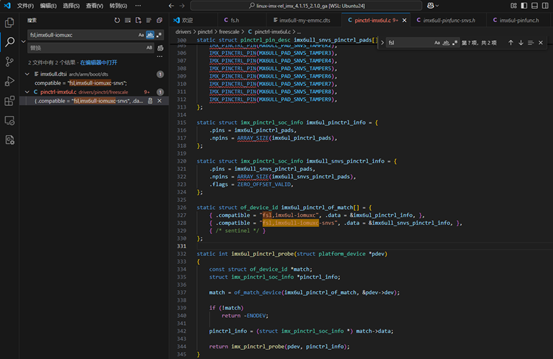

1.5 pincrtl驱动

如何找到IMX6UL对应的pinctrl子系统驱动,设备树里面的设备节点是如何根驱动匹配的呢?通过compatible,此属性是字符串列表。驱动文件里面有一个描述驱动兼容性的东西,当设备树节点的compatible属性和驱动里面的兼容性字符串匹配,也就是一模一样的时候就表示设备和驱动匹配了。

所以我们只需要全局搜索,设备节点里面的compatible属性的值,看看在哪个.c文件里面有,那么此.c文件就是驱动文件。

找到pinctrl-imx6ul.c文件,那么此文件就是6UL/6ULL的pinctrl驱动文件。

/*

* Copyright (C) 2015-2016 Freescale Semiconductor, Inc.

*

* This program is free software; you can redistribute it and/or modify

* it under the terms of the GNU General Public License version 2 as

* published by the Free Software Foundation.

*/

#include <linux/err.h>

#include <linux/init.h>

#include <linux/io.h>

#include <linux/module.h>

#include <linux/of.h>

#include <linux/of_device.h>

#include <linux/pinctrl/pinctrl.h>

#include "pinctrl-imx.h"

enum imx6ul_pads {

MX6UL_PAD_RESERVE0 = 0,

MX6UL_PAD_RESERVE1 = 1,

MX6UL_PAD_RESERVE2 = 2,

MX6UL_PAD_RESERVE3 = 3,

MX6UL_PAD_RESERVE4 = 4,

MX6UL_PAD_RESERVE5 = 5,

MX6UL_PAD_RESERVE6 = 6,

MX6UL_PAD_RESERVE7 = 7,

MX6UL_PAD_RESERVE8 = 8,

MX6UL_PAD_RESERVE9 = 9,

MX6UL_PAD_RESERVE10 = 10,

MX6UL_PAD_SNVS_TAMPER4 = 11,

MX6UL_PAD_RESERVE12 = 12,

MX6UL_PAD_RESERVE13 = 13,

MX6UL_PAD_RESERVE14 = 14,

MX6UL_PAD_RESERVE15 = 15,

MX6UL_PAD_RESERVE16 = 16,

MX6UL_PAD_JTAG_MOD = 17,

MX6UL_PAD_JTAG_TMS = 18,

MX6UL_PAD_JTAG_TDO = 19,

MX6UL_PAD_JTAG_TDI = 20,

MX6UL_PAD_JTAG_TCK = 21,

MX6UL_PAD_JTAG_TRST_B = 22,

MX6UL_PAD_GPIO1_IO00 = 23,

MX6UL_PAD_GPIO1_IO01 = 24,

MX6UL_PAD_GPIO1_IO02 = 25,

MX6UL_PAD_GPIO1_IO03 = 26,

MX6UL_PAD_GPIO1_IO04 = 27,

MX6UL_PAD_GPIO1_IO05 = 28,

MX6UL_PAD_GPIO1_IO06 = 29,

MX6UL_PAD_GPIO1_IO07 = 30,

MX6UL_PAD_GPIO1_IO08 = 31,

MX6UL_PAD_GPIO1_IO09 = 32,

MX6UL_PAD_UART1_TX_DATA = 33,

MX6UL_PAD_UART1_RX_DATA = 34,

MX6UL_PAD_UART1_CTS_B = 35,

MX6UL_PAD_UART1_RTS_B = 36,

MX6UL_PAD_UART2_TX_DATA = 37,

MX6UL_PAD_UART2_RX_DATA = 38,

MX6UL_PAD_UART2_CTS_B = 39,

MX6UL_PAD_UART2_RTS_B = 40,

MX6UL_PAD_UART3_TX_DATA = 41,

MX6UL_PAD_UART3_RX_DATA = 42,

MX6UL_PAD_UART3_CTS_B = 43,

MX6UL_PAD_UART3_RTS_B = 44,

MX6UL_PAD_UART4_TX_DATA = 45,

MX6UL_PAD_UART4_RX_DATA = 46,

MX6UL_PAD_UART5_TX_DATA = 47,

MX6UL_PAD_UART5_RX_DATA = 48,

MX6UL_PAD_ENET1_RX_DATA0 = 49,

MX6UL_PAD_ENET1_RX_DATA1 = 50,

MX6UL_PAD_ENET1_RX_EN = 51,

MX6UL_PAD_ENET1_TX_DATA0 = 52,

MX6UL_PAD_ENET1_TX_DATA1 = 53,

MX6UL_PAD_ENET1_TX_EN = 54,

MX6UL_PAD_ENET1_TX_CLK = 55,

MX6UL_PAD_ENET1_RX_ER = 56,

MX6UL_PAD_ENET2_RX_DATA0 = 57,

MX6UL_PAD_ENET2_RX_DATA1 = 58,

MX6UL_PAD_ENET2_RX_EN = 59,

MX6UL_PAD_ENET2_TX_DATA0 = 60,

MX6UL_PAD_ENET2_TX_DATA1 = 61,

MX6UL_PAD_ENET2_TX_EN = 62,

MX6UL_PAD_ENET2_TX_CLK = 63,

MX6UL_PAD_ENET2_RX_ER = 64,

MX6UL_PAD_LCD_CLK = 65,

MX6UL_PAD_LCD_ENABLE = 66,

MX6UL_PAD_LCD_HSYNC = 67,

MX6UL_PAD_LCD_VSYNC = 68,

MX6UL_PAD_LCD_RESET = 69,

MX6UL_PAD_LCD_DATA00 = 70,

MX6UL_PAD_LCD_DATA01 = 71,

MX6UL_PAD_LCD_DATA02 = 72,

MX6UL_PAD_LCD_DATA03 = 73,

MX6UL_PAD_LCD_DATA04 = 74,

MX6UL_PAD_LCD_DATA05 = 75,

MX6UL_PAD_LCD_DATA06 = 76,

MX6UL_PAD_LCD_DATA07 = 77,

MX6UL_PAD_LCD_DATA08 = 78,

MX6UL_PAD_LCD_DATA09 = 79,

MX6UL_PAD_LCD_DATA10 = 80,

MX6UL_PAD_LCD_DATA11 = 81,

MX6UL_PAD_LCD_DATA12 = 82,

MX6UL_PAD_LCD_DATA13 = 83,

MX6UL_PAD_LCD_DATA14 = 84,

MX6UL_PAD_LCD_DATA15 = 85,

MX6UL_PAD_LCD_DATA16 = 86,

MX6UL_PAD_LCD_DATA17 = 87,

MX6UL_PAD_LCD_DATA18 = 88,

MX6UL_PAD_LCD_DATA19 = 89,

MX6UL_PAD_LCD_DATA20 = 90,

MX6UL_PAD_LCD_DATA21 = 91,

MX6UL_PAD_LCD_DATA22 = 92,

MX6UL_PAD_LCD_DATA23 = 93,

MX6UL_PAD_NAND_RE_B = 94,

MX6UL_PAD_NAND_WE_B = 95,

MX6UL_PAD_NAND_DATA00 = 96,

MX6UL_PAD_NAND_DATA01 = 97,

MX6UL_PAD_NAND_DATA02 = 98,

MX6UL_PAD_NAND_DATA03 = 99,

MX6UL_PAD_NAND_DATA04 = 100,

MX6UL_PAD_NAND_DATA05 = 101,

MX6UL_PAD_NAND_DATA06 = 102,

MX6UL_PAD_NAND_DATA07 = 103,

MX6UL_PAD_NAND_ALE = 104,

MX6UL_PAD_NAND_WP_B = 105,

MX6UL_PAD_NAND_READY_B = 106,

MX6UL_PAD_NAND_CE0_B = 107,

MX6UL_PAD_NAND_CE1_B = 108,

MX6UL_PAD_NAND_CLE = 109,

MX6UL_PAD_NAND_DQS = 110,

MX6UL_PAD_SD1_CMD = 111,

MX6UL_PAD_SD1_CLK = 112,

MX6UL_PAD_SD1_DATA0 = 113,

MX6UL_PAD_SD1_DATA1 = 114,

MX6UL_PAD_SD1_DATA2 = 115,

MX6UL_PAD_SD1_DATA3 = 116,

MX6UL_PAD_CSI_MCLK = 117,

MX6UL_PAD_CSI_PIXCLK = 118,

MX6UL_PAD_CSI_VSYNC = 119,

MX6UL_PAD_CSI_HSYNC = 120,

MX6UL_PAD_CSI_DATA00 = 121,

MX6UL_PAD_CSI_DATA01 = 122,

MX6UL_PAD_CSI_DATA02 = 123,

MX6UL_PAD_CSI_DATA03 = 124,

MX6UL_PAD_CSI_DATA04 = 125,

MX6UL_PAD_CSI_DATA05 = 126,

MX6UL_PAD_CSI_DATA06 = 127,

MX6UL_PAD_CSI_DATA07 = 128,

};

enum imx6ull_lpsr_pads {

MX6ULL_PAD_BOOT_MODE0 = 0,

MX6ULL_PAD_BOOT_MODE1 = 1,

MX6ULL_PAD_SNVS_TAMPER0 = 2,

MX6ULL_PAD_SNVS_TAMPER1 = 3,

MX6ULL_PAD_SNVS_TAMPER2 = 4,

MX6ULL_PAD_SNVS_TAMPER3 = 5,

MX6ULL_PAD_SNVS_TAMPER4 = 6,

MX6ULL_PAD_SNVS_TAMPER5 = 7,

MX6ULL_PAD_SNVS_TAMPER6 = 8,

MX6ULL_PAD_SNVS_TAMPER7 = 9,

MX6ULL_PAD_SNVS_TAMPER8 = 10,

MX6ULL_PAD_SNVS_TAMPER9 = 11,

};

/* Pad names for the pinmux subsystem */

static const struct pinctrl_pin_desc imx6ul_pinctrl_pads[] = {

IMX_PINCTRL_PIN(MX6UL_PAD_RESERVE0),

IMX_PINCTRL_PIN(MX6UL_PAD_RESERVE1),

IMX_PINCTRL_PIN(MX6UL_PAD_RESERVE2),

IMX_PINCTRL_PIN(MX6UL_PAD_RESERVE3),

IMX_PINCTRL_PIN(MX6UL_PAD_RESERVE4),

IMX_PINCTRL_PIN(MX6UL_PAD_RESERVE5),

IMX_PINCTRL_PIN(MX6UL_PAD_RESERVE6),

IMX_PINCTRL_PIN(MX6UL_PAD_RESERVE7),

IMX_PINCTRL_PIN(MX6UL_PAD_RESERVE8),

IMX_PINCTRL_PIN(MX6UL_PAD_RESERVE9),

IMX_PINCTRL_PIN(MX6UL_PAD_RESERVE10),

IMX_PINCTRL_PIN(MX6UL_PAD_SNVS_TAMPER4),

IMX_PINCTRL_PIN(MX6UL_PAD_RESERVE12),

IMX_PINCTRL_PIN(MX6UL_PAD_RESERVE13),

IMX_PINCTRL_PIN(MX6UL_PAD_RESERVE14),

IMX_PINCTRL_PIN(MX6UL_PAD_RESERVE15),

IMX_PINCTRL_PIN(MX6UL_PAD_RESERVE16),

IMX_PINCTRL_PIN(MX6UL_PAD_JTAG_MOD),

IMX_PINCTRL_PIN(MX6UL_PAD_JTAG_TMS),

IMX_PINCTRL_PIN(MX6UL_PAD_JTAG_TDO),

IMX_PINCTRL_PIN(MX6UL_PAD_JTAG_TDI),

IMX_PINCTRL_PIN(MX6UL_PAD_JTAG_TCK),

IMX_PINCTRL_PIN(MX6UL_PAD_JTAG_TRST_B),

IMX_PINCTRL_PIN(MX6UL_PAD_GPIO1_IO00),

IMX_PINCTRL_PIN(MX6UL_PAD_GPIO1_IO01),

IMX_PINCTRL_PIN(MX6UL_PAD_GPIO1_IO02),

IMX_PINCTRL_PIN(MX6UL_PAD_GPIO1_IO03),

IMX_PINCTRL_PIN(MX6UL_PAD_GPIO1_IO04),

IMX_PINCTRL_PIN(MX6UL_PAD_GPIO1_IO05),

IMX_PINCTRL_PIN(MX6UL_PAD_GPIO1_IO06),

IMX_PINCTRL_PIN(MX6UL_PAD_GPIO1_IO07),

IMX_PINCTRL_PIN(MX6UL_PAD_GPIO1_IO08),

IMX_PINCTRL_PIN(MX6UL_PAD_GPIO1_IO09),

IMX_PINCTRL_PIN(MX6UL_PAD_UART1_TX_DATA),

IMX_PINCTRL_PIN(MX6UL_PAD_UART1_RX_DATA),

IMX_PINCTRL_PIN(MX6UL_PAD_UART1_CTS_B),

IMX_PINCTRL_PIN(MX6UL_PAD_UART1_RTS_B),

IMX_PINCTRL_PIN(MX6UL_PAD_UART2_TX_DATA),

IMX_PINCTRL_PIN(MX6UL_PAD_UART2_RX_DATA),

IMX_PINCTRL_PIN(MX6UL_PAD_UART2_CTS_B),

IMX_PINCTRL_PIN(MX6UL_PAD_UART2_RTS_B),

IMX_PINCTRL_PIN(MX6UL_PAD_UART3_TX_DATA),

IMX_PINCTRL_PIN(MX6UL_PAD_UART3_RX_DATA),

IMX_PINCTRL_PIN(MX6UL_PAD_UART3_CTS_B),

IMX_PINCTRL_PIN(MX6UL_PAD_UART3_RTS_B),

IMX_PINCTRL_PIN(MX6UL_PAD_UART4_TX_DATA),

IMX_PINCTRL_PIN(MX6UL_PAD_UART4_RX_DATA),

IMX_PINCTRL_PIN(MX6UL_PAD_UART5_TX_DATA),

IMX_PINCTRL_PIN(MX6UL_PAD_UART5_RX_DATA),

IMX_PINCTRL_PIN(MX6UL_PAD_ENET1_RX_DATA0),

IMX_PINCTRL_PIN(MX6UL_PAD_ENET1_RX_DATA1),

IMX_PINCTRL_PIN(MX6UL_PAD_ENET1_RX_EN),

IMX_PINCTRL_PIN(MX6UL_PAD_ENET1_TX_DATA0),

IMX_PINCTRL_PIN(MX6UL_PAD_ENET1_TX_DATA1),

IMX_PINCTRL_PIN(MX6UL_PAD_ENET1_TX_EN),

IMX_PINCTRL_PIN(MX6UL_PAD_ENET1_TX_CLK),

IMX_PINCTRL_PIN(MX6UL_PAD_ENET1_RX_ER),

IMX_PINCTRL_PIN(MX6UL_PAD_ENET2_RX_DATA0),

IMX_PINCTRL_PIN(MX6UL_PAD_ENET2_RX_DATA1),

IMX_PINCTRL_PIN(MX6UL_PAD_ENET2_RX_EN),

IMX_PINCTRL_PIN(MX6UL_PAD_ENET2_TX_DATA0),

IMX_PINCTRL_PIN(MX6UL_PAD_ENET2_TX_DATA1),

IMX_PINCTRL_PIN(MX6UL_PAD_ENET2_TX_EN),

IMX_PINCTRL_PIN(MX6UL_PAD_ENET2_TX_CLK),

IMX_PINCTRL_PIN(MX6UL_PAD_ENET2_RX_ER),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_CLK),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_ENABLE),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_HSYNC),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_VSYNC),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_RESET),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_DATA00),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_DATA01),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_DATA02),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_DATA03),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_DATA04),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_DATA05),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_DATA06),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_DATA07),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_DATA08),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_DATA09),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_DATA10),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_DATA11),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_DATA12),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_DATA13),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_DATA14),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_DATA15),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_DATA16),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_DATA17),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_DATA18),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_DATA19),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_DATA20),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_DATA21),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_DATA22),

IMX_PINCTRL_PIN(MX6UL_PAD_LCD_DATA23),

IMX_PINCTRL_PIN(MX6UL_PAD_NAND_RE_B),

IMX_PINCTRL_PIN(MX6UL_PAD_NAND_WE_B),

IMX_PINCTRL_PIN(MX6UL_PAD_NAND_DATA00),

IMX_PINCTRL_PIN(MX6UL_PAD_NAND_DATA01),

IMX_PINCTRL_PIN(MX6UL_PAD_NAND_DATA02),

IMX_PINCTRL_PIN(MX6UL_PAD_NAND_DATA03),

IMX_PINCTRL_PIN(MX6UL_PAD_NAND_DATA04),

IMX_PINCTRL_PIN(MX6UL_PAD_NAND_DATA05),

IMX_PINCTRL_PIN(MX6UL_PAD_NAND_DATA06),

IMX_PINCTRL_PIN(MX6UL_PAD_NAND_DATA07),

IMX_PINCTRL_PIN(MX6UL_PAD_NAND_ALE),

IMX_PINCTRL_PIN(MX6UL_PAD_NAND_WP_B),

IMX_PINCTRL_PIN(MX6UL_PAD_NAND_READY_B),

IMX_PINCTRL_PIN(MX6UL_PAD_NAND_CE0_B),

IMX_PINCTRL_PIN(MX6UL_PAD_NAND_CE1_B),

IMX_PINCTRL_PIN(MX6UL_PAD_NAND_CLE),

IMX_PINCTRL_PIN(MX6UL_PAD_NAND_DQS),

IMX_PINCTRL_PIN(MX6UL_PAD_SD1_CMD),

IMX_PINCTRL_PIN(MX6UL_PAD_SD1_CLK),

IMX_PINCTRL_PIN(MX6UL_PAD_SD1_DATA0),

IMX_PINCTRL_PIN(MX6UL_PAD_SD1_DATA1),

IMX_PINCTRL_PIN(MX6UL_PAD_SD1_DATA2),

IMX_PINCTRL_PIN(MX6UL_PAD_SD1_DATA3),

IMX_PINCTRL_PIN(MX6UL_PAD_CSI_MCLK),

IMX_PINCTRL_PIN(MX6UL_PAD_CSI_PIXCLK),

IMX_PINCTRL_PIN(MX6UL_PAD_CSI_VSYNC),

IMX_PINCTRL_PIN(MX6UL_PAD_CSI_HSYNC),

IMX_PINCTRL_PIN(MX6UL_PAD_CSI_DATA00),

IMX_PINCTRL_PIN(MX6UL_PAD_CSI_DATA01),

IMX_PINCTRL_PIN(MX6UL_PAD_CSI_DATA02),

IMX_PINCTRL_PIN(MX6UL_PAD_CSI_DATA03),

IMX_PINCTRL_PIN(MX6UL_PAD_CSI_DATA04),

IMX_PINCTRL_PIN(MX6UL_PAD_CSI_DATA05),

IMX_PINCTRL_PIN(MX6UL_PAD_CSI_DATA06),

IMX_PINCTRL_PIN(MX6UL_PAD_CSI_DATA07),

};

/* pad for i.MX6ULL lpsr pinmux */

static struct pinctrl_pin_desc imx6ull_snvs_pinctrl_pads[] = {

IMX_PINCTRL_PIN(MX6ULL_PAD_BOOT_MODE0),

IMX_PINCTRL_PIN(MX6ULL_PAD_BOOT_MODE1),

IMX_PINCTRL_PIN(MX6ULL_PAD_SNVS_TAMPER0),

IMX_PINCTRL_PIN(MX6ULL_PAD_SNVS_TAMPER1),

IMX_PINCTRL_PIN(MX6ULL_PAD_SNVS_TAMPER2),

IMX_PINCTRL_PIN(MX6ULL_PAD_SNVS_TAMPER3),

IMX_PINCTRL_PIN(MX6ULL_PAD_SNVS_TAMPER4),

IMX_PINCTRL_PIN(MX6ULL_PAD_SNVS_TAMPER5),

IMX_PINCTRL_PIN(MX6ULL_PAD_SNVS_TAMPER6),

IMX_PINCTRL_PIN(MX6ULL_PAD_SNVS_TAMPER7),

IMX_PINCTRL_PIN(MX6ULL_PAD_SNVS_TAMPER8),

IMX_PINCTRL_PIN(MX6ULL_PAD_SNVS_TAMPER9),

};

static struct imx_pinctrl_soc_info imx6ul_pinctrl_info = {

.pins = imx6ul_pinctrl_pads,

.npins = ARRAY_SIZE(imx6ul_pinctrl_pads),

};

static struct imx_pinctrl_soc_info imx6ull_snvs_pinctrl_info = {

.pins = imx6ull_snvs_pinctrl_pads,

.npins = ARRAY_SIZE(imx6ull_snvs_pinctrl_pads),

.flags = ZERO_OFFSET_VALID,

};

static struct of_device_id imx6ul_pinctrl_of_match[] = {

{ .compatible = "fsl,imx6ul-iomuxc", .data = &imx6ul_pinctrl_info, },

{ .compatible = "fsl,imx6ull-iomuxc-snvs", .data = &imx6ull_snvs_pinctrl_info, },

{ /* sentinel */ }

};

static int imx6ul_pinctrl_probe(struct platform_device *pdev)

{

const struct of_device_id *match;

struct imx_pinctrl_soc_info *pinctrl_info;

match = of_match_device(imx6ul_pinctrl_of_match, &pdev->dev);

if (!match)

return -ENODEV;

pinctrl_info = (struct imx_pinctrl_soc_info *) match->data;

return imx_pinctrl_probe(pdev, pinctrl_info);

}

static struct platform_driver imx6ul_pinctrl_driver = {

.driver = {

.name = "imx6ul-pinctrl",

.owner = THIS_MODULE,

.of_match_table = of_match_ptr(imx6ul_pinctrl_of_match),

},

.probe = imx6ul_pinctrl_probe,

.remove = imx_pinctrl_remove,

};

static int __init imx6ul_pinctrl_init(void)

{

return platform_driver_register(&imx6ul_pinctrl_driver);

}

arch_initcall(imx6ul_pinctrl_init);

static void __exit imx6ul_pinctrl_exit(void)

{

platform_driver_unregister(&imx6ul_pinctrl_driver);

}

module_exit(imx6ul_pinctrl_exit);

MODULE_AUTHOR("Anson Huang <Anson.Huang@freescale.com>");

MODULE_DESCRIPTION("Freescale imx6ul pinctrl driver");

MODULE_LICENSE("GPL v2");

当驱动和设备匹配以后执行,probe函数。也就是

imx6ul_pinctrl_probe

->imx_pinctrl_probe

-> 此函数会初始化imx_pinctrl_desc,为pinctrl_desc类型的结构体。重点是:

imx_pinctrl_desc->pctlops = &imx_pctrl_ops;

imx_pinctrl_desc->pmxops = &imx_pmx_ops;

imx_pinctrl_desc->confops = &imx_pinconf_ops;

最后通过pinctrl_register函数向系统注册一个imx_pinctrl_desc

->imx_pinctrl_probe_dt

->imx_pinctrl_parse_functions

->imx_pinctrl_parse_groups

-> pin_reg->mux_reg = mux_reg;

pin_reg->conf_reg = conf_reg;

pin->input_reg = be32_to_cpu(*list++);

pin->mux_mode = be32_to_cpu(*list++);

pin->input_val = be32_to_cpu(*list++);

config = be32_to_cpu(*list++);

if (config & IMX_PAD_SION)

pin->mux_mode |= IOMUXC_CONFIG_SION;

pin->config = config & ~IMX_PAD_SION;

imx_pinconf_set函数设置PIN的电气属性

imx_pmx_set函数设置PIN的复用

二、gpio子系统

使用gpio子系统来使用gpio。

45.2.1 gpio 子系统简介

上一小节讲解了 pinctrl 子系统, pinctrl 子系统重点是设置 PIN(有的 SOC 叫做 PAD)的复用和电气属性,如果 pinctrl 子系统将一个 PIN 复用为 GPIO 的话,那么接下来就要用到 gpio 子系统了。 gpio 子系统顾名思义,就是用于初始化 GPIO 并且提供相应的 API 函数,比如设置 GPIO为输入输出,读取 GPIO 的值等。 gpio 子系统的主要目的就是方便驱动开发者使用 gpio,驱动开发者在设备树中添加 gpio 相关信息,然后就可以在驱动程序中使用 gpio 子系统提供的 API函数来操作 GPIO, Linux 内核向驱动开发者屏蔽掉了 GPIO 的设置过程,极大的方便了驱动开发者使用 GPIO。

45.2.2 I.MX6ULL 的 gpio 子系统驱动

1、设备树中的 gpio 信息

I.MX6ULL-ALPHA 开发板上的 UART1_RTS_B 做为 SD 卡的检测引脚, UART1_RTS_B 复用为 GPIO1_IO19,通过读取这个 GPIO 的高低电平就可以知道 SD 卡有没有插入。首先肯定是将 UART1_RTS_B 这个 PIN 复用为 GPIO1_IO19,并且设置电气属性,也就是上一小节讲的pinctrl 节点。打开 imx6ull-alientek-emmc.dts, UART1_RTS_B 这个 PIN 的 pincrtl 设置如下:

2.1 gpio使用方式

1、gpio在设备树中的表示方法

&usdhc1 {

pinctrl-names = "default", "state_100mhz", "state_200mhz";

pinctrl-0 = <&pinctrl_usdhc1>;

pinctrl-1 = <&pinctrl_usdhc1_100mhz>;

pinctrl-2 = <&pinctrl_usdhc1_200mhz>;

cd-gpios = <&gpio1 19 GPIO_ACTIVE_LOW>;

keep-power-in-suspend;

enable-sdio-wakeup;

vmmc-supply = <®_sd1_vmmc>;

status = "okay";

};

定义了一个cd-gpios属性。

此处使用GPIO1_IO19。

gpio1: gpio@0209c000 {

compatible = "fsl,imx6ul-gpio", "fsl,imx35-gpio";

reg = <0x0209c000 0x4000>;

interrupts = <GIC_SPI 66 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 67 IRQ_TYPE_LEVEL_HIGH>;

gpio-controller;

#gpio-cells = <2>;

interrupt-controller;

#interrupt-cells = <2>;

};

devicetree\bindings\gpio

如何从设备树中获取要使用的GPIO信息。of函数。

2、驱动中对gpio的操作函数

1、首先,获取到GPIO所处的设备节点,比如of_find_node_by_path。

2、获取GPIO编号, of_get_named_gpio函数,返回值就是GPIO编号。

3、请求此编号的GPIO,gpio_request函数

4、设置GPIO,输入或输出,gpio_direction_input或gpio_direction_output。

5、如果是输入,那么通过gpio_get_value函数读取GPIO值,如果是输出,通过gpio_set_value设置GPIO值。

2.2 gpio驱动

1、gpiolib

两部分,给原厂编写GPIO底层驱动的,给驱动开发人员使用GPIO操作函数的。

使用gpiochip_add向系统添加gpio_chip,这些都是半导体原厂做的,这部分就是最底层的GPIO驱动。

2、gpio驱动

在drivers/gpio目录下,gpio-xxx.c文件为具体芯片的驱动文件,

static struct mxc_gpio_hwdata imx35_gpio_hwdata = {

.dr_reg = 0x00,

.gdir_reg = 0x04,

.psr_reg = 0x08,

.icr1_reg = 0x0c,

.icr2_reg = 0x10,

.imr_reg = 0x14,

.isr_reg = 0x18,

.edge_sel_reg = 0x1c,

.low_level = 0x00,

.high_level = 0x01,

.rise_edge = 0x02,

.fall_edge = 0x03,

};

mxc_gpio_probe

-> mxc_gpio_get_hw 获取6ULL的GPIO寄存器组。

-> bgpio_init 重点初始化gpio_chip

->gpiochip_add 向系统添加gpio_chip

三、编写驱动

3.1、修改设备树

3.2 编写驱动

申请IO的时候失败,大部分原因是这个IO被其他外设占用了。检查设备树,查找有哪些使用同一IO的设备。

1,检查复用,也就是pinctl设置。

2,gpio使用

四、运行测试

五、总结

1,添加pinctrl信息,

2,检查当前设备树中要使用的IO有没有被其他设备使用,如果有的话要处理。

3,添加设备节点,在设备节点中创建一个属性,此属性描述所使用的gpio。

4,编写驱动,获取对应的gpio编号,并申请IO,成功以后即可使用此Io