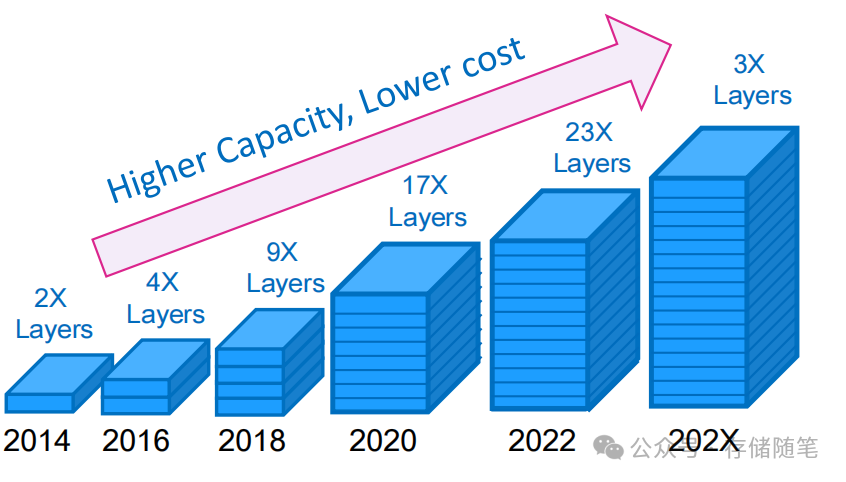

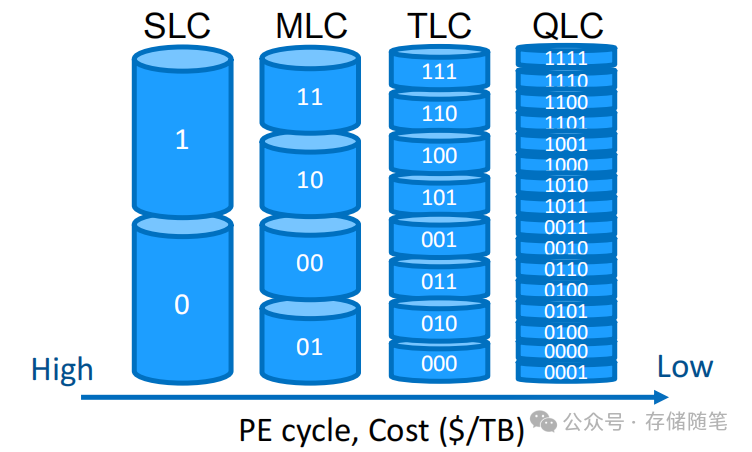

在当今数字化时代,数据量呈爆炸式增长,对存储技术的性能、容量和可靠性提出了前所未有的高要求。3D NAND闪存作为主流存储技术,正朝着更高密度、更低成本的方向持续演进。在此过程中,低密度奇偶校验码(LDPC)技术,尤其是16K LDPC,成为提升存储系统性能和可靠性的关键技术之一。然而,16K LDPC在实际应用中面临诸多挑战,需要创新的解决方案来充分发挥其潜力。

1. LDPC技术背景

LDPC由罗伯特·加拉格(Robert G. Gallager)在1960年提出,在沉寂多年后,随着计算能力提升和通信技术发展,于20世纪90年代重新受到关注,并在存储领域得到广泛应用。其核心原理基于线性分组码,通过构建稀疏校验矩阵对数据进行编码。编码时,在原始数据中加入冗余信息形成码字;解码阶段,利用校验矩阵和接收到的含噪数据进行迭代计算,逐步纠正错误。

与传统纠错码(如BCH码)相比,LDPC具有显著优势。它采用的迭代解码算法能在低信噪比环境下有效工作,在相同误码率(BER)要求下,所需信噪比更低,这意味着能更精准地从噪声数据中恢复原始信息。同时,通过调整校验矩阵的结构和参数,可灵活设计码长、码率和纠错能力,以满足不同存储场景需求。在3D NAND闪存中,存储单元数量不断增加,数据错误概率随之上升,LDPC的这些优势使其成为保障数据可靠性的理想选择。

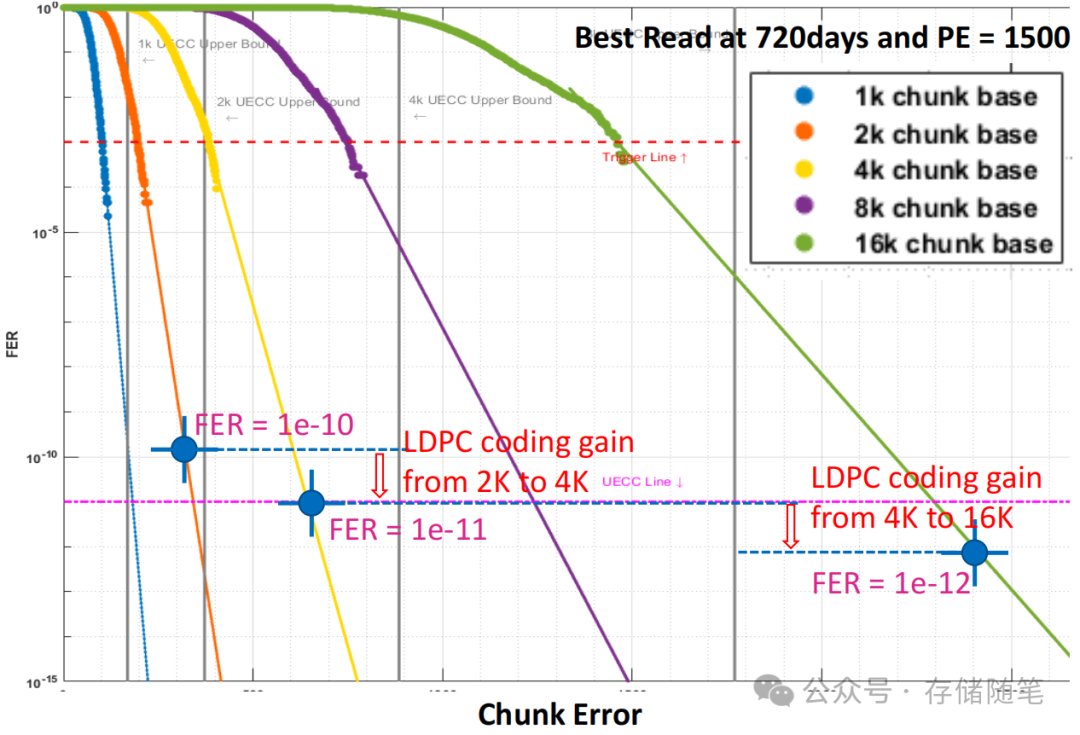

随着3D NAND闪存层数增加、存储密度提高,数据错误率也相应提升,对纠错码性能要求愈发严格。更长码长的LDPC在应对高密度存储产生的复杂错误时表现更优,因为长码长可引入更多冗余信息,增强纠错能力。例如,16K LDPC相比4K LDPC,在处理相同错误分布时,理论上能纠正更多错误,从而降低误码率,提高存储系统可靠性,这促使行业对16K LDPC技术的研究和应用不断深入。

扩展阅读:

2. 16K LDPC面临的挑战

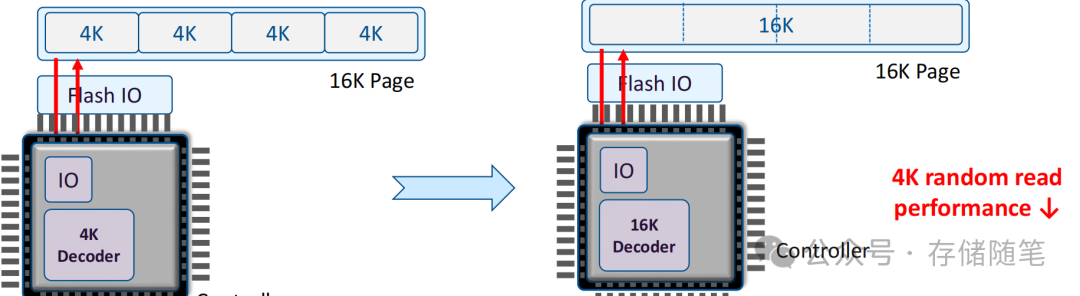

(1)读写操作不匹配

在SSD系统中,常见的读写操作以4K为基本单位,而16K LDPC的页面大小为16K。这一差异导致在进行4K随机读操作时,性能严重受限。由于每次读取的数据量小于页面大小,无法充分利用16K页面的带宽优势,并且可能需要额外的地址转换和数据拼接操作。在频繁的4K随机读场景下,这些额外操作会增加读取延迟,降低系统整体性能。

(2)收益与成本问题

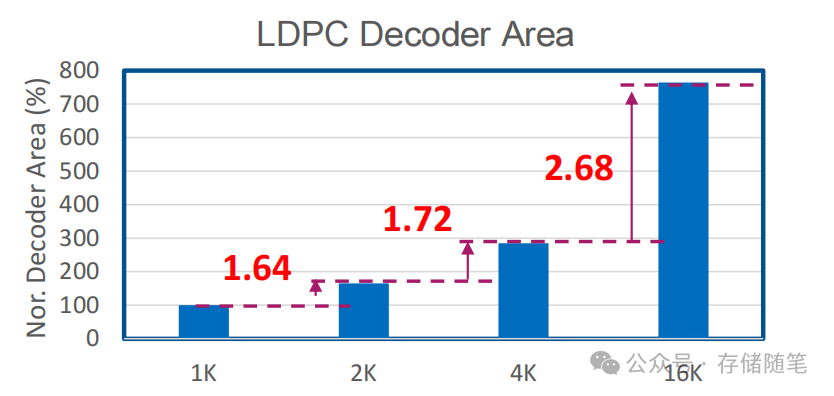

从编码增益和硬件资源占用角度看,16K LDPC在实际应用中的优势并不明显。虽然随着码长增加,编码增益有所提升,但从4K到16K的增益提升幅度相对较小。

相比之下,16K LDPC解码器的实现需要更大的芯片面积和更高的功耗。在有限的芯片空间内,增加解码器面积会影响其他功能模块布局,提高成本。而且更高的功耗会导致发热问题,影响存储设备的稳定性和寿命。这使得在权衡性能提升和成本增加时,16K LDPC的性价比优势不突出。

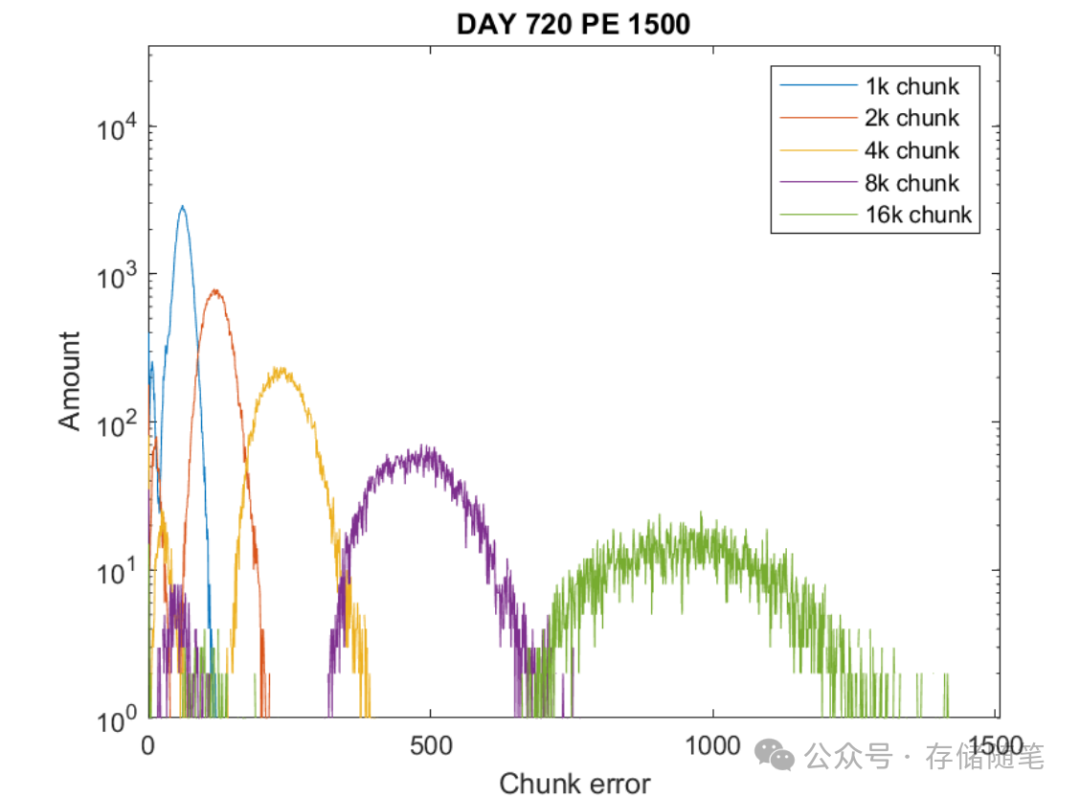

(3)错误分布不均匀

16K LDPC在面对不同大小数据块时,错误分布呈现不均匀特性。由于3D NAND闪存存储单元物理特性差异、编程擦除次数不均衡以及外部环境干扰等因素,不同数据块出现错误的概率和错误类型各不相同。在一些情况下,部分数据块可能频繁出现错误,而其他数据块则相对稳定。这种不均匀的错误分布增加了错误检测和纠正的复杂性,传统的统一纠错策略难以适应这种情况,导致纠错效率降低,影响数据可靠性。

3. 业内解决技术方案

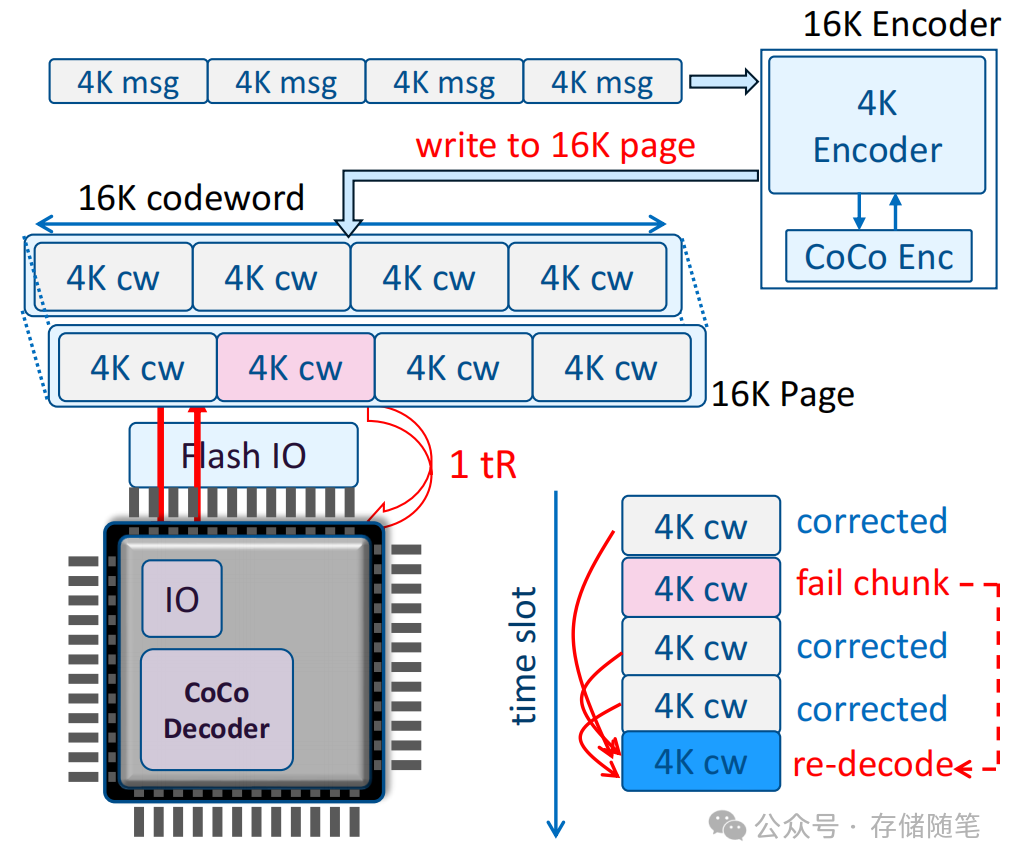

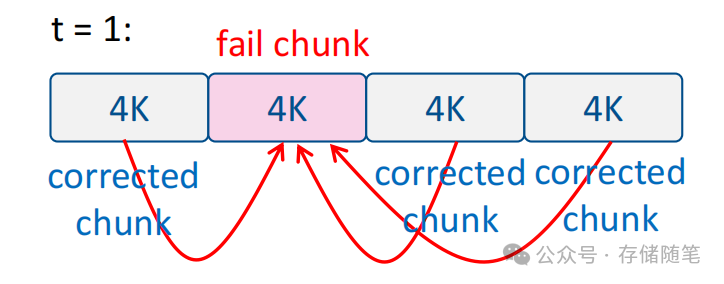

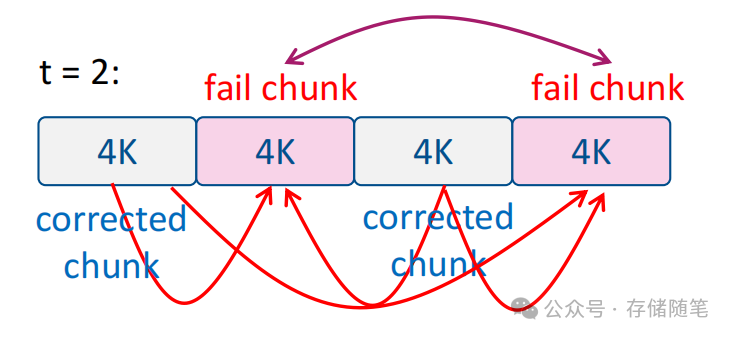

针对16K LDPC应用难题,业内SSD控制器厂商SMI提出的一种方案CoCo(Collaborative Codeword)技术。其核心概念是利用已成功校正的块信息辅助重新解码失败的块。在CoCo技术的码结构中,四个4K码字组成一个16K码字。编码时,将4个4K消息分别编码为4个4K码字,再组合成16K码字存储;解码时,若某个4K码字解码失败,可借助其他已成功解码的4K码字信息进行重新解码。

CoCo技术优势:

适应4K读写操作:在随机4K读写条件下,CoCo技术表现卓越。由于其基于4K码字的协同解码机制,能有效应对4K读写模式,避免了16K LDPC与4K读写操作不匹配的问题。在4K读操作时,即使遇到部分块读取失败,也能快速利用其他已校正块信息重新解码,显著提升4K随机读性能。

接近16K解码性能:CoCo技术通过巧妙的协同机制,在解码性能上能接近真正的16K解码器。在处理复杂错误时,四个4K码字相互协作,多次迭代解码,利用冗余信息纠正错误,达到与16K解码器相近的纠错效果,保障数据高可靠性。

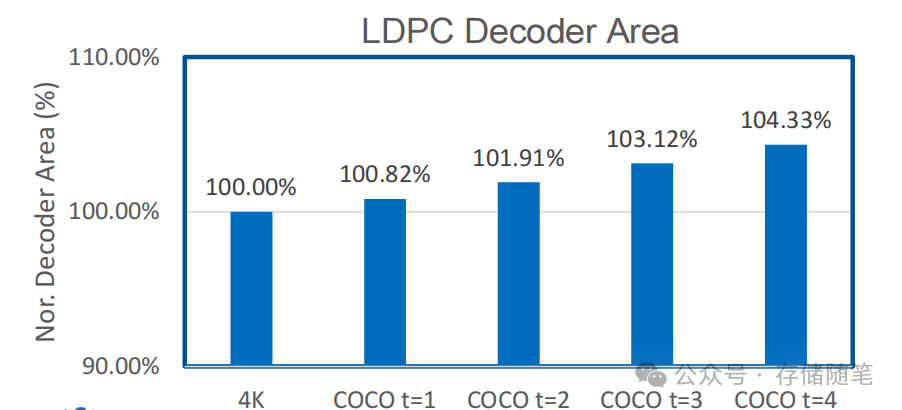

低解码器复杂度:CoCo技术的解码器复杂度与4K解码器相近。这在硬件实现上意义重大,意味着无需大幅增加硬件成本和资源即可支持16K LDPC功能。与传统16K LDPC解码器相比,CoCo技术在保证性能前提下,降低了硬件设计难度和成本,提高了存储系统整体性价比。

CoCo技术类型及效果:

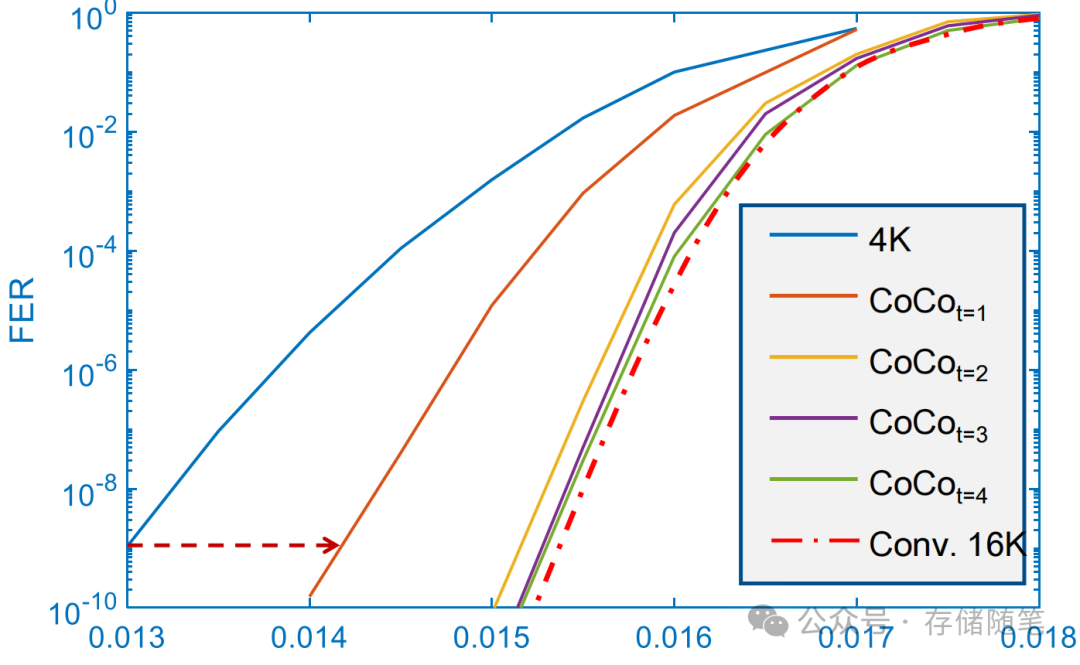

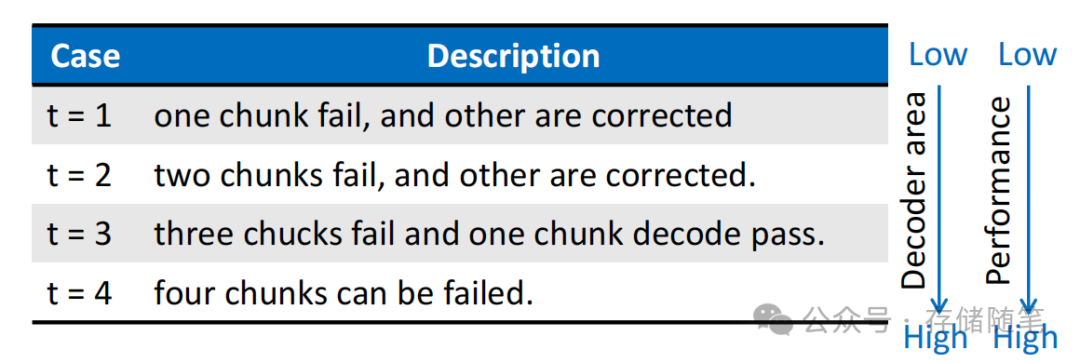

CoCo技术根据失败块数量分为四种类型(t = 1、t = 2、t = 3、t = 4)。

t = 1:仅有一个块失败,其他块均已校正。此时解码器复杂度最低,利用三个已校正块信息可快速恢复失败块数据,在保证数据准确性的同时实现高效解码。

- t = 2:两个块失败。这种情况下,CoCo技术在性能和复杂度之间达到良好平衡。通过合理利用两个已校正块信息,能有效重新解码失败块,在一定复杂度下实现较高解码成功率,是CoCo技术的“最佳平衡点”。

t = 3:三个块失败,仅一个块解码通过。虽然解码难度较大,但借助唯一成功解码块的信息,CoCo技术仍能对失败块进行重新解码,在复杂错误环境下展现出一定纠错能力。

t = 4:四个块全部失败。尽管情况极端,但CoCo技术仍可尝试解码,在某些情况下能实现较高解码成功率,展现出最佳解码性能,不过解码复杂度相对较高。

随着3D NAND闪存技术不断发展,存储密度将持续提高,数据可靠性面临更大挑战。CoCo技术有望在未来存储领域发挥更重要作用,为存储行业提供高效、可靠且成本效益高的解决方案。同时,基于CoCo技术的进一步优化和创新值得期待,例如结合先进的信号处理算法和机器学习技术,以应对更复杂的存储环境和错误模式,推动存储技术持续发展。

如果您看完有所受益,欢迎点击文章底部左下角“关注”并点击“分享”、“在看”,非常感谢!

精彩推荐: