XC5VSX95T‑1FFG1136I 属于 AMD/Xilinx Virtex‑5 SXT 平台,基于 65 nm 铜 CMOS 工艺,集成 94 208 个逻辑单元(LE)、7 360 个 CLB、640 个 DSP48E 切片、8.784 Mbit Block RAM、1.520 Mbit 分布式 RAM;配备 16 路 RocketIO™ GTP 收发器(最高 3.75 Gb/s)和 640 个通用 I/O,引脚封装为 1136‑ball FCBGA(35 × 35 mm),核心电压典型 1.0 V(范围 0.95–1.05 V),支持工业级温度(–40 °C 至 100 °C),最高内核时钟可达 550 MHz。

平台定位与典型应用

Virtex‑5 SXT 平台定位于高性能信号处理,高度优化的 DSP 能力与高速串行互连,适合 5G 无线前端、软件定义无线电、广播视频处理、高速网络转发、机器视觉与工业自动化等场景。

核心架构与工艺

工艺节点:65 nm 铜 CMOS,提供比前代 90 nm 平台更高的性能/功耗比。

架构特点:基于第二代 ASMBL™ 列式架构,支持高效路由与可扩展存储,集成专用硬件加速模块(如 PCIe® 端点、三模式以太网 MAC 等)。

逻辑资源

逻辑单元 (LE):94 208 个,可映射为 CLB、LUT 与 FF。

查找表 & 触发器:每个 CLB 含 2 个切片,每切片包括 4 个 6‑输入 LUT 和 4 个 Flip‑Flop,合计支持 217 K LUT 与 434 K FF(推算)。

逻辑数组块 (LAB/CLB):7 360 个 CLB。

存储资源

分布式 RAM:1 520 kbit,用于小规模、低延迟缓存。

Block RAM (BRAM):8 784 kbit(36 kbit×244 块),支持自定义宽度、双口和内置 ECC。

DSP 切片

DSP48E:640 个,内含 25 × 18 位乘法器、二级累加器、可选位逻辑与流水线,最高可并行运行 550 MHz × 640 = 352 GMAC。

高速收发器与 I/O

RocketIO™ GTP 收发器:16 路,可达 3.75 Gb/s,多协议 (CPRI/OBSAI、SDI、PCIe、Ethernet、Serial RapidIO 等) 直连。

通用 I/O:640 个,可配置为差分或单端 1.2 – 3.3 V,支持细粒度银行与主动终端 (DCI)。

电气与热特性

核心电压 (VCCINT):典型 1.0 V,范围 0.95 – 1.05 V。

I/O 电压 (VCCO):1.2 – 3.3 V 可选(每 I/O 银行独立)。

温度等级:工业级 (–40 °C 至 100 °C TJ)。

最大工作频率:内核最高 550 MHz。

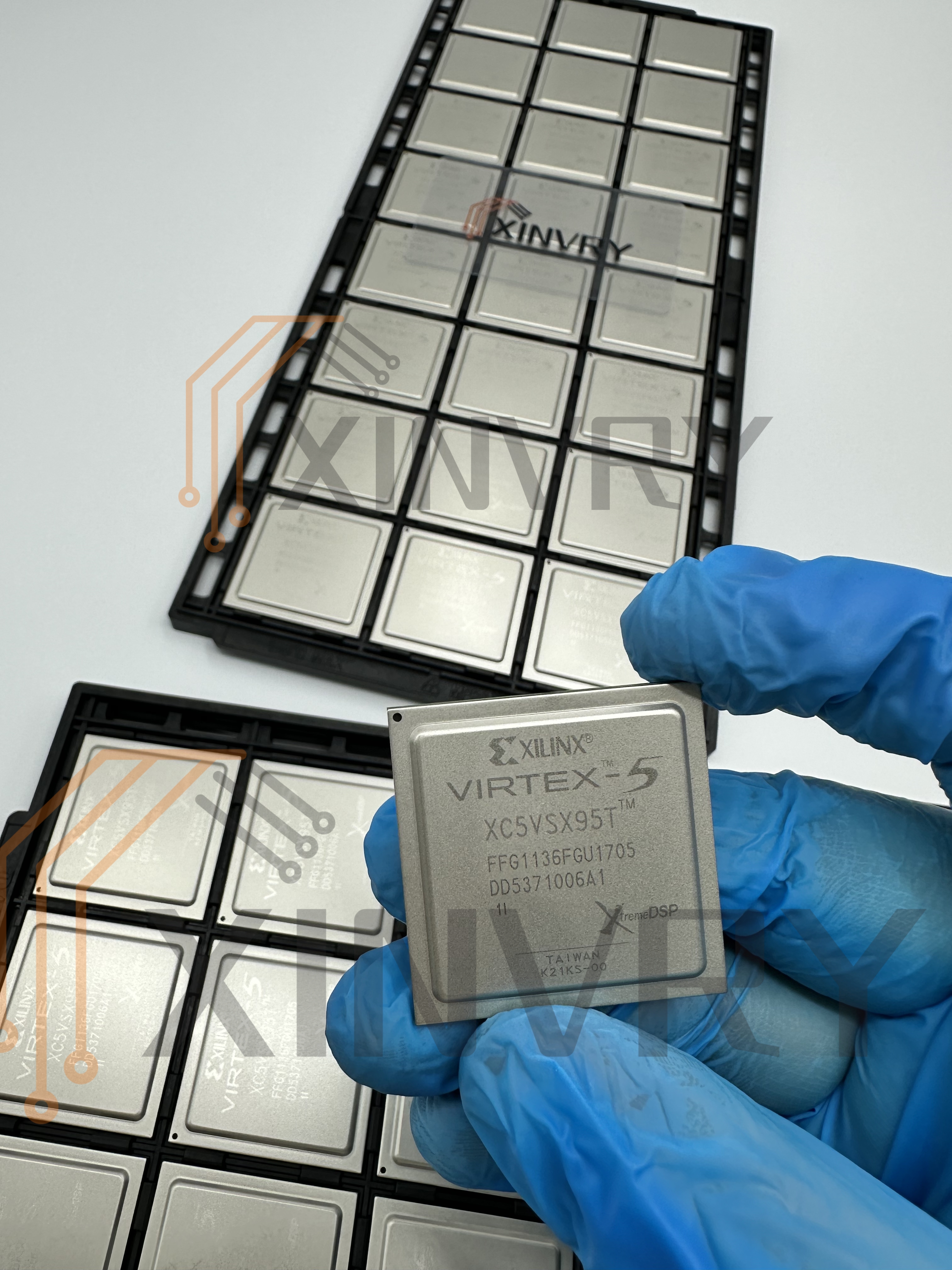

封装与封装选项

封装形式:1136‑ball FCBGA,球间距 1.0 mm,整体尺寸 35 × 35 × 3.4 mm。

湿度敏感度等级:MSL 4 (72 h)。

开发生态与评估平台

开发套件:Xilinx ML506/ML507 (SXT) Evaluation Platform,提供 DDR2/DDR3、RocketIO、FMC 接口等,便于收发器和 DSP 性能验证。

设计工具:Vivado 及 ISE Design Suite (含 System Generator、ChipScope、Platform Cable USB II 支持)。