目前FPGA的开发和官方的EDA工具是高度绑定的,用哪家的芯片只能用其配套的EDA工具进行开发(综合可选工具,布局布线没有可选的工具),那么有没有其他的开发方式呢?今天就介绍一个使用开源工具链来开发FPGA的方式。

本文核心:开源 FPGA 工具链,例如 APIO、IceStrom、yosys OssCAD 等使用。

工具链简介

APIO

简介:

APIO(Advanced Python Integration for OpenFPGA)是一个基于Python的FPGA开发工具链封装器,旨在简化开源FPGA工具的使用。它整合了IceStorm、yosys等工具,提供一键式编译、烧录和调试功能。

官网/GitHub: https://github.com/FPGAwars/apio (注:APIO 是 FPGAwars 社区项目,GitHub 是主要资源库)

特点:

支持多平台(Linux/macOS/Windows)。

自动化依赖管理(如自动安装IceStorm工具链)。

支持常见的FPGA开发板(如iCE40、ECP5等)。

提供项目模板和快速构建脚本。

用途:

适合快速原型开发,尤其适合初学者或希望避免手动配置工具链的用户。

IceStorm

简介:

IceStorm是Lattice iCE40 FPGA的开源工具链,包含综合(yosys)、布局布线(arachne-pnr/nextpnr)、位流生成(icepack)和烧录工具(iceprog)。

官网: http://www.clifford.at/icestorm/

GitHub: https://github.com/YosysHQ/icestorm

关键组件:

Yosys:RTL综合工具,将Verilog转换为iCE40支持的网表。

nextpnr:新一代布局布线工具,支持iCE40和ECP5。

iceprog:通过USB烧录位流到FPGA。

特点:

完全开源,无需商业许可证。

支持低功耗、低成本FPGA开发。

用途:

适用于iCE40 FPGA的开发,如Lattice IceStick、TinyFPGA等开发板。

Yosys

简介:

Yosys(Yosys Open SYnthesis Suite)是一个开源的RTL综合工具,支持Verilog/VHDL到目标网表的转换。

官网: https://yosyshq.net/yosys/

GitHub: https://github.com/YosysHQ/yosys

功能:

逻辑综合、优化、形式化验证。

支持多种FPGA架构(iCE40、ECP5、Xilinx 7系列等)。

可扩展的插件系统(如TinyTapeout流程)。

用途:

作为IceStorm和许多其他开源工具链的核心综合引擎,广泛应用于学术研究和工业项目。

OssCAD(或 OSSCAD)

简介:

OssCAD(Open Source System for Chip and ASIC Design)是一个开源硬件设计生态系统,强调从RTL到GDSII的全流程工具链。

说明: "OssCAD" 并非单一工具,而是开源硬件工具链的统称,指以下生态:

OSSCAD Suite(社区项目): https://github.com/osscda

相关工具链(Yosys + nextpnr + OpenROAD):

OpenROAD (ASIC 设计): https://theopenroadproject.org/

关键工具:

包含Yosys、nextpnr、OpenROAD(用于ASIC布局布线)、Magic(版图编辑)等。

支持FPGA和ASIC设计。

特点:

社区驱动,强调开放性和协作。

与商业工具(如Cadence/Synopsys)互补,适合教学和小规模项目。

用途:

ASIC原型设计、FPGA验证及开源芯片(如RISC-V)开发。

工具链关系与典型流程

FPGA开发流程(以iCE40为例):

使用Yosys将Verilog综合为网表(.blif)。

用nextpnr进行布局布线,生成位流(.asc)。

通过icepack生成二进制文件(.bin),用iceprog烧录到FPGA。

APIO可自动化上述步骤。

ASIC/OSSCAD流程:

Yosys + OpenROAD + Magic 实现从RTL到版图的全流程。

其他关键链接

FPGAwars(APIO 所属社区): https://fpgawars.github.io/

YosysHQ(Yosys/IceStorm/nextpnr 维护团队): https://yosyshq.net/

注意事项

部分工具(如 IceStorm/Yosys)已合并到 YosysHQ 组织下统一维护。

开源工具更新较快,建议通过 GitHub 获取最新版本。

虽然这些软件在基于 Linux 的发行版或 WSL 中运行效果最佳,但在这里我们将在 Windows(10)上完成所有操作。

步骤 0. 准备系统。

要开始使用工具链,系统应该包含 Python 3.5 或更高版本,可以使用以下命令检查系统上的 Python 版本

$ python --version应该得到这样的输出。

如果没有,需要在系统上下载安装 python 和 pip。

步骤1. 获取系统上的 API

系统准备就绪后,我们现在需要在系统上安装 apio。在 Windows 终端中使用此命令即可轻松完成。

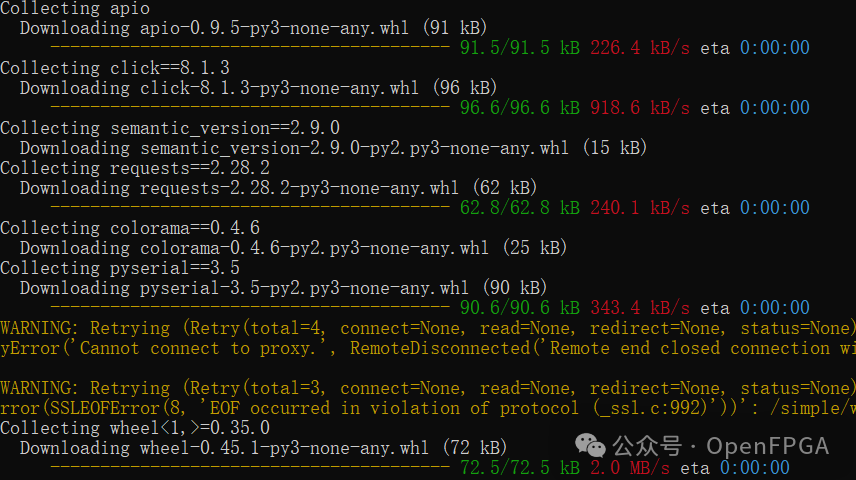

pip install -U apio此命令将下载系统上的 apio,apio 作为将用于 FPGA 开发的所有项目和工具的管理器。

步骤3. 安装所有软件(Yosys,GTKwave,nxtpnr)

FPGA 开发过程中使用各种工具,这些是需要的

OSS CAD -Yosys(验证)

Gtkwave(仿真)

IceStrom

这些软件可以单独下载安装,但我们将使用命令下载完整的包。

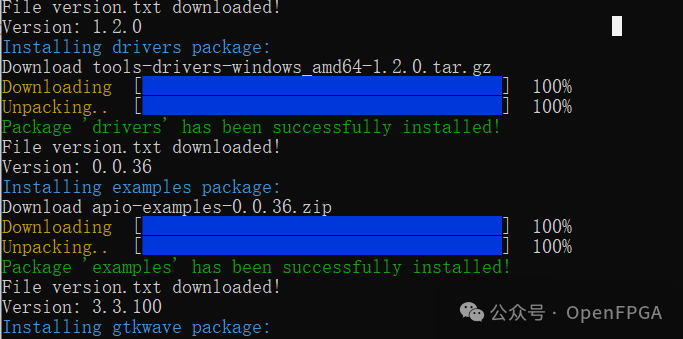

apio install --allapio 将开始下载所有支持文件,这可能需要一些时间,具体取决于网络速度。

可以在此文档页面上阅读 apio 文档

https://apiodoc.readthedocs.io/en/stable/source/quick_start.html

下载后,可以使用此命令检查版本。

apio --version这显示了系统中现有的 apio 版本。

下面这些都是我们将要使用的各种 apio 命令。

$ apio

Usage: apio [OPTIONS] COMMAND [ARGS]...

Options:

--version Show the version and exit.

--help Show this message and exit.

Project commands:

build Synthesize the bitstream.

clean Clean the previous generated files.

lint Lint the verilog code.

sim Launch the verilog simulation.

time Bitstream timing analysis.

upload Upload the bitstream to the FPGA.

verify Verify the verilog code.

Setup commands:

drivers Manage FPGA boards drivers.

init Manage apio projects.

install Install packages.

uninstall Uninstall packages.

Utility commands:

boards Manage FPGA boards.

config Apio configuration.

examples Manage verilog examples.

raw Execute commands using Apio packages.

system System tools.

upgrade Check the latest Apio version.可以在apio 的文档中详细阅读这些命令

https://apiodoc.readthedocs.io/en/stable/index.html

安装 apio 及其所需的所有软件包后,将在系统中启用串口和安装 ftdi 驱动程序,需要在管理员模式下打开 Windows cmd 。

然后运行此命令。

apio drivers --ftdi-enable完成后关闭管理员提示。

到目前为止,无论主板是否受 apio 项目支持,都可以使用此命令找出所有受支持的主板的列表。

apio boards --list步骤4.创建第一个项目

现在研究如何创建我们的第一个项目。

现在打开或创建选择的文件夹。

完成后,会显示你想要的位置。

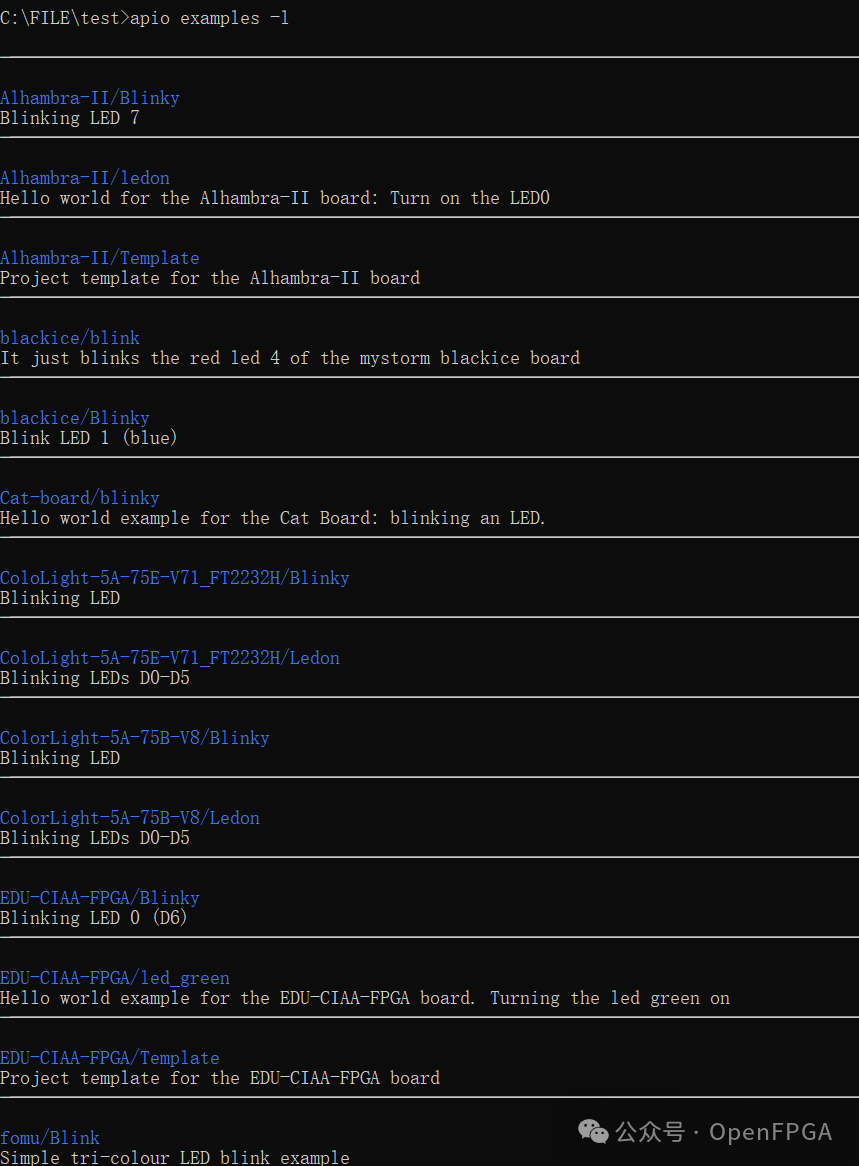

apio 的一大亮点是它自带了所有支持板卡的示例。现在,我们将在 apio 项目中使用内置的示例文件。使用此命令,我们可以列出所有示例。

apio examples -l应该得到这样的列表。

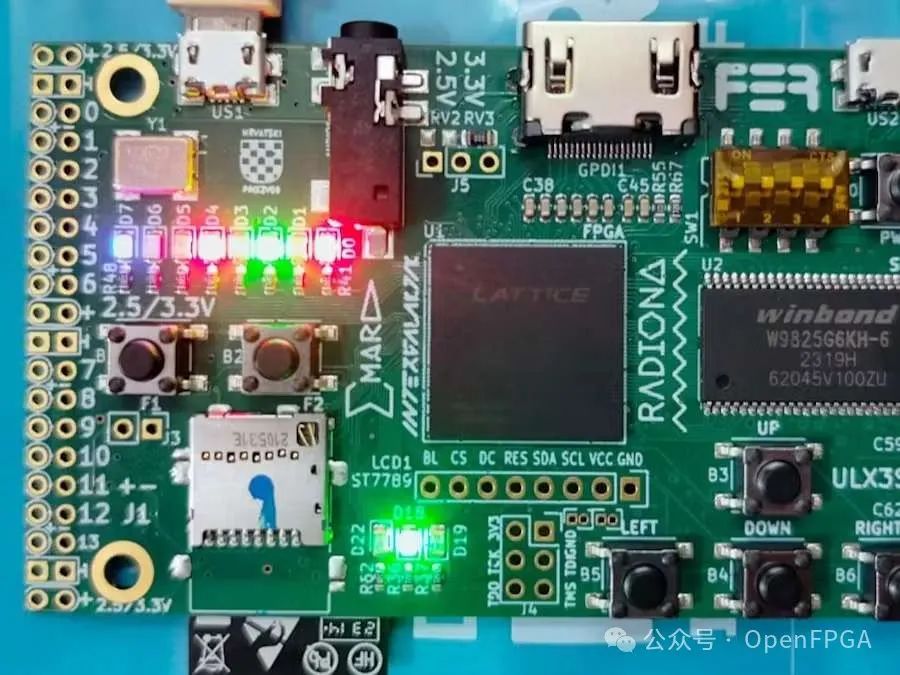

现在我们可以用列表中的示例来对应你的主板。我的主板是 ULX3S- 12f。

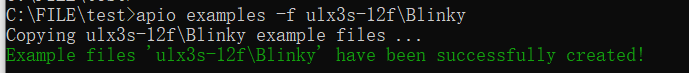

因此我将使用该命令来使用示例,可以根据自己板卡对其进行修改。

apio examples -f ulx3s-12f\Blinky如果示例创建成功,将看到如下输出

该示例文件包含所有需要的 Verilog、Testbench、Simulation 和 Constraints 文件。

现在必须执行以下基本步骤

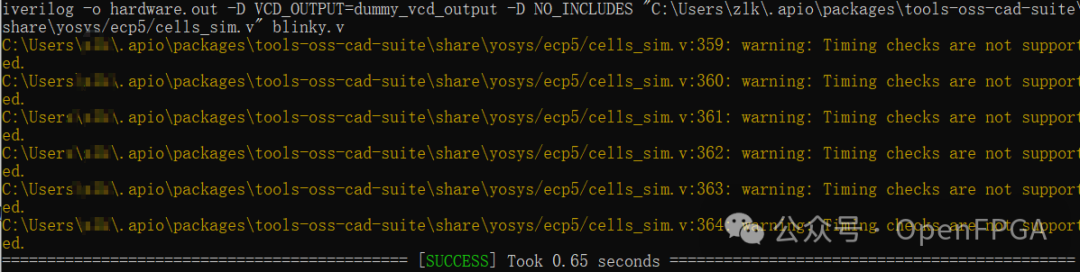

使用命令验证 Verilog 代码

apio verify如果所有语法都正确,将获得如下输出,因为这是一个示例,所以出现语法错误的可能性较小(几乎为 0)。

验证完成后,我们需要仿真这段代码,我们的文件夹必须包含一个测试平台文件。将使用这个命令进行仿真,并使用 Icarus Veriog 和 GTKwave 进行仿真,这样我们就能看到波形了。

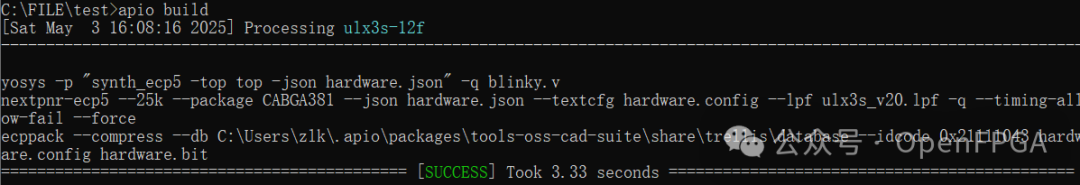

apio sim下一步是为项目构建比特流,使用以下命令完成。

apio build

现在比特流已经生成。我们将把这个比特流上传到我们的开发板,首先我们需要使用这个命令将开发板连接到我们的电脑,然后运行这个命令。

apio upload恭喜您已成功安装开源 apio 项目和工具链,并创建了一个示例项目。可以通过板上的 LED 闪烁来确认。

总结

简单且高效,主要是不需要License,如果你对FPGA这一套EDA比较感兴趣,那么这套工具也可以研究一下。

另外这一套工具其实也是某平台官方源码流出来后魔改的(流传~)。

最后是一些相关参考资料:

https://apiodoc.readthedocs.io/en/stable/index.html

https://github.com/FPGAwars/apio

https://clifford.at/icestorm

https://www.youtube.com/watch?v=gtkQ84Euyww&list=PPSV