- 对应于原文 Multichannel Buffered Serial Port (McBSP)的 2.5.3 Data Clock Generation。

CLKG

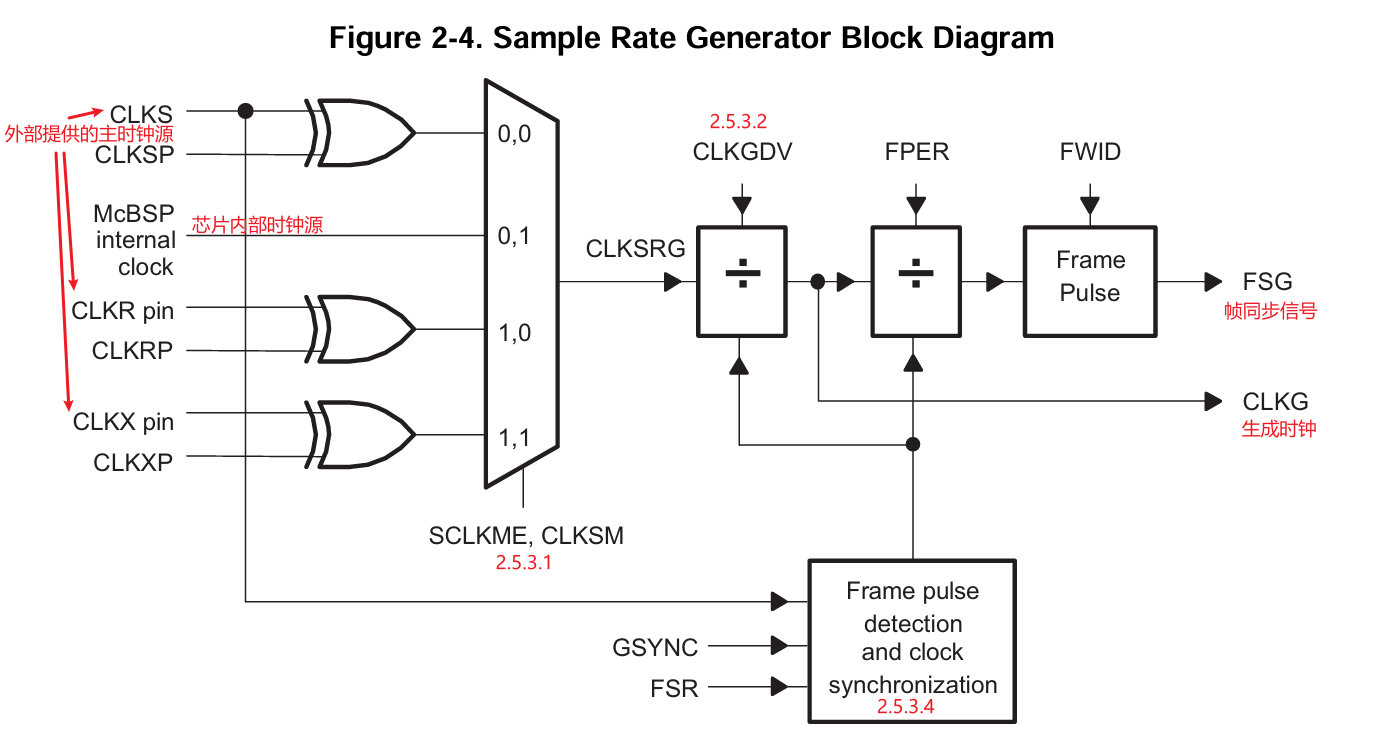

Figure 2-4. Sample Rate Generator Block Diagram

CLKG 是采样率发生器输出的数据位时钟(Data Bit Clock),它被用来控制:

- 数据发送/接收的时钟节奏(即每个数据位在哪个时钟边沿传输)

- 帧同步信号 FSG 的生成时机

- CLKG 是通过对 CLKS 进行分频得到的,具体分频系数由寄存器 CLKGDV 控制。

2.5.3 Data Clock Generation

当接收/发送时钟模式设置为 1(即在引脚控制寄存器(PCR)中设置

CLK(R/X)M = 1)时,数据时钟(CLK(R/X))将由内部采样率发生器输出的时钟 CLKG 驱动。你可以为接收器和发送器选择多种数据位时钟源,包括:采样率发生器的输入时钟可以是内部时钟源,也可以是通过 CLKX、CLKR 或 CLKS 引脚 输入的专用外部时钟源。

在芯片内部,McBSP 的时钟源可通过配置系统配置模块中的 CFGCHIP3 寄存器 中的 ASYNC3_CLKSRC 位 来选择为 PLL0_SYSCLK2 或 PLL1_SYSCLK2。有关 McBSP 内部时钟源的详细信息,请参见 第 2.5.3.1 节。上段提到的采样率发生器的输入时钟源(无论是内部时钟源还是专用外部时钟源),都可以通过一个可编程分频值(采样率发生器寄存器(SRGR)中的

CLKGDV位)进行分频,以驱动 CLKG。无论采样率发生器使用哪种时钟源,CLKSRG 的上升沿(见图 2-4)都会用于生成 CLKG 和 FSG。

2.5.3.1 Input Clock Source Mode: CLKSM and SCLKME 时钟源的选择

采样率发生器的输入时钟信号可以从四种可选的时钟源中选择,这些时钟源由 引脚控制寄存器(PCR)中的 SCLKME 位 和 采样率发生器寄存器(SRGR)中的 CLKSM 位 共同决定,详见 表 2-2。

表 2-2:使用

SCLKME和CLKSM位选择采样率发生器的输入时钟

| PCR 寄存器中的 SCLKME 位 | SRGR 寄存器中的 CLKSM 位 | 采样率发生器的输入时钟源 |

|---|---|---|

| 0 | 0 | CLKS 引脚上的外部输入时钟McBSP |

| 0 | 1 | 内部输入时钟(通常为 LSPCLK) |

| 1 | 0 | CLKR 引脚上的外部输入时钟 |

| 1 | 1 | CLKX 引脚上的外部输入时钟 |

- 各时钟源解释:

| 输入时钟源 | 描述 |

|---|---|

| McBSP 内部输入时钟 | 通常是系统低速外设时钟(LSPCLK),即 DSP 主频的四分之一(SYSCLKOUT / 4)。这是最常用的主模式配置。 |

| CLKS 引脚上的外部输入时钟 | 来自 CLKS 引脚的外部时钟信号,可用于同步到其他系统的主时钟。 |

| CLKX 引脚上的外部输入时钟 | 使用发送时钟引脚 CLKX 上的外部时钟作为采样率发生器的输入。 |

| CLKR 引脚上的外部输入时钟 | 使用接收时钟引脚 CLKR 上的外部时钟作为采样率发生器的输入。 |

2.5.3.2 Sample Rate Generator Data Bit Clock Rate: CLKGDV 频率

第一个分频阶段从输入时钟生成串行数据位时钟。该分频阶段使用一个计数器,该计数器由采样率发生器寄存器(SRGR)中的 CLKGDV 位预加载,并包含分频比值。该阶段的输出是数据位时钟,它通过采样率发生器的输出 CLKG 输出,并作为第二和第三分频阶段的输入。

CLKG 的频率等于采样率发生器输入时钟频率的 1/(CLKGDV + 1)。因此,采样率发生器的输入时钟频率被分频了 1 到 256 之间的某个值。所选择的 CLKGDV 值 必须确保生成的时钟满足设备数据手册中规定的时序要求和限制条件。

当 CLKGDV 的值为奇数或等于 0 时,生成的 CLKG 时钟占空比为 50%。请注意:如果 CLKGDV 是奇数,表示对源时钟进行了偶数分频;如果 CLKGDV 是偶数(设为 2p),则表示对源时钟进行了奇数分频,此时高电平持续时间为 p + 1 个周期,低电平持续时间为 p 个周期。这一点在 示例 2-1、示例 2-2 和 示例 2-3 中有详细说明。

这里省略示例

2.5.3.3 Bit Clock Polarity: CLKSP 触发边沿的类型

- 通过在采样率发生器寄存器(SRGR)中设置 CLKSM = 0,并在引脚控制寄存器(PCR)中设置 SCLKME = 0,可以选择使用**外部时钟(CLKS)**来驱动采样率发生器的时钟分频器。在这种情况下,SRGR 寄存器中的 CLKSP 位 用于选择在 CLKS 的哪一个边沿 上生成采样率发生器的数据位时钟(CLKG)和帧同步信号(FSG)。由于 CLKG 和 FSG 是在 CLKSRG 的上升沿 生成的,因此:

当 CLKSP = 0 时,CLKS 的上升沿 会触发 CLKG 和 FSG 的跳变;

当 CLKSP = 1 时,CLKS 的下降沿 会触发 CLKG 和 FSG 的跳变。

2.5.3.4 Bit Clock and Frame Synchronization 决定是否让 CLKG 和帧同步信号 FSG 与外部帧同步信号(如 FSR)保持相位同步

当选择使用外部时钟 CLKS 来驱动采样率发生器(即在 SRGR 寄存器中设置 CLKSM = 0,并在 PCR 寄存器中设置 SCLKME = 0)时,SRGR 寄存器中的 GSYNC 位 可用于配置 CLKG 相对于 CLKS 的时序关系。

- 当 GSYNC = 1:

- 启用全局同步模式。每次接收到外部帧同步信号(FSR)的上升沿(或下降沿,取决于极性设置)时,会触发 CLKG 和 FSG 的重新对齐。 确保 McBSP 与外部设备(如音频编解码器)之间保持精确的时序同步。

- CLKG 在同步后总是从高电平开始。此时,FPER(帧周期)寄存器的值不再起作用,因为帧周期由外部帧同步脉冲决定。

- 当 GSYNC = 0:

- 关闭全局同步。CLKG 自由运行,不受外部帧同步信号的影响。

- 使用内部设定的 FPER 和 FWID 来生成帧同步信号 FSG。

- 当 GSYNC = 1:

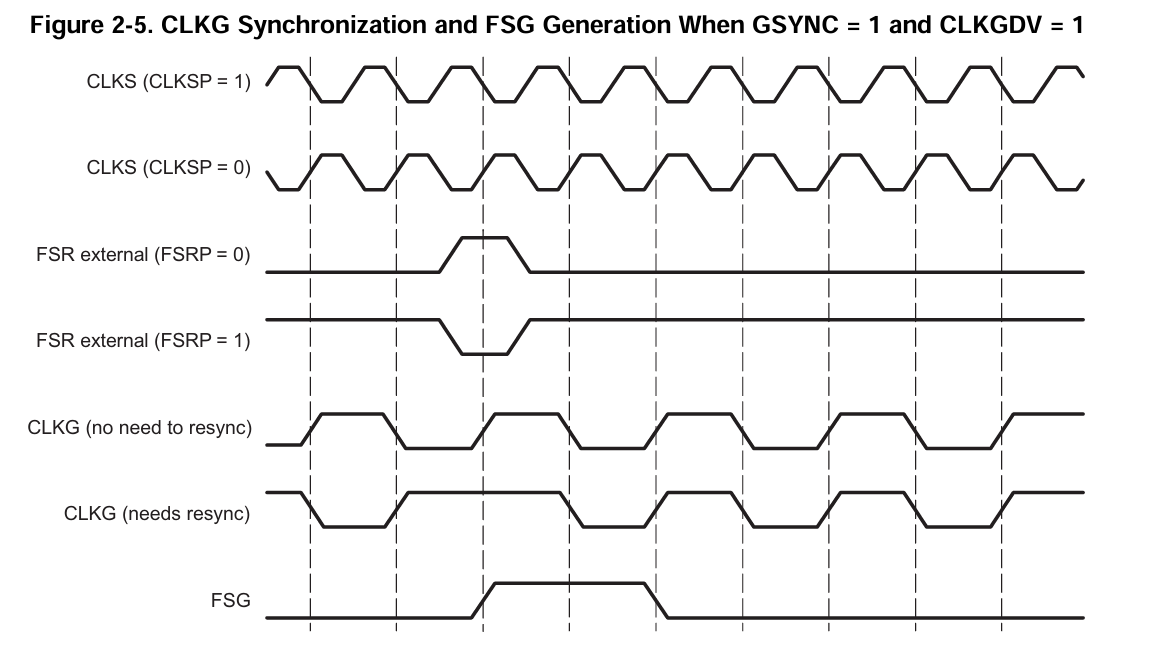

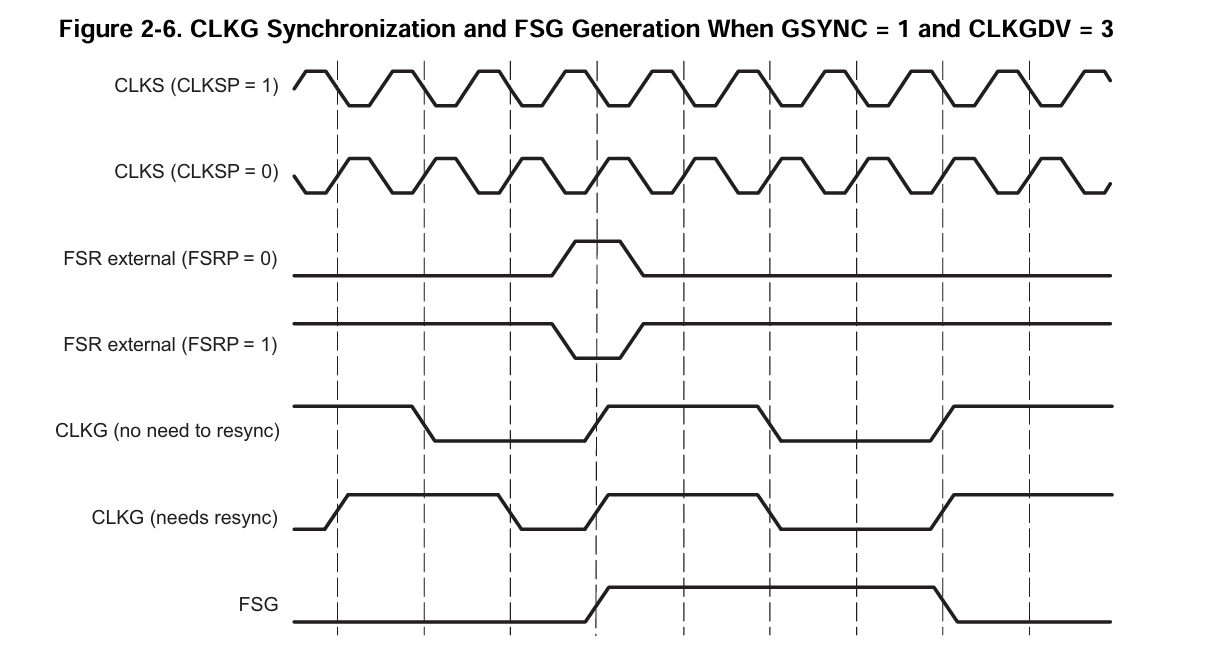

图 2-5 和 图 2-6 展示了在不同 CLKS 和 FSR 极性 配置下的这种操作行为。这些图中假设 FWID = 0,即生成的帧同步信号 FSG 的宽度为 1 个 CLKG 周期。

这些图展示了当 CLKG 初始时与帧同步信号同步且 GSYNC = 1 的情况下,以及当 CLKG 与帧同步信号不同步但 GSYNC = 1 时,CLKG 的变化情况。

Figure 2-5. CLKG Synchronization and FSG Generation When GSYNC = 1 and CLKGDV = 1

下面的三个小标题是对图中元素的说明:

FSRP 的作用

FSRP(Frame Sync Rising Edge Polarity)

是 McBSP 寄存器中的一个配置位,用于设置外部帧同步信号 FSR(接收帧同步)的触发边沿类型。FSR(Frame Sync Receive)

是 McBSP 接收端的帧同步输入引脚。该引脚接收来自外部设备的帧同步信号,用来标识一帧数据的开始。

| FSRP 值 | 触发边沿 | 含义说明 |

|---|---|---|

0 |

上升沿(Rising Edge) | 当 FSR 引脚上出现一个从低到高的跳变时,表示新的一帧开始,并触发同步机制 |

1 |

下降沿(Falling Edge) | 当 FSR 引脚上出现一个从高到低的跳变时,表示新的一帧开始,并触发同步机制 |

CLKG 状态

| 项目 | CLKG (no need to resync) | CLKG (needs resync) |

|---|---|---|

| 中文含义 | 不需要重新同步的 CLKG | 需要重新同步的 CLKG |

| 描述 | CLKG 已与外部帧同步信号(如 FSR)对齐 | CLKG 尚未与帧同步信号对齐 |

| 状态说明 | 当前处于同步模式下,数据传输稳定 | 处于等待同步状态,尚未完成首次同步或同步丢失 |

| 行为变化 | CLKG 按照当前相位继续运行 | CLKG 将被重新对齐,从高电平开始一个新的周期 |

FSG 的作用

FSG 是 Frame Sync Generator(帧同步发生器)的缩写,是 McBSP(多通道缓冲串行端口)模块中的一个内部信号,用于生成帧同步脉冲,标识一帧数据的开始。

在串行通信中(如音频、TDM 等),数据通常以“帧”为单位进行传输。每一帧包含多个数据位(如 16bit 或 32bit),帧同步信号用来告诉接收方:“新的一帧开始了”。

Figure 2-6. CLKG Synchronization and FSG Generation When GSYNC = 1 and CLKGDV = 3

当 GSYNC = 1 时,只要满足以下条件,发送器就可以与接收器同步工作:

- FSX 被配置为由采样率发生器的帧同步信号 FSG 驱动(即在 SRGR 寄存器中设置 FSGM = 1,并在 PCR 寄存器中设置 FSXM = 1)。

- 采样率发生器的时钟 应该驱动发送和接收的数据位时钟(即在 SPCR 寄存器中设置 CLK(R/X)M = 1)。因此,CLK(R/X) 引脚不应由其他任何时钟源驱动。

2.5.3.5 Digital Loopback Mode: DLB

- 略

2.5.3.6 Receive Clock Selection: DLB, CLKRM

表 2-3 展示了串口控制寄存器(SPCR)中的数字回环位(DLB)和引脚控制寄存器(PCR)中的 CLKRM 位如何共同决定接收器所使用的时钟来源。当 数字回环模式(DLB = 1) 启用时,发射器的时钟会驱动接收器。CLKRM 位用于决定 CLKR 引脚是作为输入还是输出使用。

表 2-3. 接收时钟选择(Receive Clock Selection)

| SPCR 中的 DLB 位 | PCR 中的 CLKRM 位 | 接收时钟来源 | CLKR 引脚功能 |

|---|---|---|---|

| 0 | 0 | CLKR 作为外部输入时钟,经过 CLKRP 控制反相处理后用于接收 | 输入。由外部驱动 |

| 0 | 1 | 采样率发生器时钟(CLKG)驱动 CLKR | 输出。由 CLKG 驱动,并根据 CLKRP 设置是否反相后输出 |

| 1 | 0 | 内部发送时钟(CLKX_int)驱动内部接收时钟(CLKR_int),并根据 CLKRP 设置是否反相 | 高阻抗 |

| 1 | 1 | CLKX_int 驱动 CLKR_int,并根据 CLKRP 设置是否反相 | 输出。CLKR(与 CLKX 相同)在输出前根据 CLKRP 设置被反相。 |

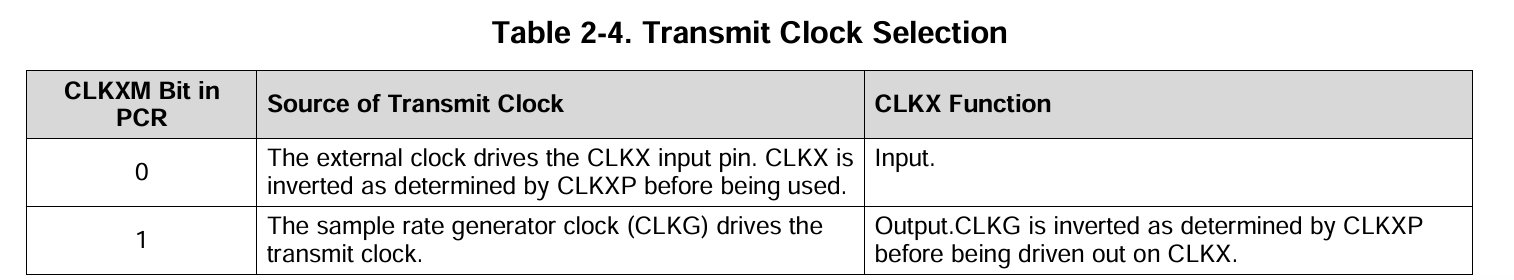

2.5.3.7 Transmit Clock Selection: CLKXM

- 表 2-4 显示了引脚控制寄存器(PCR)中的 CLKXM 位如何选择发送时钟(transmit clock),以及 CLKX 引脚是作为输入还是输出使用。

2.5.3.8 Stopping Clocks

- 略