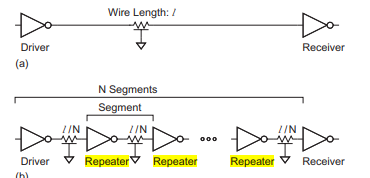

Repeaters

RC延迟与导线长度的关系:

- 导线的电阻(R)和电容(C)都会随着导线长度(l)的增加而增大。

- RC延迟是电阻和电容共同作用导致的信号延迟。由于RC延迟与R和C的乘积有关,因此它会随着导线长度的平方(l²)而增加。

使用中继器(Repeater)降低延迟:

- 为了减少这种延迟,可以将长导线分成N段,并在每段之间插入一个叫做“中继器”的装置(通常是一个反相器或缓冲器)。

- 中继器的作用是主动驱动信号,使信号能够更快地通过下一段导线。

- 每段导线的RC延迟大致与 (l/N)² 成正比。因为总共有N段,所以总的延迟大约是 l² / N。

中继器数量与延迟关系的优化:

- 如果中继器的数量(即分段数N)与导线长度l成正比,那么总的延迟就不再是随l²增长,而是只与l成正比。

- 这样就可以显著改善长导线带来的信号延迟问题。

如何优化中继器(repeater)之间的距离和尺寸,以达到最小的信号传输延迟。

背景设定:

- 使用反相器(inverter)作为中继器可以提高信号驱动能力,从而减少导线上的RC延迟。

- 每个中继器本身也会引入一定的延迟。

- 如果中继器之间间隔太远 → 延迟主要由长导线的RC效应决定;

- 如果中继器之间间隔太近 → 延迟主要由大量中继器本身的延迟累积造成;

- 所以需要在两者之间找到一个平衡点,使总延迟最小。

参数定义:

一个“单位大小”的反相器具有:

- 电阻 R

- 栅极电容 C

- 扩散电容 Cp_inv(即输出端口的寄生电容)

导线每单位长度的参数为:

- 电阻 Rw

- 电容 Cw

插入的中继器是“W倍单位大小”的反相器。也就是说,中继器的尺寸可以放大 W 倍来增强驱动能力。

分析思路:

延迟来源分解:

- 中继器输入到输出的延迟 = 驱动器(前一级)通过导线给中继器输入端的电容充电的时间。

- 中继器输出驱动下一段导线时,也要对导线电容以及下一级中继器的输入电容进行充放电。

中继器尺寸的影响:

- 如果中继器尺寸变大(W增大),它的内部电阻会减小,驱动能力增强,延迟降低;

- 但同时它的输入电容(C × W)也会增加,导致前一级驱动它时产生更多延迟;

- 因此,中继器尺寸也需要优化,不能太大也不能太小。

目标:

- 找到最优的中继器插入间隔(即每段导线的长度);

- 找到最优的中继器尺寸放大倍数 W;

- 使得整个路径上的信号传播延迟最小。

总结:

为了最小化长导线引起的信号延迟,可以通过插入适当数量、适当尺寸的中继器来分段驱动导线。这涉及到两个关键参数的优化:

- 中继器之间的距离(导线分段长度)

- 中继器的尺寸放大倍数 W

公式(编号对应CMOS VLSI Design A Circuits and Systems Perspecctive)

| 公式编号 | 公式文本形式 (纯文本) | 新变量名称及解释 | 公式内容描述 | 影响最大的几个变量及其关系 |

|---|---|---|---|---|

| (6.26) | t_pd = N * [ R / W * ( (C_w * l / N) + CW(1 + p_inv) ) + Rw * (l/N) * ( (C_w / 2* (l/N)) + C*W ) ] | t _ p d t\_{pd} t_pd: 传播延迟 (总延迟)。<br> N N N: 重复器(Repeater/Inverter)的数量。<br> R R R: 每个重复器的输出电阻 (Effective resistance of each repeater)。<br> C _ w C\_w C_w: 单位长度导线电容 (Capacitance per unit length of wire)。<br> C C C: 每个重复器的输入电容 (Input capacitance of each repeater)。<br> W W W: 重复器的宽度,通常指驱动晶体管的宽度。<br> p _ i n v p\_{inv} p_inv: 反相器延迟因子,通常与扇出(fanout)有关,描述反相器相对于其内部RC常数的延迟倍数。对于FO4(fanout-of-4)反相器,通常 p _ i n v a p p r o x 0.5 p\_{inv} \\approx 0.5 p_invapprox0.5 (对于折叠晶体管)。<br> C _ s w C\_{sw} C_sw: 单位长度导线开关电容 (Switching capacitance per unit length of wire),这可能是导线与衬底或相邻导线之间的边缘效应电容。 | 这是重复导线的Elmore延迟模型,表示一个具有 N N N个重复器的互连线的总传播延迟。它包含两部分:重复器本身的延迟和驱动导线的延迟。 | N (重复器数量): 复杂关系,存在最佳值,N过小或过大都会增加延迟。<br> R (重复器电阻): 成正比。<br> C_w (单位长度导线电容): 成正比。<br> C (重复器输入电容): 成正比。<br> W (重复器宽度): 通常W越大R越小C越大,存在一个权衡。<br> R_w (单位长度导线电阻): 存在于R项中,与延迟呈正比。 |

| (6.27) | l / N = sqrt( (2 * R * C * (1 + p_inv)) / (R_w * C_w) ) | l l l: 导线总长度 (Total wire length)。<br> R _ w R\_w R_w: 单位长度导线电阻 (Resistance per unit length of wire)。 | 这个公式表示在实现最小总延迟时,每段导线的最佳长度 ( l / N l/N l/N)。它通过对(6.26)式关于 N N N和 W W W求导并优化得到,平衡了重复器本身的延迟和驱动导线的延迟。 | R (重复器电阻): 每段长度与R的平方根成正比。<br> C (重复器输入电容): 每段长度与C的平方根成正比。<br> R_w (单位长度导线电阻): 每段长度与R_w的平方根成反比。<br> C_w (单位长度导线电容): 每段长度与C_w的平方根成反比。 |

| (6.28) | l / N = 0.77* sqrt( FO4 / (R_w *C_w)) | FO4: FO4反相器的延迟,这里假设是 5 R C 5RC 5RC。 | 这是(6.27)的简化形式,假设FO4反相器延迟为 5 R C 5RC 5RC,并且 p _ i n v = 0.5 p\_{inv} = 0.5 p_inv=0.5(对于折叠晶体管)。这个常数 0.77 0.77 0.77是经过经验优化或简化得到的。 | FO4 (FO4反相器延迟): 平方根成正比。<br> R_w (单位长度导线电阻): 每段长度与R_w的平方根成反比。<br> C_w (单位长度导线电容): 每段长度与C_w的平方根成反比。 |

| (6.29) | t_pd / l = (2 + sqrt(2 * (1 + p_inv))) * sqrt(R * C * R_w * C_w) = 1.67 * sqrt(FO4 * R_w * C_w) | 这个公式表示在最佳重复器配置下,每单位长度的重复导线的最小延迟。它表明了在理想情况下,延迟与导线长度的平方根成正比(这是著名的Elmore延迟的平方根定律)。 | R (重复器电阻): 单位长度延迟与R的平方根成正比。<br> C (重复器输入电容): 单位长度延迟与C的平方根成正比。<br> R_w (单位长度导线电阻): 单位长度延迟与R_w的平方根成正比。<br> C_w (单位长度导线电容): 单位长度延迟与C_w的平方根成正比。<br> FO4 (FO4反相器延迟): 单位长度延迟与FO4的平方根成正比。 | |

| (6.30) | W = sqrt( (R * C_w) / (R_w * C) ) | 为了实现上述最小延迟,该公式给出了反相器应使用的nMOS晶体管的宽度。这个宽度是优化重复器性能的关键参数之一。 | R (重复器电阻): 重复器宽度与R的平方根成正比。<br> C (重复器输入电容): 重复器宽度与C的平方根成反比。<br> R_w (单位长度导线电阻): 重复器宽度与R_w的平方根成反比。<br> C_w (单位长度导线电容): 重复器宽度与C_w的平方根成正比。 | |

| (6.31) | E / l = C_w + NWC*(1 + p_inv) = C_w * ( 1 + sqrt( (1 + p_inv) / 2 ) ) * V_DD^2 = 1.87 * C_w * V_DD^2 | E E E: 传输一个比特所需的能量 (Energy to send a bit).<br> V _ D D V\_{DD} V_DD: 电源电压 (Supply voltage). | 这个公式表示每单位长度传输一个比特所需的能量。在优化延迟的重复器配置下,能量主要由导线电容和重复器电容的充放电决定。最终简化式说明,对于优化后的重复导线,能量消耗主要与单位长度导线电容和电源电压的平方成正比。 | C_w (单位长度导线电容): 成正比。<br> V_DD (电源电压): 成二次方正比。 |

📌 关键术语中英对照表(便于快速查阅)

| 中文术语 | 英文术语 |

|---|---|

| 中继器 | Repeater |

| 反相器 | Inverter |

| 扩散电容 | Diffusion Capacitance |

| 单位长度线电容 | Unit-length wire capacitance |

| 折叠晶体管 | Folded transistor |

| 非反相中继器 | Noninverting repeater |

| 延迟 | Delay |

| 能量-延迟乘积 | Energy-Delay Product (EDP) |

| 导线 | Wire |

| 段 | Segment |

| 尺寸倍数 | Size multiple |

| 三态总线 | Tristate bus |

| 分布式总线 | Distributed bus |

| 点对点通信 | Point-to-point communication |

| 方向性 | Directionality |

导线延迟与能耗优化之间的权衡关系,以及中继器设计对电路性能的影响。

1. 延迟与能量的折中(EDP 最小点)

- 在最优驱动尺寸和中继器间距附近,延迟随距离和驱动尺寸的变化曲线比较平坦。这意味着:

- 如果允许延迟略微增加,可以显著降低能量消耗。

- 当达到能量延迟积(EDP, Energy-Delay Product)最小点时:

- 每段导线长度变为原来的 1.7 倍。

- 驱动器宽度减小到原来的 0.6 倍。

- 延迟增加了 14%,但中继器只使总能量增加 30%(相比没有中继器的情况)。

- 对于 Example 6.10 中的参数:

- 最优 EDP 点出现在:

- 中继器间距约为 0.8 mm

- 驱动器宽度为 11 Rm(即 110x 单位宽度)

- 能量降低至 0.26 pJ/mm

- 延迟为 47 ps/mm

- 最优 EDP 点出现在:

- 缺点是:由于导线段更长,系统更容易受到噪声干扰。

2. 中继器类型对设计的影响

- 使用反相中继器inverting repeaters会带来一些设计复杂性:

- 必须确保每根线上有偶数个中继器,以保证信号极性不变;

- 或者接收端逻辑要能处理反转后的输入信号。

- 为了避免这个问题,有些设计师使用缓冲器结构(两个反相器串联)代替单个反相器:

- 这样不会改变信号极性;

- 但会引入额外的延迟。

- 缓冲器中的第一个反相器可以做得较小(

W1),因为它对前级导线的负载更轻; - 第二个反相器可以做得更大(

W2 = k × W1),以更好地驱动下一段导线;- 当

p_inv = 0.5时,最佳比例因子k = 2.25。

- 当

- 使用缓冲器后,中继器之间的最优间距也会相应增大(具体公式见练习题 6.6)。

总结

该段内容强调了在实际高速数字电路设计中,如何在延迟、能量、噪声和设计复杂度之间进行权衡:

- 在延迟略有上升的情况下,可以显著节省能量;

- 使用缓冲器结构虽然解决了信号极性问题,但会增加延迟;

- 中继器的设计需要综合考虑驱动强度、段长、噪声容忍度和功耗等多方面因素。

公式

由于图片中没有明确给出所有变量的定义,我将根据集成电路设计中的常见惯例进行推断和解释。

| 公式编号 | 公式文本形式 (纯文本) | 新变量名称及解释 | 公式内容描述 | 影响最大的几个变量及其关系 |

|---|---|---|---|---|

| (6.33) | l / N = sqrt( (2 * R * C * (k + (1/k) + 2 * p_inv)) / (R_w * C_w) ) = 1.22 * FO4 / sqrt(R_w * C_w) | l l l: 导线总长度 (Total wire length)。<br> N N N: 重复器(Repeater/Inverter)的数量。<br> R R R: 每个重复器的输出电阻 (Effective resistance of each repeater)。<br> C C C: 每个重复器的输入电容 (Input capacitance of each repeater)。<br> k k k: 重复器(缓冲器)的扇出比(或级联比),表示相邻两级重复器之间的尺寸比例或驱动能力比例。通常用于优化多级缓冲器的延迟。<br> p _ i n v p\_{inv} p_inv: 反相器延迟因子,通常与扇出(fanout)有关,描述反相器相对于其内部RC常数的延迟倍数。<br> R _ w R\_w R_w: 单位长度导线电阻 (Resistance per unit length of wire)。<br> C _ w C\_w C_w: 单位长度导线电容 (Capacitance per unit length of wire)。<br> FO4: FO4反相器的延迟,这里假设是 5 R C 5RC 5RC。 | 这个公式表示在优化延迟时,每段导线的最佳长度 ( l / N l/N l/N)。它考虑了重复器(缓冲器)的级联比 k k k,以进一步优化性能。等式右侧是简化后的经验公式,使用FO4延迟来表示。 | R (重复器电阻): 每段长度与R的平方根成正比。<br> C (重复器输入电容): 每段长度与C的平方根成正比。<br> k (级联比): 影响复杂,存在最佳k值。<br> R_w (单位长度导线电阻): 每段长度与R_w的平方根成反比。<br> C_w (单位长度导线电容): 每段长度与C_w的平方根成反比。<br> FO4 (FO4反相器延迟): 成正比。 |

| (6.34) | t_pd / l = 1.81 * sqrt(FO4 * R_w * C_w) | t _ p d t\_{pd} t_pd: 传播延迟 (总延迟)。 | 这个公式表示在最佳重复器(缓冲器)配置下,每单位长度的重复导线的最小延迟。常数 1.81 1.81 1.81是经过优化和简化后得到的经验值。 | FO4 (FO4反相器延迟): 单位长度延迟与FO4的平方根成正比。<br> R_w (单位长度导线电阻): 单位长度延迟与R_w的平方根成正比。<br> C_w (单位长度导线电容): 单位长度延迟与C_w的平方根成正比。 |

| (6.35) | W_1 = W / sqrt(k) , W_2 = W * sqrt(k) | W _ 1 W\_1 W_1: 第一级(或输入级)晶体管的宽度。<br> W _ 2 W\_2 W_2: 第二级(或输出级)晶体管的宽度。<br> W W W: 基础晶体管宽度,可能是指某个参考尺寸或未优化的宽度。<br> k k k: 重复器(缓冲器)的扇出比(或级联比)。 | 这些公式给出了在优化延迟时,不同级重复器(或缓冲器)中晶体管的宽度。通常,多级缓冲器会按照一定的比例(如 k k k)进行尺寸递增,以有效地驱动大负载。 | k (级联比): 影响晶体管宽度,W1与k的平方根成反比,W2与k的平方根成正比。<br> W (基础宽度): 成正比。 |

| (6.36) | E / l = 2.2 * C_w * V_DD^2 | E E E: 传输一个比特所需的能量 (Energy to send a bit).<br> V _ D D V\_{DD} V_DD: 电源电压 (Supply voltage). | 这个公式表示每单位长度传输一个比特所需的能量。常数 2.2 2.2 2.2是经过优化和简化后得到的经验值。它表明,对于优化后的重复导线,能量消耗主要由单位长度导线电容和电源电压的平方决定。 | C_w (单位长度导线电容): 成正比。<br> V_DD (电源电压): 成二次方正比。 |

非反相中继器(noninverting repeaters)与反相中继器(inverting repeaters)在性能、面积和设计复杂性方面的差异,导线方向性对通信结构的影响。

1. 非反相中继器的延迟代价

- 使用非反相中继器(即缓冲器,由两个反相器组成)时,每单位长度的导线延迟仅比使用单个反相中继器增加约8%。

- 虽然引入了额外的延迟,但这种代价相对较小。

2. 中继器数量减少带来的好处

- 因为非反相中继器允许更长的段长(见前文关于 EDP 最小点的分析),所以所需的中继器数量大约只有原来的三分之二。

- 这带来了以下优势:

- 简化布局规划(floorplanning):因为需要放置的中继器更少,所以在芯片上寻找合适位置变得更简单;

- 布线资源压力减小:减少了中继器占用的空间和布线干扰。

3. 面积与功耗略有上升

- 虽然中继器数量减少,但由于每个非反相中继器包含两个反相器,因此:

- 总面积略增;

- 总功耗也略有上升;

- 但这些增加通常是可以接受的,尤其是在考虑了布局便利性和信号完整性之后。

4. 延迟对中继器间距不敏感

- 整体延迟对中继器之间的距离变化并不敏感,也就是说:

- 即使稍微增加中继器间距,整体延迟不会显著上升;

- 因此,为了便于布局,可以合理地增加段长,从而减少中继器数量,而不必担心严重的性能损失。

5. 中继器导致导线具有方向性

- 中继器本质上是单向器件,它们只能在一个方向上传播信号;

- 因此,使用中继器的导线就变成了有方向性的导线;

- 这带来了一些限制:

❌ 对双向总线和三态总线的影响:

- 双向总线(bidirectional busses) 和 分布式三态总线(distributed tristate busses):

- 无法使用简单的中继器;

- 因为中继器不能处理反向传播的信号;

- 所以这些类型的总线速度较慢;

- ✅ 相对而言,点对点、单向通信结构(point-to-point unidirectional communication)更适合使用中继器;

- 可以充分利用中继器带来的延迟优化;

- 更适合现代高性能数字系统的设计趋势(如高速串行链路、片上网络等)。

总结

这段话的核心思想是:

在实际电路设计中,使用非反相中继器虽然会略微增加延迟和功耗,但能显著简化布局、减少中继器数量,同时避免信号极性反转的问题。由于整体延迟对中继器间距不敏感,适当增加段长是一个合理的选择。然而,中继器的使用也意味着导线变得有方向性,这使得传统的双向或三态总线不再适用,从而推动了现代系统向点对点、单向通信架构的发展。