一、知识准备

1.一些术语,缩写和概念:

1)ZYNQ全称:ZYNQ7000 All Pgrammable SoC

2)SoC:system on chips(片上系统),对比集成电路的SoB(system on board)

3)ARM:处理器架构,基于RISC(精简指令集),对比X86架构基于CISC(复杂指令集)

4)ASIC:Application-specific Integrated Circuit(专用集成电路);

5)SOPC:System-on-Programmable-Chip(可编程片上系统);

6)APSOC:All-Programmable-SoC(全可编程片上系统)——软件(arm)和硬件(门阵列)都可编程,ZYNQ就属于APSOC;

2.常见可编程逻辑器件

2.1 CPLD

全称Complix Pragrammable Logic Device,CPLD通常由几个较小的、具有高度并行处理能力的逻辑块组成。每个逻辑块包含多个逻辑门、触发器和其他数字电路。 CPLD的结构比较“扁平化”,即它们的内部连接较为固定,支持逻辑操作的资源比较有限。它的内部连接较简单,且配置时需要对电路进行一定的优化。 CPLD的最大特点是它的逻辑块之间是通过专用的可编程互联网络连接起来的。

CPLD性能相对较低,适合需要低功耗和低复杂度的应用。CPLD的工作速度通常较慢,逻辑容量也较小(通常只有几千到几十千个逻辑门)。 由于其资源有限,CPLD通常用于一些小型的控制应用、简单的逻辑运算、状态机、解码器等。

2.2 FPGA

全称Filed Programable Gate Array,FPGA采用的是更加复杂的结构,通常由成千上万个较小的逻辑单元(称为逻辑块)组成,每个逻辑块可以执行基本的逻辑运算。这些逻辑块通过更为复杂的路由网络连接起来,支持更大的设计和更复杂的功能。 FPGA支持更灵活的连接和更高的并行度,可以实现更多的定制化电路,适合更复杂的应用。

FPGA一般有可编程IO,可编程逻辑单元,底层嵌入功能单元,嵌入式Block RAM,布线资源和硬核,其中可编程IO、嵌入式Block RAM和可编程逻辑单元在不同的FPGA芯片中只有数量上的区别,而底层嵌入功能单元是一些常用的功能单元,不同FPGA芯片上其数量和功能都有所不同,硬核也是具有特定功能的单元,其功能是专用的功能,不是所有FPGA芯片都有硬核。

FPGA性能非常高,能够处理极为复杂的逻辑操作,支持的逻辑容量非常大,通常有数百万个逻辑门或更多。 FPGA广泛应用于要求高速运算和大量并行计算的领域,如视频处理、图像处理、通信系统、数据加速等。

二、ZYNQ解析

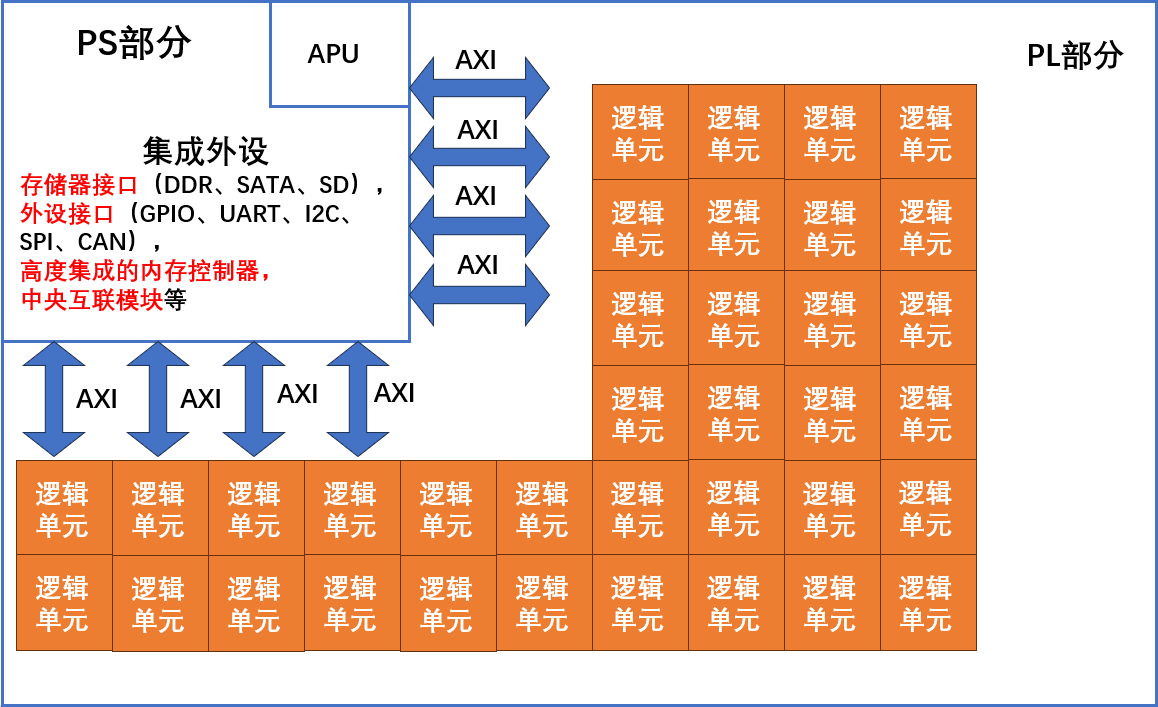

ZYNQ实际是一种APSOC,它是组合了一个双核ARM Cortex-A9处理器(PS部分)和一个传统的FPGA门阵列逻辑部件的片上系统(PL部分)。ARM架构的处理器赋予了它软件编程的能力,可以运行例如linux这样的完整的操作系统,而FPGA门阵列则赋予了其硬件编程的能力可以构建各种定制化外设电路,PS和PL两个部分都可以单独使用,也可以结合起来使用(通过AXI接口)。

结构示意图如下:

1. PS(processing system):

PS部分主要包含搭载双核ARM架构处理器的APU以及一些外部集成电路;

1.1 APU

APU中的部分常用资源说明如下:

①两个ARM Cortex-A9处理器:核心处理器;

②两个浮点运算单元(FPU):进行浮点运算;

③两个并行运算引擎NEON Engine:常用于图像中像素点的并行处理;

④两个存储管理单元MMU;

⑤两套一级缓存(cache):每一套都包含一个32K的指令cache(I-cache)和一个32K的数据cache(D-cache);

⑥一个512K的共用二级缓存和一个片上存储(OCM)互联:这两个部分都通过SCU(snoop Controller Unit)一致性控制单元接收两个处理器的控制;

⑦一个中断控制器(GIC);

⑧一个直接内存访问(DMA):允许外部设备(如硬盘、网络接口、图形处理单元(GPU)、音频设备等)直接与系统内存(RAM)交换数据,而不需要通过中央处理器(CPU)的干预。

1.2外部集成电路:

外部集成电路主要包含以下内容:

① 中央互联:不同组件之间的通信骨架,负责将各个模块有效连接起来,并管理它们之间的数据流,主要包括:处理器核心与外设之间的互联、CPU和外设对内存访问的管理、总线仲裁;

② 与外界互联的接口(USB、SD/SDIO、GPIO、UART等)以及可配置映射的多功能输入输出接口(MIO,即直接与外设进行通信的引脚共54个);

③ 复位管理和时钟生成器;

④ 其他互联;

2.PL(Programmable Logic):

PL部分可以看作是一个FPGA模块,这部分允许用户通过硬件描述语言(如VHDL或Verilog)定义硬件电路,实现自定义的逻辑功能。PL是高度可编程的,能够为特定应用提供极大的灵活性。

PL部分包含以下内容:

① 可扩展引脚(EMIO):用于PS的MIO不够时进行扩展,也可以使用这些EMIO与ps进行一些交互;

② XADC数模转换接口:外设通过该接口可直接访问XADC硬核;

③ DMA接口:实现PL直接访问PS的DMA模块;

④ AXI接口;

⑤ 可编程逻辑单元;

3.AXI接口

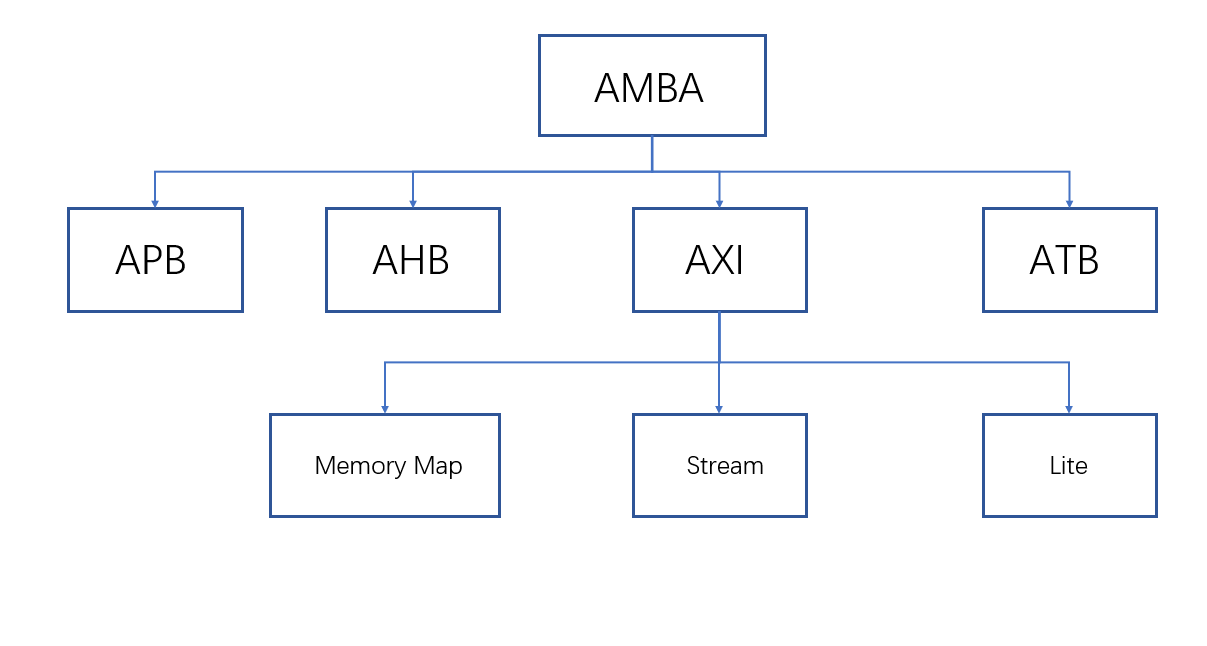

AXI(Advanced Extensible Interface)接口是一种由 ARM 公司开发的高性能、可扩展的 总线协议,它是AMBA总线的一部分,主要用于高带宽、低延迟的数据传输。它被广泛应用于 ARM 处理器和各种嵌入式系统中的数据传输,特别是在 Zynq 等集成了 ARM 处理器 和 FPGA 的 SoC(System on Chip)系统中。

PS和PL的协同工作就依赖于该接口,AXI接口包含通用接口(GP接口,General purpose interface),加速器一致接口(ACP接口——Accelerator Coherency Port,S_AXI_ACP),高性能接口(HP接口——High Performance interface,S_AXI_HP)三个部分,其中GP接口又有主(master)接口M_AXI_GP[1:0]和从(slave)接口S_AXI_GP[1:0]分别承担发起通信和响应通信的作用,这里M和S都表示PS部分的角色是主还是从;ACP接口直接访问SCU实现PL对PS中的OCM和二级cache的通信,通过ACP接口可以使PL访问OCM和二级cache的速度和CPU访问这两个模块的速度相当;HP接口连接PS的数据存储区,其高性能体现在每一个HP接口都有一个FIFO缓冲区,且接口的数据传输速度和吞吐量都很大。在HP接口通信和ACP通信过程中都是PL做主机,PS做从机。

AMBA总线的框架结构如下图所示:

其中Memory Map、Stream和Lite是不同的AXI类别属于AMBA4.0分别表示存储映射、数据流、轻量化访问,而AMBA3.0只有一种AXI。