Camera Sensor LVDS与SubLVDS接口及协议深度解析

一、物理层核心技术

1. LVDS(低压差分信号)

电气特性 :

- 差分电压 :350mV恒定摆幅(最小247mV,最大454mV)

- 共模电压 :1.2V ±0.1V

- 终端匹配 :100Ω电阻(精度±1%)

- 电流驱动 :3.5mA恒流源

- 传输模型 :

math

V_{diff} = (V_{D+}) - (V_{D-}) = 350mV_{pp}

拓扑结构 :

- 点对点直连(1:1)

- 最大传输距离:10米(CAT6A电缆)

- 支持通道数:4-28对差分线

2. SubLVDS(亚低压差分信号)

进化亮点 :

- 电压摆幅降低43%:350mV → 200mV

- 功耗降低40%:0.4mW/通道(计算公式:P = V²/R)

- 共模电压兼容现代低功耗芯片

二、协议层架构解析

1. 数据帧结构

典型时序参数 (以720p@60fps为例):

| 参数 | 值 | 说明 |

|---|---|---|

| 帧周期 | 16.7ms | 1/60秒 |

| 行周期 | 29.6μs | 包含消隐区 |

| 像素时钟 | 74.25MHz | 1280×720×60 |

| VSYNC脉宽 | 5行时间 | 帧同步信号 |

| HSYNC脉宽 | 128像素时间 | 行同步信号 |

2. 同步机制

同步模式对比 :

| 模式 | 信号线 | 优点 | 缺点 |

|---|---|---|---|

| 独立同步 | VSYNC+HSYNC | 简单直观 | 增加2根信号线 |

| 嵌入式同步 | 数据通道(SAV/EAV)) | 减少布线 | 需要编解码器 |

| 混合模式 | VSYNC+数据嵌入 | 平衡方案 | 设计复杂 |

三、工业应用场景分析

1. 机器视觉系统(Basler ace方案)

关键参数 :

- 分辨率:2448×2048

- 帧率:30fps

- 位深:12-bit

- 带宽计算:2448×2048×12×30 ≈ 1.8Gbps

- 接口:8对LVDS通道

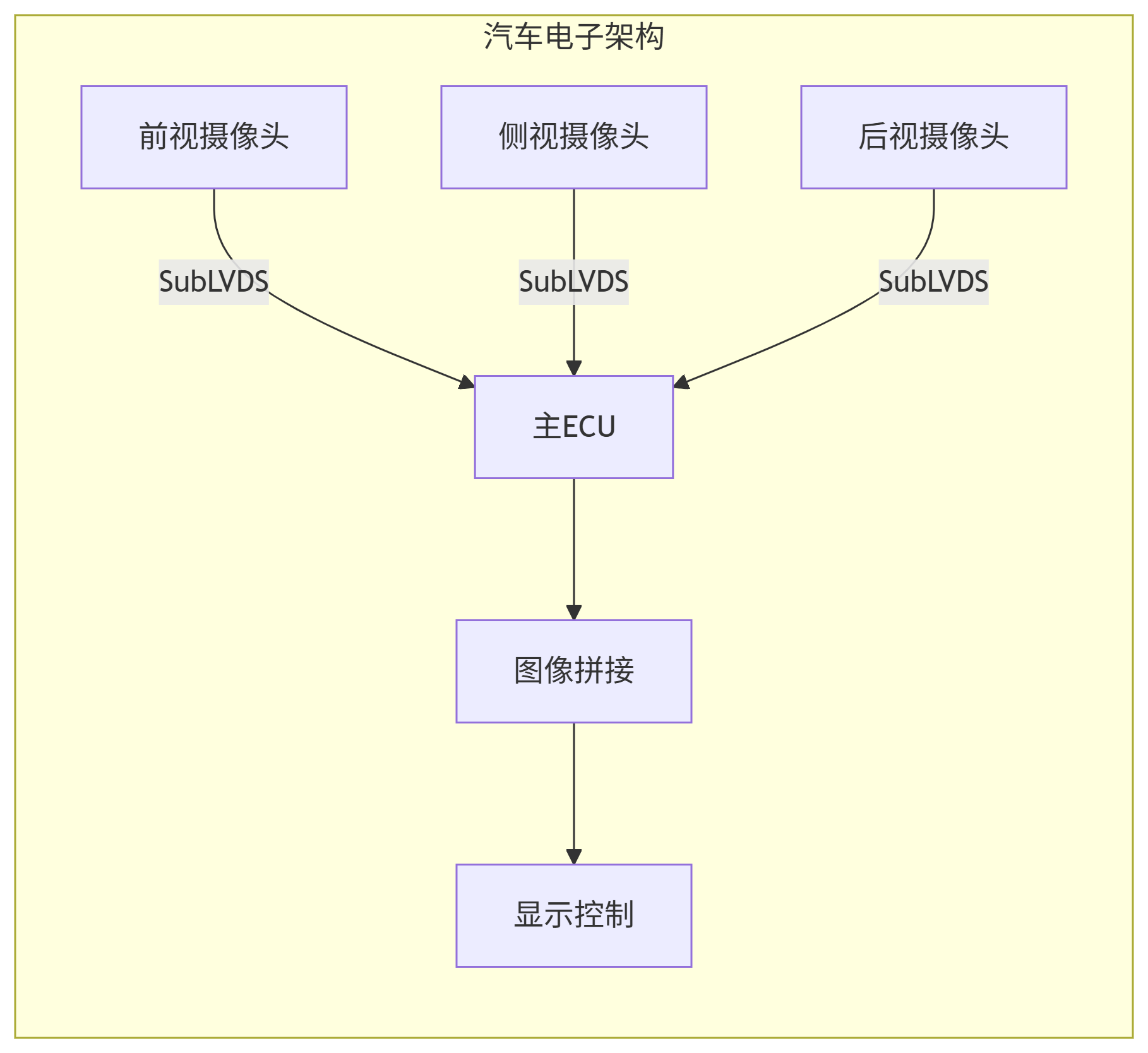

2. 汽车环视系统

设计优势 :

- 4路720P@30fps总功耗<2W

- -40℃~105℃宽温域工作

- 抗电磁干扰能力:30dB CMNR

- 传输距离:15米无中继

四、驱动开发与FPGA实现

1. Linux V4L2驱动框架

c

// LVDS接收器初始化

struct v4l2_subdev *sd;

v4l2_subdev_init(sd, &lvds_ops);

// 设置格式

struct v4l2_mbus_framefmt fmt = {

.width = 1280,

.height = 720,

.code = MEDIA_BUS_FMT_SGRBG12_1X12,

};

v4l2_subdev_call(sd, pad, set_fmt, NULL, &fmt);

// 启动流传输

struct v4l2_subdev_video_ops *video = sd->ops->video;

video->s_stream(sd, 1);

2. FPGA采集逻辑(Verilog)

verilog

module lvds_receiver(

input [3:0] lvds_p, // LVDS+

input [3:0] lvds_n, // LVDS-

input clk_ref, // 200MHz参考时钟

output [11:0] pixel // 12-bit像素输出

);

genvar i;

generate

for (i=0; i<4; i=i+1) begin

IBUFDS #(.DIFF_TERM("TRUE")) ibuf (

.I(lvds_p[i]),

.IB(lvds_n[i]),

.O(lvds_data[i])

);

IDDR #(.DDR_CLK_EDGE("SAME_EDGE")) iddr (

.Q1(data_even[i]),

.Q2(data_odd[i]),

.C(clk_ref),

.CE(1'b1),

.D(lvds_data[i]),

.R(1'b0),

.S(1'b0)

);

end

endgenerate

assign pixel = {data_even, data_odd}; // 合并双沿数据

endmodule

五、与MIPI CSI-2的对比分析

| 维度 | LVDS/SubLVDS | MIPI CSI-2 | 优势场景 |

|---|---|---|---|

| 协议开销 | 0% | 10-15% | 实时控制 |

| 传输延迟 | <10ns | 50-100ns | 工业自动化 |

| 开发难度 | FPGA直采 | 需PHY芯片 | 快速原型 |

| 成本 | $0.5/通道 | $1.2/Lane | 成本敏感型 |

| 传输距离 | 15米 | 0.3米 | 分布式系统 |

| 抗干扰性 | 30dB CMNR | 25dB CMNR | 工业环境 |

六、未来发展趋势

1. 技术演进路线

2. 替代技术分析

- SLVS-EC :索尼专有协议,速率达6Gbps

- A-PHY :开放标准,支持15米@16Gbps

- HDBaseT :基于以太网的替代方案

LVDS与SubLVDS作为工业视觉和汽车电子的骨干技术,凭借其卓越的抗干扰能力和传输可靠性,在严苛环境应用中持续发挥不可替代的作用。随着A-PHY等新技术的崛起,掌握多协议兼容设计能力将成为工程师的核心竞争力。