文章目录

一、本文知识覆盖范围

1、概述

计算机系统组成是计算机科学的基础知识,它帮助我们理解计算机是如何工作的,以及各个组件如何协同工作来完成复杂的计算任务。掌握这些知识对于:

- 系统架构设计:在构建大型软件系统时,理解硬件特性有助于优化系统性能

- 性能调优:了解存储层次、总线结构等有助于识别性能瓶颈

- 技术选型:根据应用场景选择合适的硬件配置和软件架构

- 问题诊断:当系统出现性能问题时,能够从硬件层面分析原因

2、知识体系概览

| 知识模块 | 具体内容 | 学习重点 |

|---|---|---|

| 计算机系统基础 | 硬件组成、软件分类、系统架构 | 理解各组件功能及相互关系 |

| 冯·诺依曼体系结构 | 五大组成部分、工作原理、数据流向 | 掌握计算机基本工作原理 |

| 存储系统 | 层次化存储、局部性原理、缓存机制 | 理解存储性能优化原理 |

| 总线系统 | 总线分类、传输控制、性能特点 | 掌握数据传输机制 |

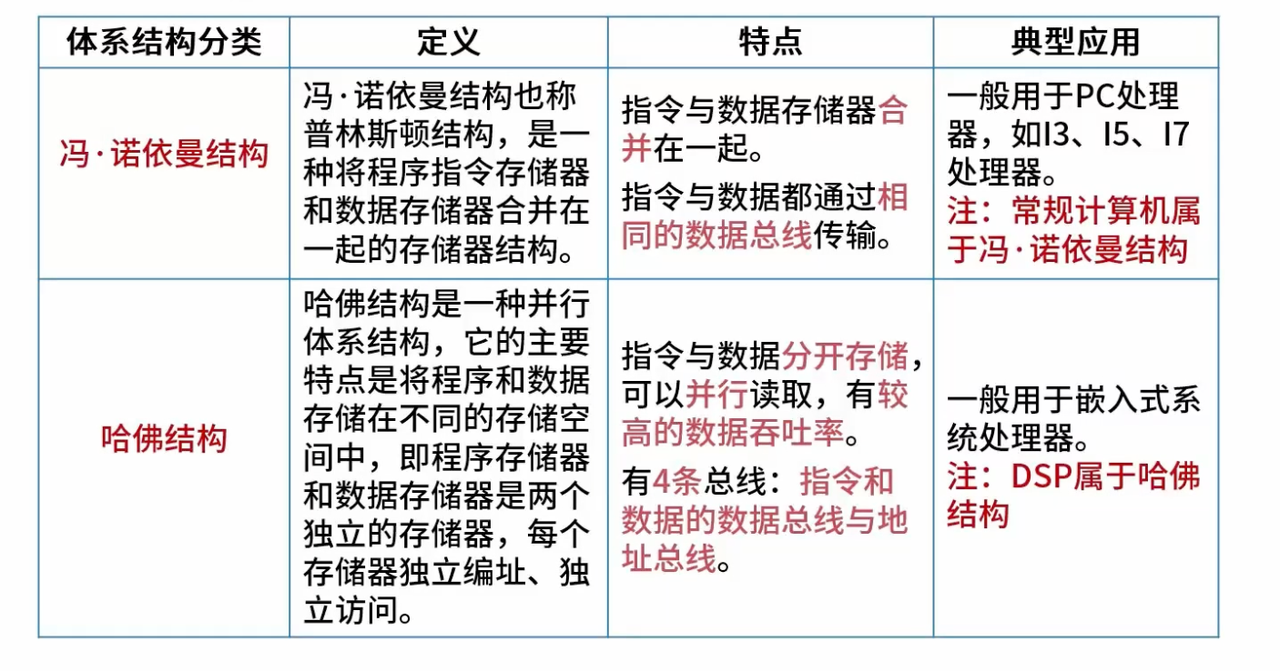

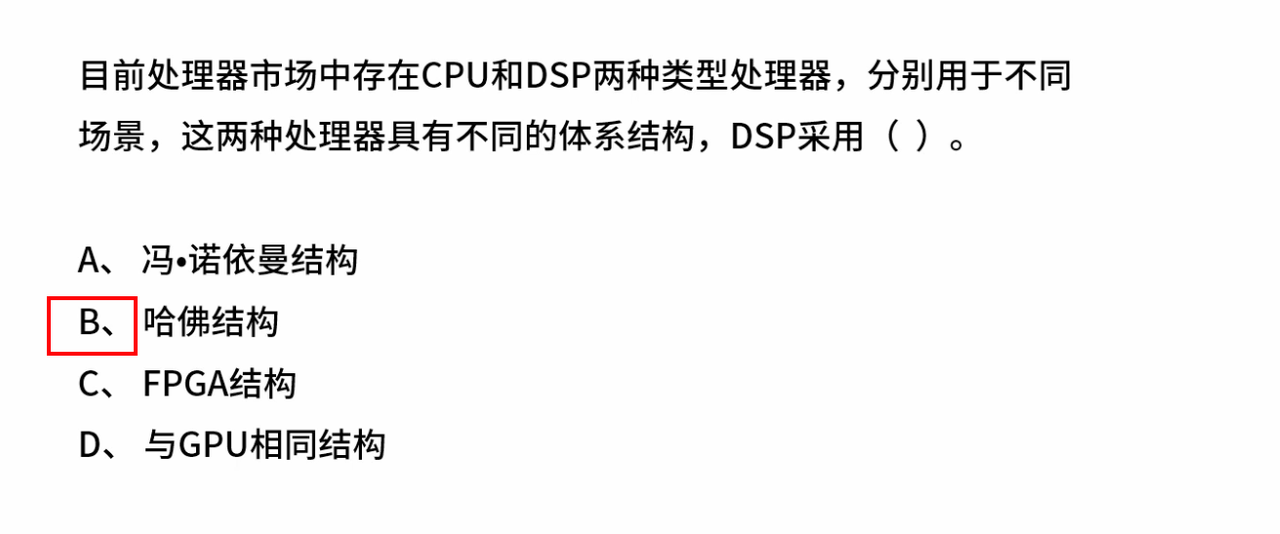

| 处理器架构 | CISC vs RISC、冯·诺依曼 vs 哈佛结构 | 理解不同架构的适用场景 |

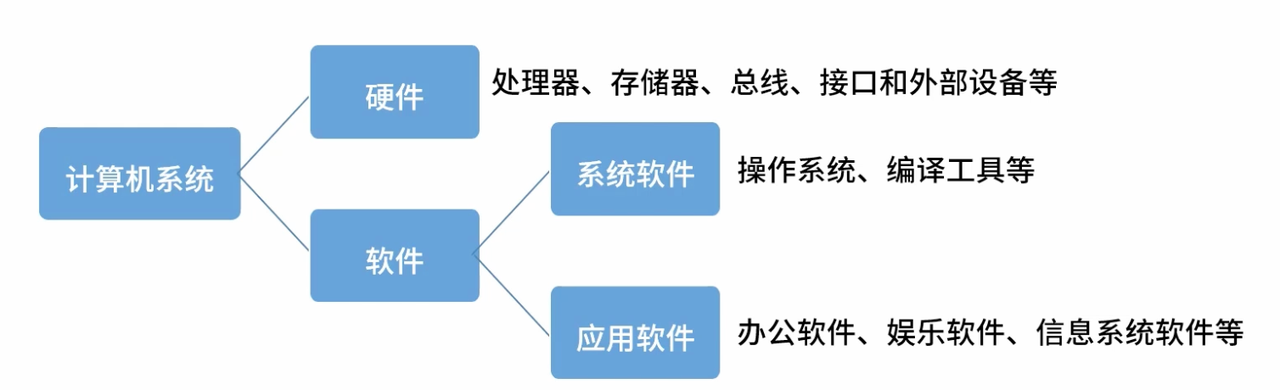

二、计算机系统基础组成

本章节将详细介绍计算机系统的硬件和软件组成,帮助读者建立完整的系统认知。

1、硬件系统组成

处理器(CPU):作为计算机的运算和控制核心,负责执行指令、处理数据。

| 特征 | 说明 | 实际产品 | 应用价值 |

|---|---|---|---|

| 运算能力 | 决定计算机运行速度和多任务处理能力 | Intel酷睿i7-12700K、AMD锐龙7 5800X | 影响程序执行效率,决定系统整体性能 |

| 核心数量 | 多核处理器可并行处理多个任务 | 8核16线程的Intel i7处理器 | 提升多任务处理能力,适合服务器应用 |

| 缓存大小 | 内置高速缓存减少内存访问延迟 | L3缓存32MB的处理器 | 提高数据访问速度,优化程序性能 |

存储器系统:用于存储程序、数据和中间结果的设备,分为主存储器和辅助存储器。

| 类型 | 特点 | 容量范围 | 应用场景 |

|---|---|---|---|

| RAM(随机存取存储器) | 速度快,断电数据丢失 | 8GB-128GB | 存储正在运行的程序和数据 |

| ROM(只读存储器) | 永久存储,不可修改 | 几MB | 存储BIOS等系统固件 |

| 硬盘(HDD/SSD) | 容量大,永久存储 | 500GB-10TB | 存储操作系统、应用程序、用户数据 |

| 固态硬盘(SSD) | 速度快,无机械部件 | 256GB-4TB | 提升系统启动和程序加载速度 |

实际应用对比:

// 传统机械硬盘 vs 固态硬盘性能对比

机械硬盘:读取速度 100-150 MB/s,寻道时间 8-12ms

固态硬盘:读取速度 500-3500 MB/s,寻道时间 0.1ms

// 实际影响:系统启动时间

机械硬盘:Windows启动需要 30-60秒

固态硬盘:Windows启动仅需 10-20秒

总线系统:连接计算机各功能部件的公共通信干线,负责传输数据、地址和控制信号。

| 总线类型 | 功能 | 实际应用 | 性能影响 |

|---|---|---|---|

| 数据总线 | 传输数据信息 | PCIe 4.0 x16显卡接口 | 影响数据传输带宽 |

| 地址总线 | 传输内存地址 | 64位地址总线支持4GB以上内存 | 决定可寻址内存空间 |

| 控制总线 | 传输控制信号 | USB控制信号管理设备连接 | 协调各部件工作时序 |

2、软件系统组成

系统软件:管理计算机硬件资源,为应用软件提供运行环境的软件。

| 软件类型 | 主要功能 | 典型产品 | 实际作用 |

|---|---|---|---|

| 操作系统 | 资源管理、任务调度、设备管理 | Windows 11、Ubuntu 22.04、macOS Monterey | 提供用户界面,管理硬件资源 |

| 编译工具 | 将高级语言转换为机器语言 | GCC、Visual Studio、Clang | 将源代码编译为可执行程序 |

| 设备驱动 | 控制硬件设备工作 | 显卡驱动、网卡驱动 | 让操作系统识别和控制硬件 |

实际应用示例:

// 操作系统资源管理示例

Windows任务管理器显示:

- CPU使用率:25%(4核处理器中1核满负荷)

- 内存使用:8GB/16GB(50%使用率)

- 磁盘使用:500GB/1TB(50%使用率)

// 编译工具使用示例

gcc -o hello hello.c // 将C语言源文件编译为可执行文件

./hello // 运行编译后的程序

应用软件:面向特定应用需求开发的软件,直接为用户提供服务。

| 软件分类 | 典型产品 | 主要功能 | 使用场景 |

|---|---|---|---|

| 办公软件 | Microsoft Office、WPS Office | 文档处理、表格计算、演示制作 | 日常办公、商务应用 |

| 开发工具 | Visual Studio Code、IntelliJ IDEA | 代码编写、调试、版本管理 | 软件开发、系统维护 |

| 数据库软件 | MySQL、PostgreSQL、Oracle | 数据存储、查询、管理 | 企业信息系统、Web应用 |

| 娱乐软件 | 腾讯视频、Steam游戏平台 | 视频播放、游戏娱乐 | 个人娱乐、休闲活动 |

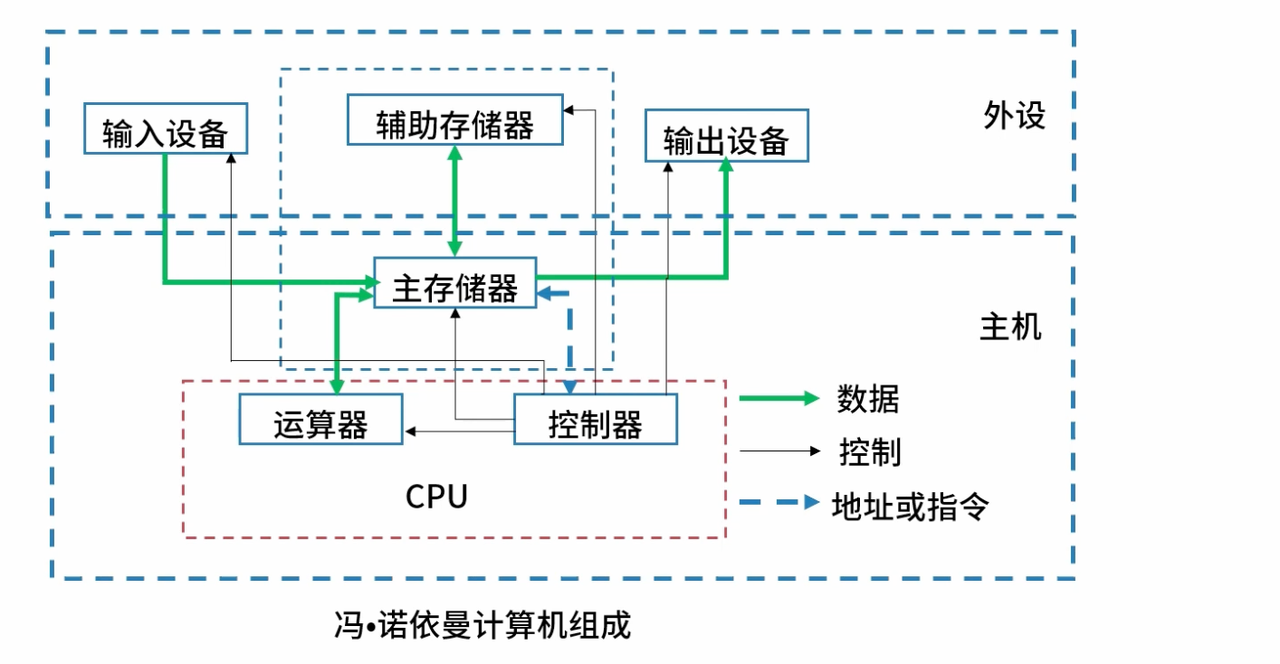

三、冯·诺依曼体系结构

本章节将深入解析冯·诺依曼计算机的五大组成部分及其工作原理。

1、五大核心组件

- 运算器:负责进行算术运算(如加、减、乘、除 )和逻辑运算(如与、或、非 )。它从主存储器获取数据,按照指令进行运算操作,再将运算结果返回主存储器 。比如在计算1 + 2时,运算器从主存读取1和2,执行加法运算后,把结果3存回主存。

- 控制器:计算机的指挥中心,从主存储器中逐条读取指令,对指令进行译码分析,然后向计算机各部件发出控制信号,协调各部件有序执行指令规定的操作。例如,当要执行一个文件打开指令时,控制器会指挥相关部件完成从存储设备读取文件等操作 。

- 主存储器:用于临时存储计算机正在运行的程序和数据,可被CPU直接访问。它就像一个临时的数据仓库,存储着当前需要处理的数据和程序指令,方便CPU快速读取和写入。

- 辅助存储器:即外部存储设备,如硬盘、U盘等,用于长期存储大量数据和程序。当需要使用这些数据或程序时,先从辅助存储器调入主存储器,再由CPU处理。

- 输入设备:向计算机输入数据和指令的设备,常见的有键盘、鼠标、扫描仪等。用户通过输入设备将信息传递给计算机,比如在键盘上输入文字,这些文字信息就会进入计算机系统。

- 输出设备:将计算机处理的结果以人们能够识别的形式输出,如显示器、打印机、音箱等。例如,计算机处理完文档编辑后,通过显示器将编辑后的文档内容显示出来。

2、数据流向与控制机制

- 数据流向(绿色箭头):从输入设备获取数据,存入主存储器,运算器从主存读取数据进行运算,运算结果再存回主存,最后可从主存输出到输出设备;辅助存储器也可与主存进行数据交换,存储或读取数据 。

- 控制流向(黑色箭头):控制器发出控制信号,指挥运算器、主存储器、输入输出设备等部件按指令要求工作 。

- 地址或指令流向(蓝色虚线箭头):控制器从主存储器读取指令,解析指令中的地址信息,指挥各部件按地址访问数据或执行操作 。

四、计算机系统组成

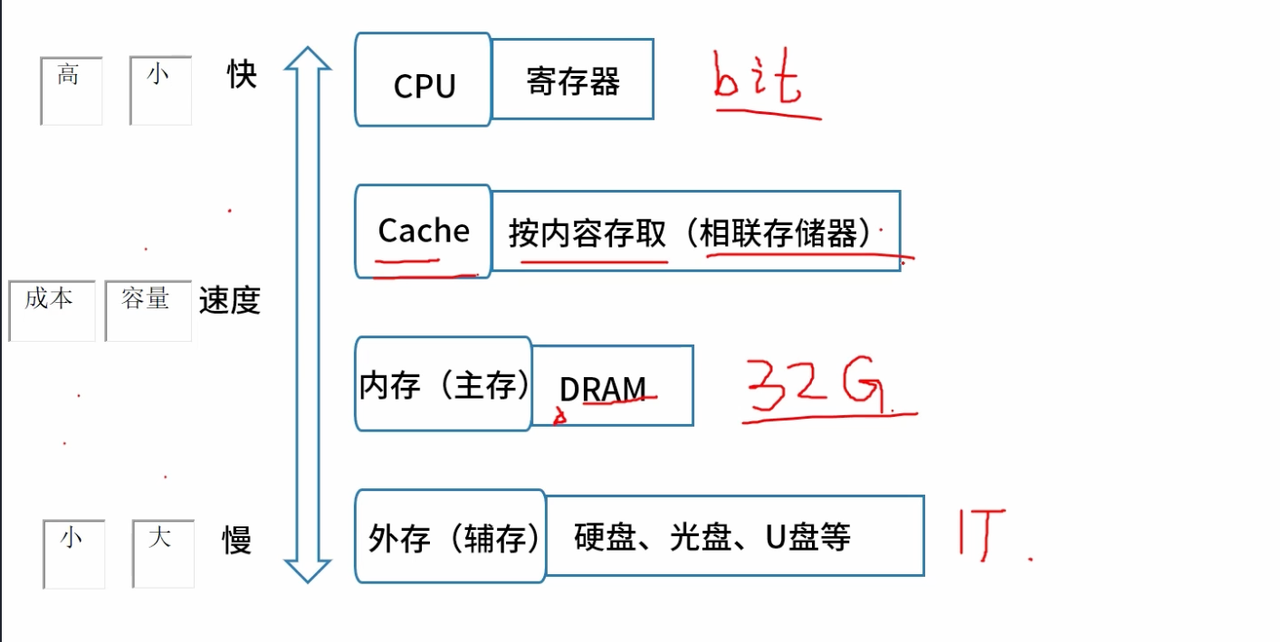

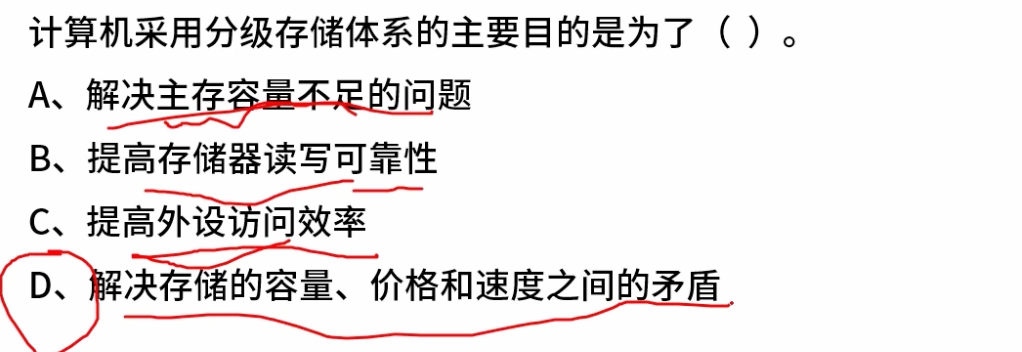

1、存储层次结构

上图展示了计算机的层次化存储结构,从高到低介绍如下:

| 存储层级 | 核心位置与特性 | 核心作用 |

|---|---|---|

| CPU寄存器 | 存储体系顶层,与CPU紧密相连;速度极快(纳秒级)、成本极高、容量极小(KB级),以“bit”为单位 | 实时存储CPU正在/即将处理的核心数据和指令,实现CPU零等待访问,直接决定单次运算效率 |

| Cache(高速缓存) | 寄存器之下,多集成于CPU内;采用相联存储器技术,速度较快(近寄存器)、成本较高、容量(MB级)大于寄存器但远小于内存 | 缓存CPU近期高频访问的数据/指令,CPU优先查找,命中则快速获取,大幅减少内存访问次数 |

| 内存(主存) | Cache之下,多为DRAM技术;速度适中(几十至几百纳秒)、成本适中、容量大(常见8-32GB),断电数据丢失 | 存储操作系统、运行中程序及待处理数据,供CPU直接读写,是程序运行的核心临时存储区 |

| 外存(辅存) | 存储体系底层,含硬盘/U盘/光盘等;速度最慢(毫秒级)、成本最低、容量极大(TB级),断电数据不丢失 | 长期存储海量数据/程序,需先调入内存,才能被CPU读取和处理 |

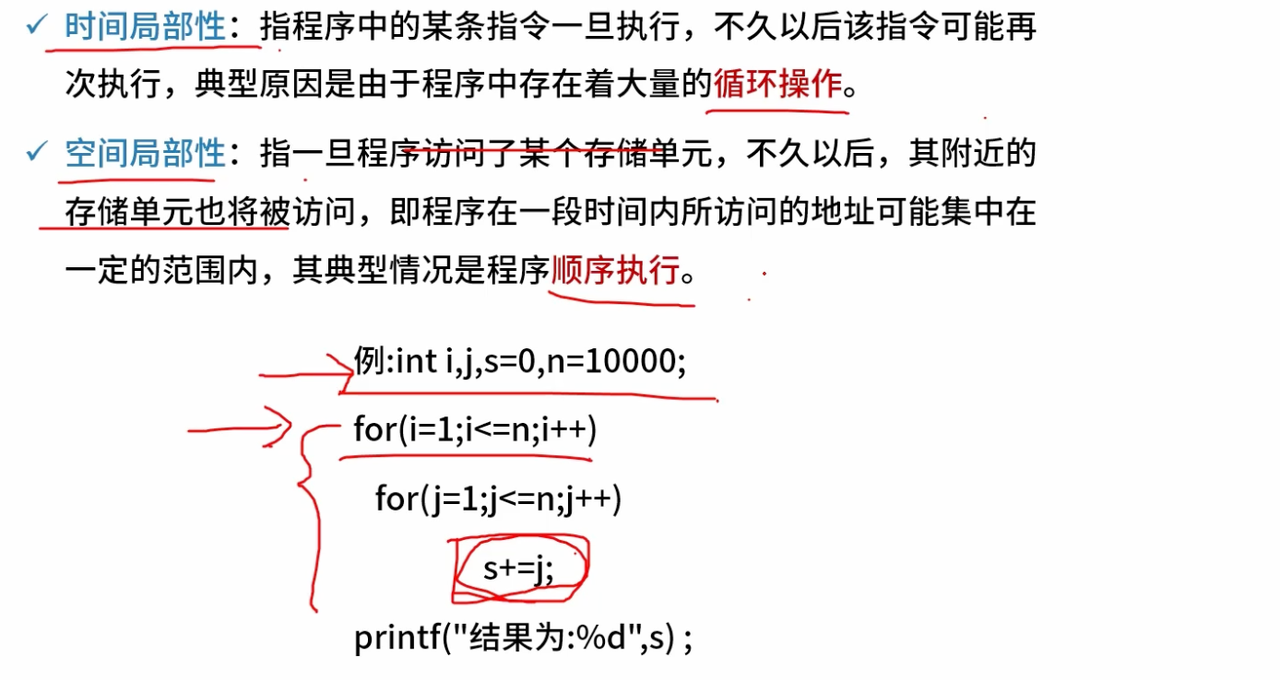

2、局部性原理

时间局部性

- 概念:程序中的某条指令一旦执行,不久后该指令可能再次执行 ,主要源于程序中大量的循环操作。比如在一段循环代码中,循环体内的指令会反复执行,每次执行到相同指令时,若之前执行过,就体现了时间局部性。

- 示例分析:图中代码里,s += j; 语句在两层嵌套 for 循环中,会被反复执行很多次,这很好地体现了时间局部性,因为这条指令在短时间内会多次被执行。

空间局部性

- 概念:程序访问了某个存储单元后,不久其附近的存储单元也会被访问,典型情况是程序顺序执行。计算机内存按地址连续存储数据,当程序顺序读取数据时,会访问相邻地址的存储单元。

- 示例分析:在图中代码的执行过程中,若数据在内存中连续存储,例如数组元素的存储 ,在循环遍历数组进行计算(类似 s += j; 这种涉及数据操作)时,会顺序访问相邻的数组元素所在存储单元,这就体现了空间局部性。

五、总线系统

本章节将全面解析计算机总线系统的分类、特点和工作机制。

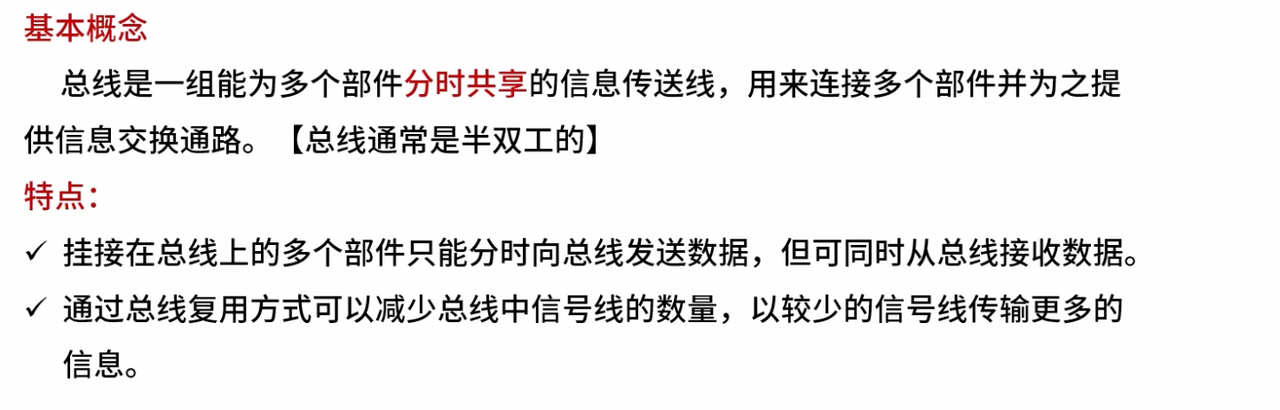

1、总线基本概念

总线是连接计算机各功能部件的公共通信干线,实现分时共享的信息传输。

| 特性 | 技术原理 | 实际应用 | 性能影响 |

|---|---|---|---|

| 分时共享 | 多个部件按时间顺序使用总线 | 多个设备不能同时发送数据 | 避免信号冲突,确保数据传输正确 |

| 半双工 | 同一时刻只能单向传输 | 发送和接收不能同时进行 | 简化总线设计,降低硬件成本 |

| 总线复用 | 一条信号线传输多种信息 | 地址和数据复用同一组信号线 | 减少信号线数量,降低布线复杂度 |

实际工作示例:

// 总线分时共享的实际表现

时间片1:CPU向内存发送读取请求

时间片2:内存向CPU返回数据

时间片3:显卡向内存请求纹理数据

时间片4:网卡向内存写入接收到的数据

// 总线复用技术

传统方式:需要64条数据线 + 32条地址线 = 96条信号线

复用方式:32条信号线在不同时间传输地址和数据

硬件节省:减少67%的信号线,降低PCB设计复杂度

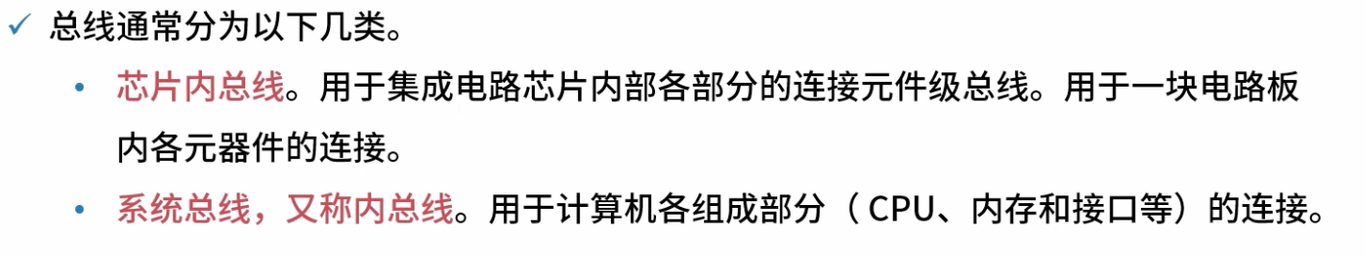

2、总线分类体系

按功能分类

概念定义:根据总线传输的信息类型进行分类。

| 总线类型 | 传输内容 | 实际应用 | 性能特点 |

|---|---|---|---|

| 数据总线 | 实际数据信息 | CPU与内存间的数据传输 | 宽度决定每次传输的数据量 |

| 地址总线 | 内存或I/O设备地址 | CPU访问特定内存单元 | 宽度决定可寻址空间大小 |

| 控制总线 | 控制信号和时序信号 | 协调各部件工作 | 确保数据传输的正确性和时序 |

实际性能对比:

// 不同数据总线宽度的性能差异

32位数据总线:每次传输4字节数据

64位数据总线:每次传输8字节数据

128位数据总线:每次传输16字节数据

// 实际应用影响

32位系统:最大支持4GB内存(2^32字节)

64位系统:最大支持16EB内存(2^64字节)

实际限制:受操作系统和硬件设计限制,通常支持128GB-2TB内存

按传输方式分类

概念定义:根据数据传输的并行性进行分类。

| 传输方式 | 技术原理 | 典型应用 | 优缺点对比 |

|---|---|---|---|

| 并行总线 | 多条数据线同时传输 | PCI、AGP显卡接口 | 速度快,但成本高,距离受限 |

| 串行总线 | 数据逐位依次传输 | USB、SATA、PCIe | 成本低,距离远,但速度相对较慢 |

实际应用对比:

// 并行总线 vs 串行总线性能对比

并行总线(PCI):

- 32位并行传输

- 理论带宽:133MB/s

- 实际应用:老式显卡、网卡接口

- 缺点:信号干扰严重,传输距离短

串行总线(PCIe):

- 串行传输,但使用多条通道

- PCIe 3.0 x16:16GB/s带宽

- 实际应用:现代显卡、SSD接口

- 优点:抗干扰能力强,传输距离远

// 现代发展趋势

并行总线:逐渐被淘汰,仅用于特殊应用

串行总线:成为主流,通过多通道实现高带宽

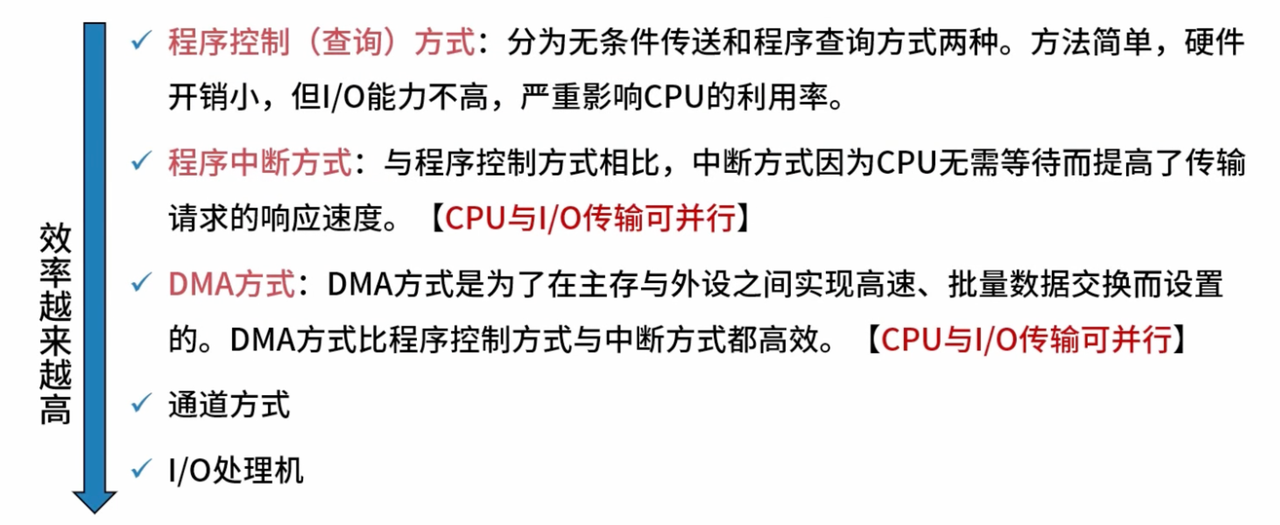

3、数据传输控制方式

程序控制方式

概念定义:CPU通过程序主动查询和控制数据传输的方式。

| 控制类型 | 工作原理 | 实际应用 | 性能特点 |

|---|---|---|---|

| 无条件传送 | CPU按固定时序传输数据 | 简单设备控制 | 实现简单,但效率低 |

| 程序查询 | CPU循环查询设备状态 | 低速设备控制 | 硬件成本低,但CPU利用率低 |

实际应用示例:

// 程序查询方式的实际代码

while (true) {

if (设备状态寄存器.数据就绪 == 1) {

数据 = 从设备读取数据();

处理数据(数据);

break;

}

// CPU在这里空转等待,浪费计算资源

}

// 性能问题分析

CPU利用率:在等待设备准备期间,CPU无法执行其他任务

实际效率:CPU利用率可能只有10-30%

适用场景:仅适用于对实时性要求不高的简单应用

程序中断方式

概念定义:设备准备好数据后主动向CPU发送中断请求,CPU响应中断处理数据传输。

| 中断类型 | 触发条件 | 处理方式 | 性能优势 |

|---|---|---|---|

| 硬件中断 | 设备状态改变 | CPU暂停当前任务处理中断 | 提高CPU利用率 |

| 软件中断 | 程序主动触发 | 系统调用、异常处理 | 实现系统服务调用 |

实际工作流程:

// 中断处理的实际流程

1. 设备准备数据完成

2. 设备向CPU发送中断请求信号

3. CPU保存当前程序状态(寄存器、程序计数器等)

4. CPU跳转到中断服务程序

5. 执行数据传输操作

6. CPU恢复之前保存的程序状态

7. 继续执行被中断的程序

// 性能提升效果

CPU利用率:从10-30%提升到70-90%

响应时间:中断响应时间通常在微秒级别

并发处理:CPU可以在等待I/O期间处理其他任务

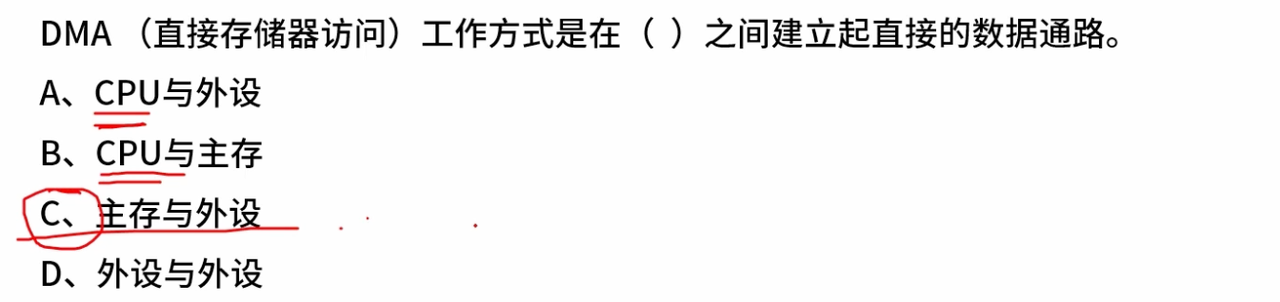

DMA方式

概念定义:直接内存访问,通过专门的DMA控制器在主存和外设间直接传输数据。

| DMA特性 | 技术优势 | 实际应用 | 性能提升 |

|---|---|---|---|

| 直接传输 | 绕过CPU,直接访问内存 | 硬盘读写、网络数据传输 | 减少CPU负担,提高传输效率 |

| 批量传输 | 一次传输大量数据 | 文件复制、视频播放 | 提高数据传输吞吐量 |

| 并行处理 | CPU和DMA同时工作 | 多任务处理 | 实现真正的并行处理 |

实际应用示例:

// DMA在文件复制中的应用

传统方式:

1. CPU从源文件读取数据到CPU寄存器

2. CPU将数据从寄存器写入目标文件

3. 重复上述步骤直到文件复制完成

问题:CPU全程参与,无法处理其他任务

DMA方式:

1. CPU设置DMA控制器参数(源地址、目标地址、传输大小)

2. CPU启动DMA传输

3. DMA控制器直接在主存和硬盘间传输数据

4. CPU可以同时处理其他任务

5. DMA传输完成后向CPU发送中断

// 性能对比

传统方式:CPU利用率100%,文件复制期间系统响应缓慢

DMA方式:CPU利用率5-10%,文件复制期间系统响应正常

传输速度:DMA方式通常比传统方式快2-5倍

六、处理器体系结构

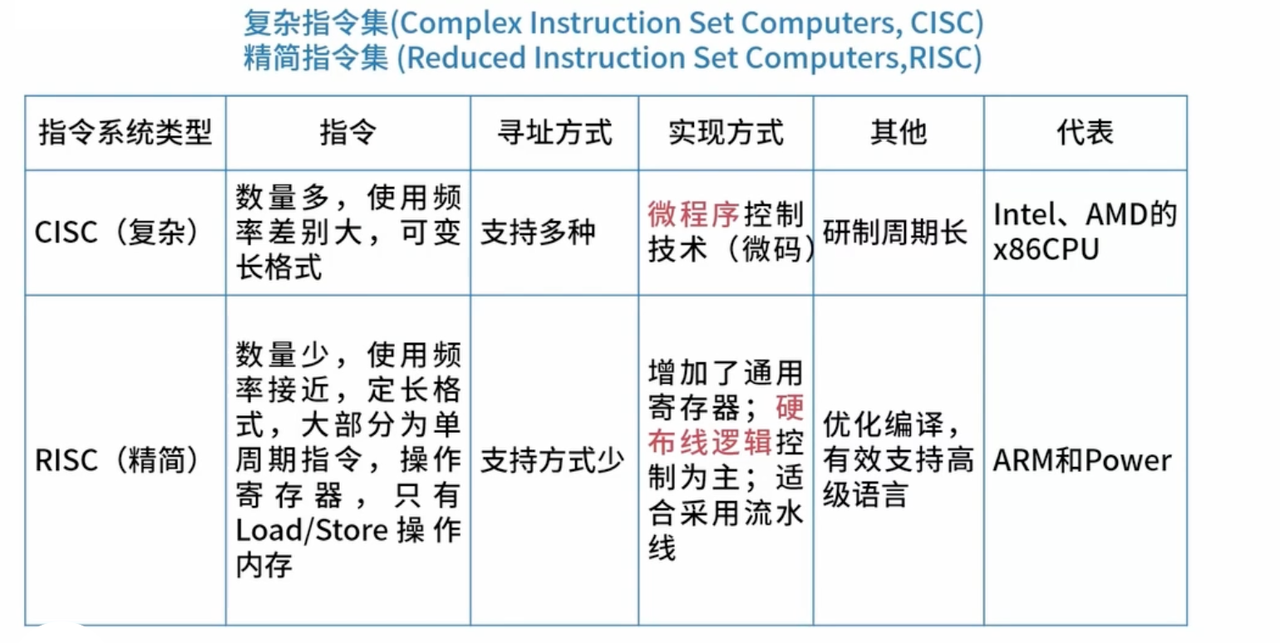

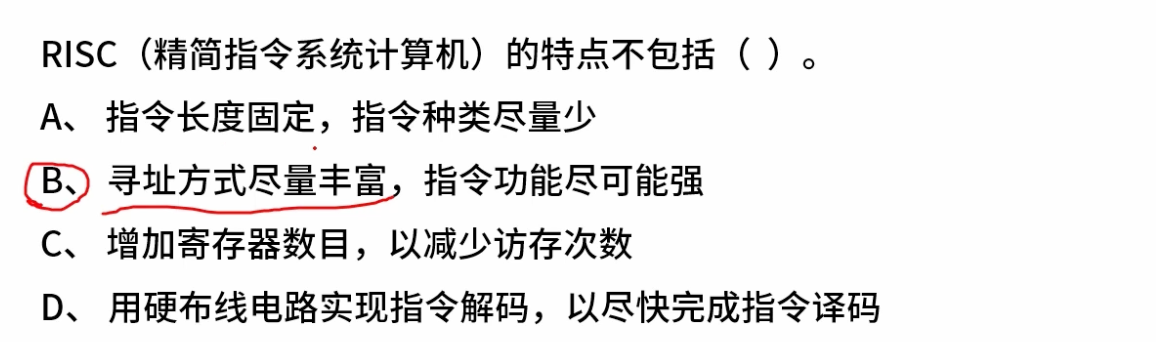

1、CISC vs RISC架构

2、现代处理器发展趋势

多核处理器

概念定义:在单个芯片上集成多个处理核心的处理器架构。

| 核心配置 | 技术特点 | 实际产品 | 性能提升 |

|---|---|---|---|

| 双核 | 2个处理核心 | Intel Core 2 Duo | 多任务处理能力提升 |

| 四核 | 4个处理核心 | Intel i5、AMD Ryzen 5 | 并行计算能力增强 |

| 八核 | 8个处理核心 | Intel i7、AMD Ryzen 7 | 高性能计算应用 |

实际应用示例:

// 多核处理器的任务分配

单核处理器:

任务1 → 任务2 → 任务3 → 任务4

(串行执行,总时间 = 各任务时间之和)

四核处理器:

核心1:任务1

核心2:任务2

核心3:任务3

核心4:任务4

(并行执行,总时间 = 最长任务时间)

// 实际性能提升

视频编码:4核比单核快3-4倍

游戏运行:4核支持更复杂的游戏场景

多任务处理:同时运行多个应用程序不卡顿

超线程技术

概念定义:通过硬件技术让单个物理核心模拟多个逻辑核心的技术。

| 技术原理 | 实现方式 | 性能提升 | 应用场景 |

|---|---|---|---|

| 逻辑核心 | 1个物理核心模拟2个逻辑核心 | 提升20-30%性能 | 多线程应用 |

| 资源复用 | 共享执行单元和缓存 | 提高资源利用率 | 服务器应用 |

| 并行处理 | 同时处理多个线程 | 减少线程切换开销 | 数据库系统 |

实际工作示例:

// 超线程技术的工作原理

物理核心1:

- 逻辑核心1:执行线程A

- 逻辑核心2:执行线程B

当线程A等待内存数据时:

- 逻辑核心1:暂停线程A

- 逻辑核心2:继续执行线程B

- 充分利用CPU资源

// 性能对比

无超线程:CPU利用率60-70%

有超线程:CPU利用率80-90%

实际效果:多线程应用性能提升20-30%