一、SDRAM介绍

SDRAM(Synchronous Dynamic Random Access Memory),同步动态随机存储器。同步、动态、随机是其性能特点的外在说明:

同步(Synchronous )是指内存工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准

动态(Dynamic )是指存储阵列 需要不断的刷新来保证数据不丢失

随机(Random )是指数据不是线性依次存储,而是自由指定地址进行 数据读写

SDRAM具有空间存储量大、读写速度快、价格相对便宜等优点。然而由于SDRAM内部利用电容来存储数据,为保证数据不丢失,需要持续对各存储电容进行刷新操作;同时在读写过程中 需要考虑行列管理、各种操作延时等,由此导致了其控制逻辑复杂的特点。

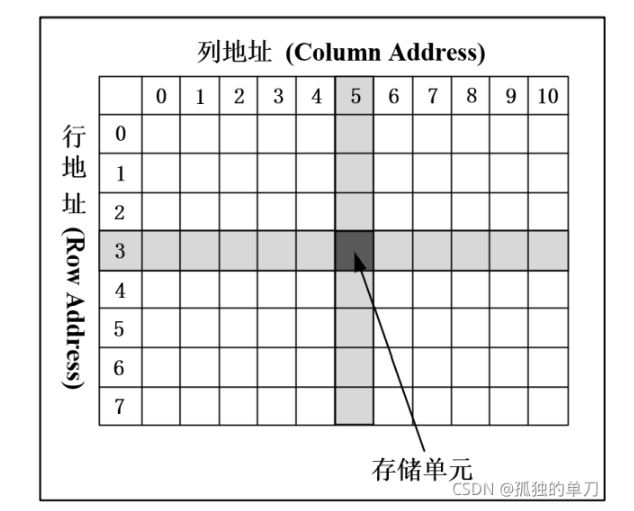

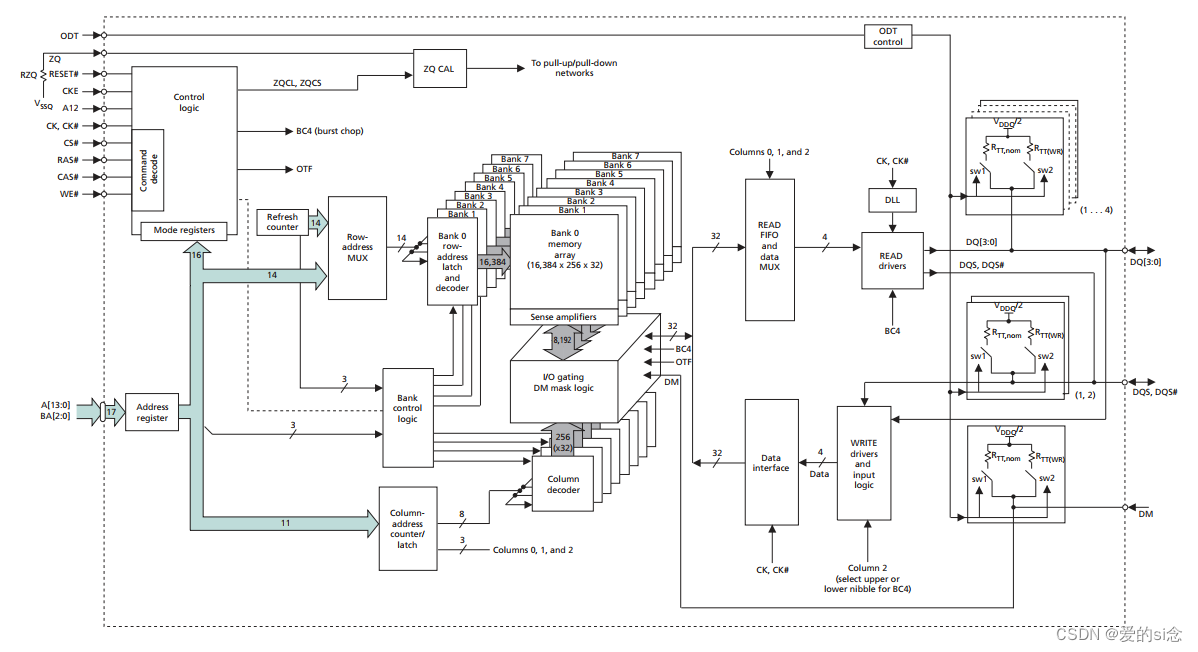

SDRAM 内部可以理解为一个存储阵列,表格中的每一个单元格可以类比为存储阵列的单个存储单元。若想要实现存储阵列中的某一存储单元的数据读写操作,我们要通过行地址(Row Address)和列地址 (Column Address)(先行后列)精确定位到这一存储单元,进而进行数据的读写操作,这就是所谓的随机地址存取.

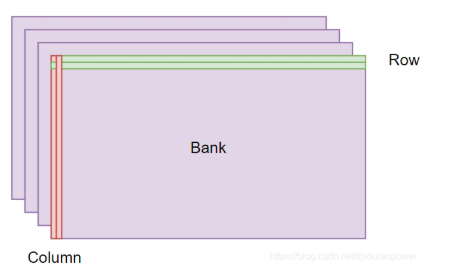

由于行列地址引脚数量有限,导致寻址空间有限,为了扩大sdram的容量,每个sdram都有几块bank,每个bank都是一个单独的存储逻辑块,共用行列引脚,同时再用几个引脚来选择不同的bank。 Row、Column、Bank 就是sdram基本的组成部分,一个sdram的容量就是row*column*bits*bank,bits为每个存储单元的位数,16位的sdram每个存储单元有16bit,32位的sdram每个单元有32bit。

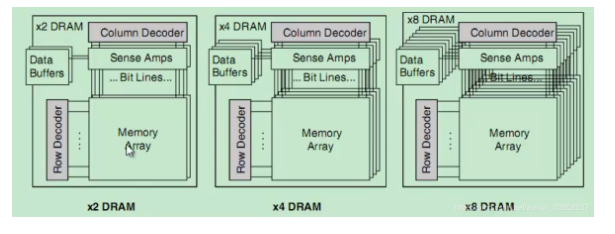

由于行、列的这种寻址操作一次只能定位1bit数据,对于4bit、8bit、16bit、64bit的sdram每个bank中都有4个、8个、16个、64个Memory Array,这些Memory Array是并联的共用行列地址线。比如4bit的sdram,一个bank中有4个Memory Array,一次就能取出4bit数据。

二、LPDDR4概述

LPDDR4是新一代面向移动设备的低功耗内存,它属于SDRAM家族的存储器产品。2014年JEDEC固态技术协会正式发布LPDDR4标准。JEDEC发布的LPDDR4规范编号是“JESD209-4”,文档链接为:JEDEC JESD209-4-2014 Low Power Double Data Rate 4 (Lpddr4) - 道客巴巴 。JEDEC规定了LPDDR4的主要内部结构、引脚功能、命令真值表、读写时序、寄存器等,每个厂家生产的LPDDR都会依照这个规范来做。

相关名词解释:

Die:芯片晶元单元。芯片行业中wafer,die,cell的概念

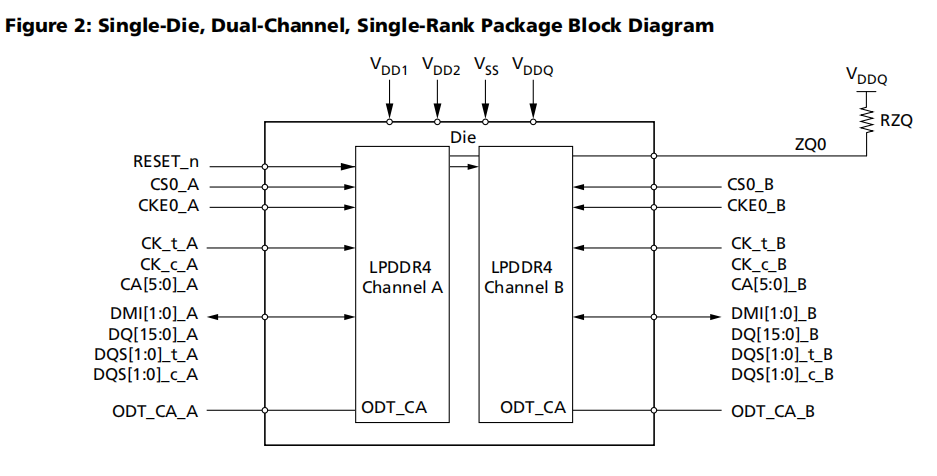

Channel:通道,每个die中有一个或两个通道

Bank:存逻辑块

Rank:rank是为了凑cpu的位数。例如cpu是64bit的,但是sdram一般是4bit或者8bit,所以要凑8个,也就是数据位扩展,这8个就叫一个rank。

bank<rank<die<channel

下面以美光的MT53B256M32型号的LPDDR4芯片为例做介绍。MT53B256M32数据手册下载地址:https://media-www.micron.com/-/media/client/global/documents/products/data-sheet/dram/mobile-dram/low-power-dram/lpddr4/200b_z91m_sdp_ddp_auto_lpddr4.pdf?rev=b2562b5ff0a0479baacd533a55f21ce9

2.1 LPDDR4基本结构

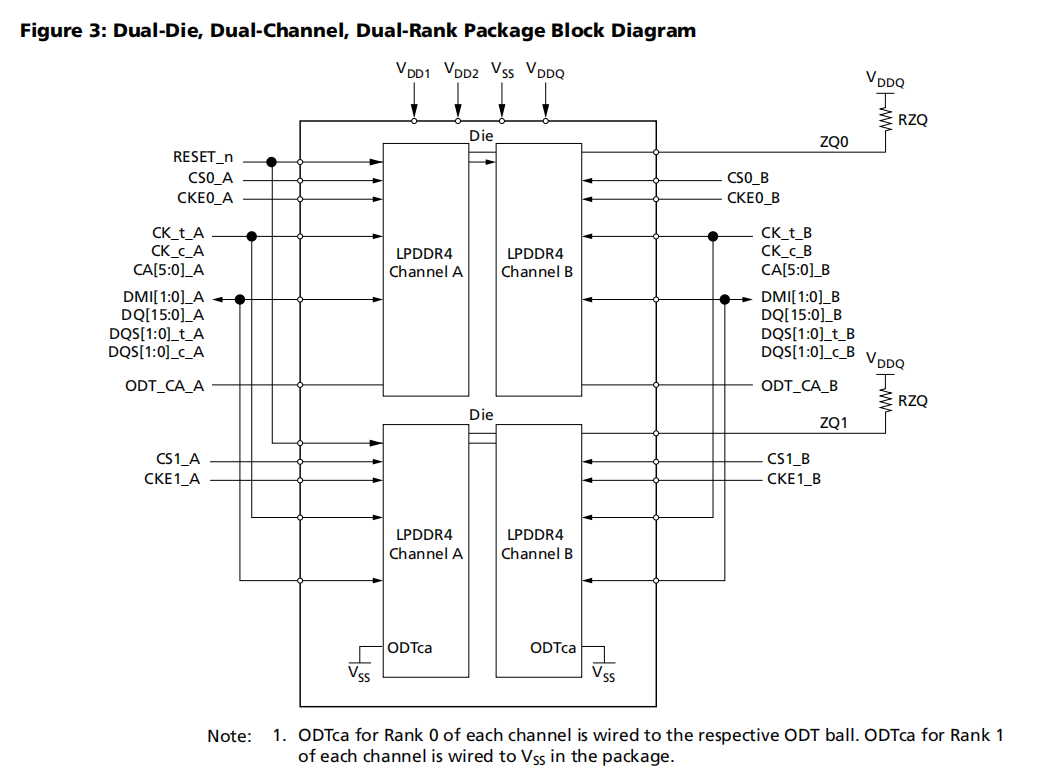

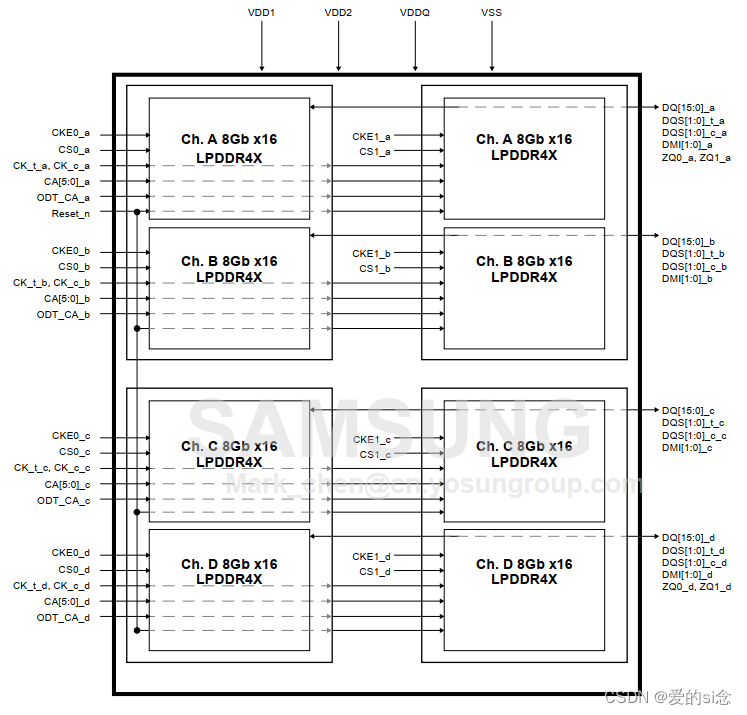

64bit Single-Rank

64bit Dual-Rank

内部结构

2.2 引脚描述

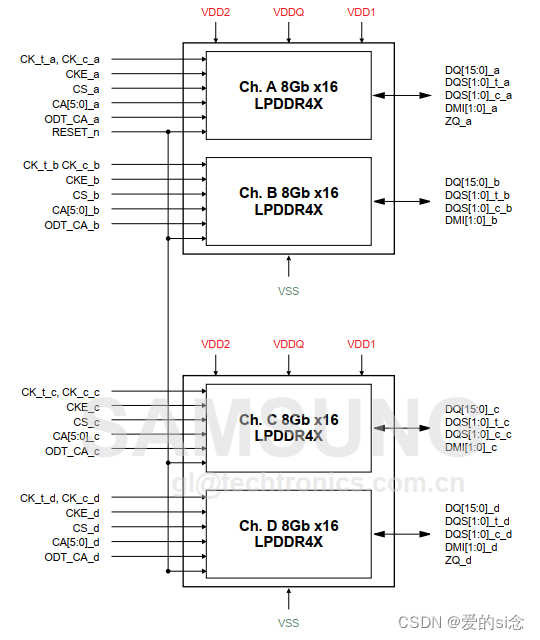

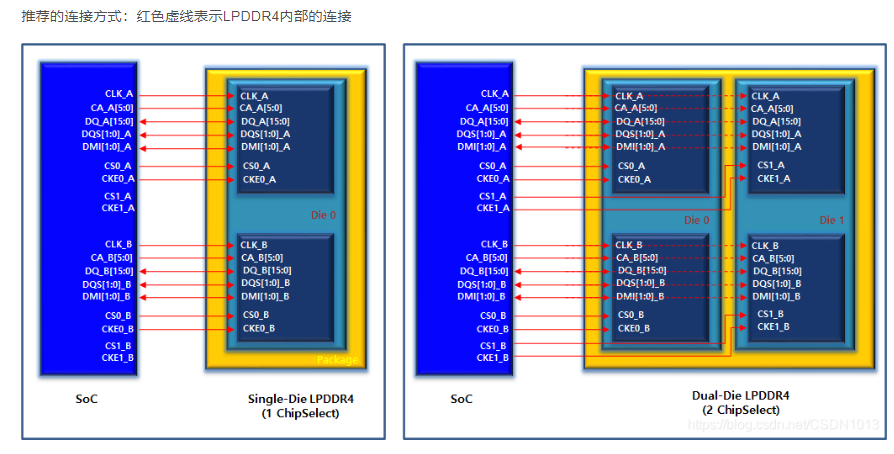

2.3 LPDDR4与soc的连接方式

LPDDR4与soc的连接方式如下所示:

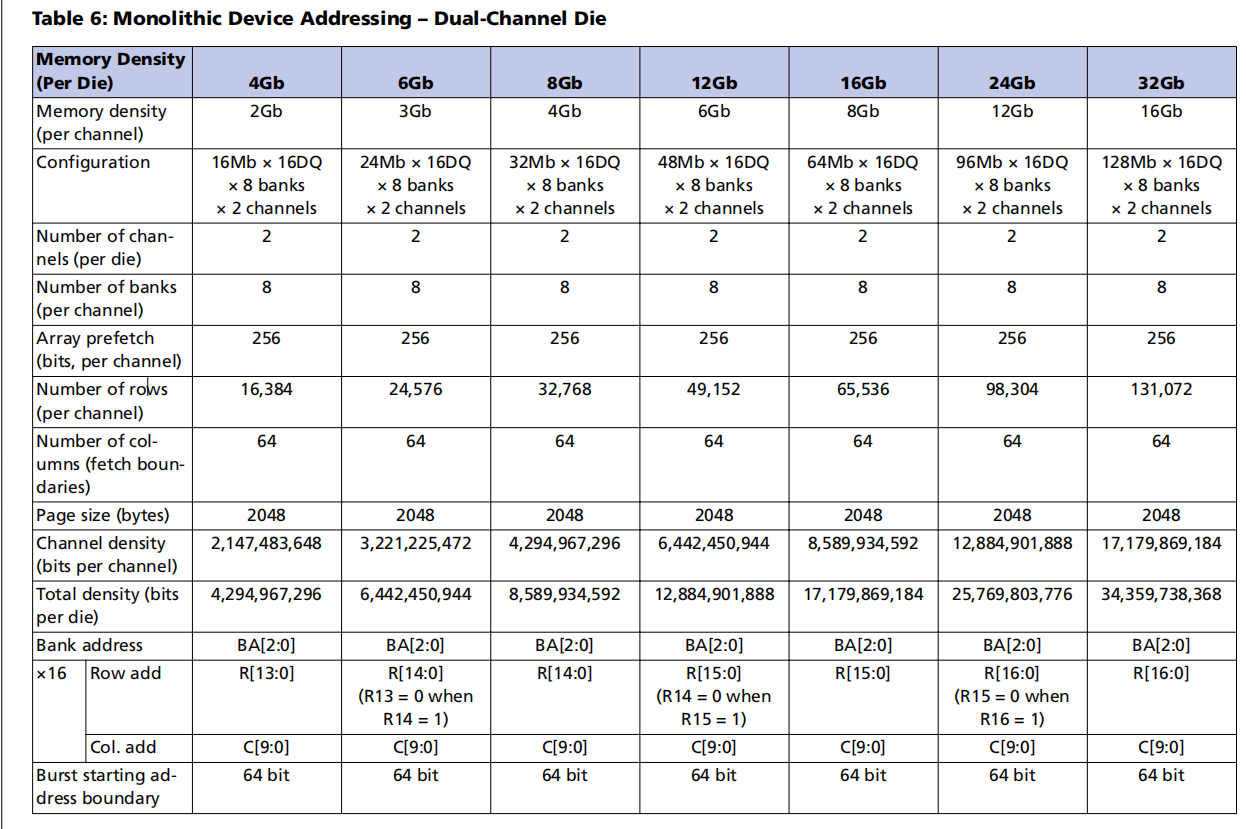

2.4 LPDDR4寻址表

LPDDR4寻址表遵循JEDEC制定的规范

下面以寻址表中第二列4Gb为例做解释:

Memory Density(Per Die) 4Gb:每个die容量为4Gb

Memory density(per channel) 2Gb:每个通道大小为2Gb,一个die有两个通道

Configuration 16Mb × 16DQ× 8 banks× 2 channels :16Mb的寻址空间*16位*每个channels8个bank*每个die两channels。16Mb为R[13:0] 和C[9:0]组成的寻址空间。 214 × 210 ÷ 102 ÷ 1024 = 16Mb。

Channel density(bits per channel) 2,147,483,648 :每个通道的粒度,即每个通道可以存储多少位的数据,214 × 210 × 16 × 8 = 2,147,483,648(行寻址空间*列寻址空间*16位*每个channel有8bank)

Total density (bitsper die) 4,294,967,296:每个die的粒度,每个die有两个channel,这个值为Channel density的两倍

Bank address BA[2:0]:bank选择通道

Row add R[13:0] :行选信号

Col. add C[9:0]:列选信号

注:bank选择信号、行选信号、列选信号并不对应lpddr4实际的控制引脚,lpddr可以理解为sdram外面封装了一个ddr控制器,lpddr4的命令、地址信号是CA[5:0]_A, CA[5:0]_B,ddr控制器会将这两个引脚信号转化为内部控制sdram的行、列和bank信号。

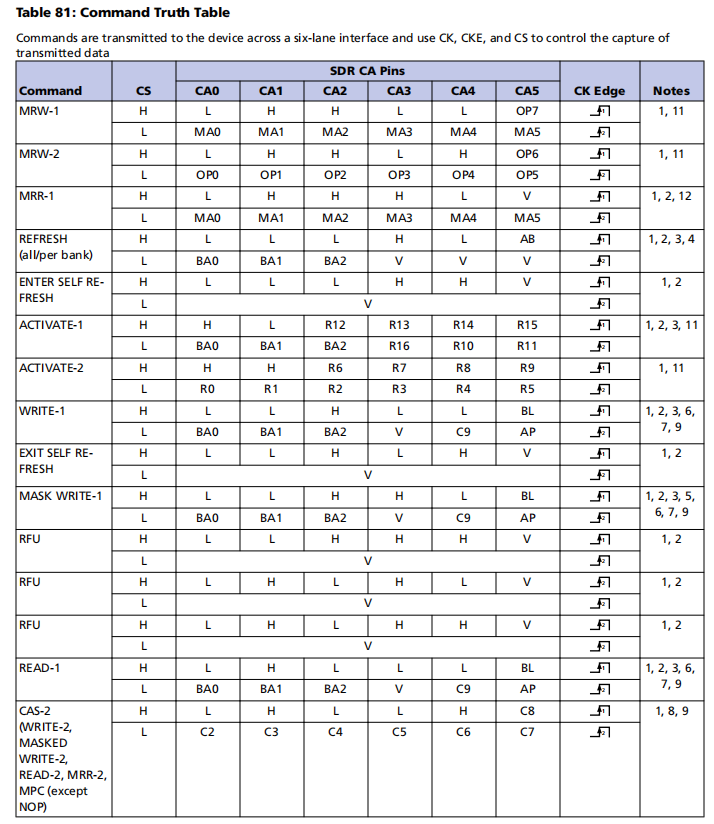

三、命令和读写时序

LPDDR4有专用的DQ[15:0]数据引脚来传输数据,为了减少引脚数量,节省空间,LPDDR4用CA[5:0]命令/地址复用引脚来复用bank选择信号、行选择信号、列选择信号。通过编辑命令的形式将这三种地址型号编辑成不同的命令。LPDDR4每个命令都需要连续的两个时钟上升沿来锁存。LPDDR4命令真值表如下所示:

注:LPDDR4的命令真值表和读写时序都遵循JEDEC制定的标准。

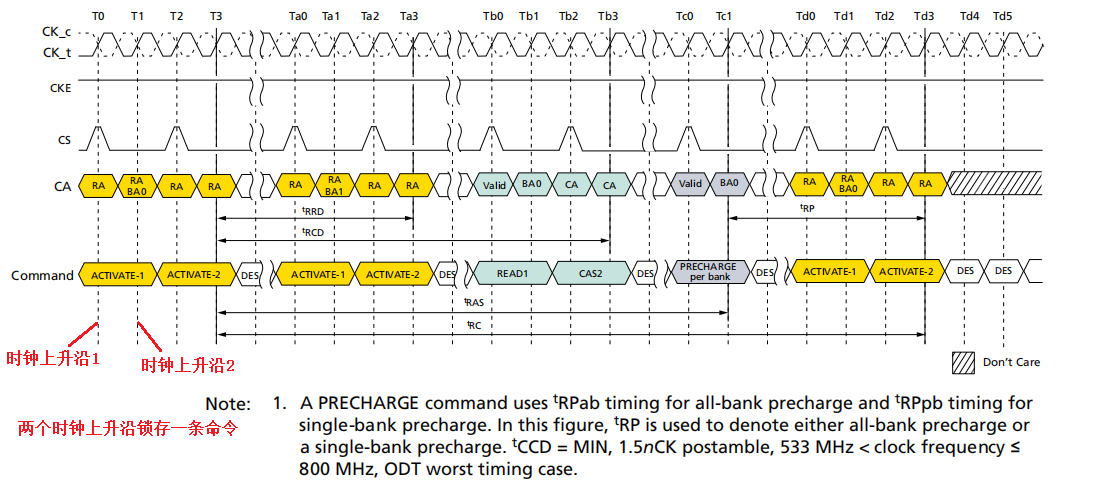

3.1 ACTIVATE命令

在读写命令之前,必须要发送ACTIVATE命令,ACTIVATE命令由ACTIVATE-1和ACTIVATE-2组成,ACTIVATE命令中包含了BA[2:0]的bank选择信号和R[15:0]的行选择信号。ACTIVATE命令时序如下所示;

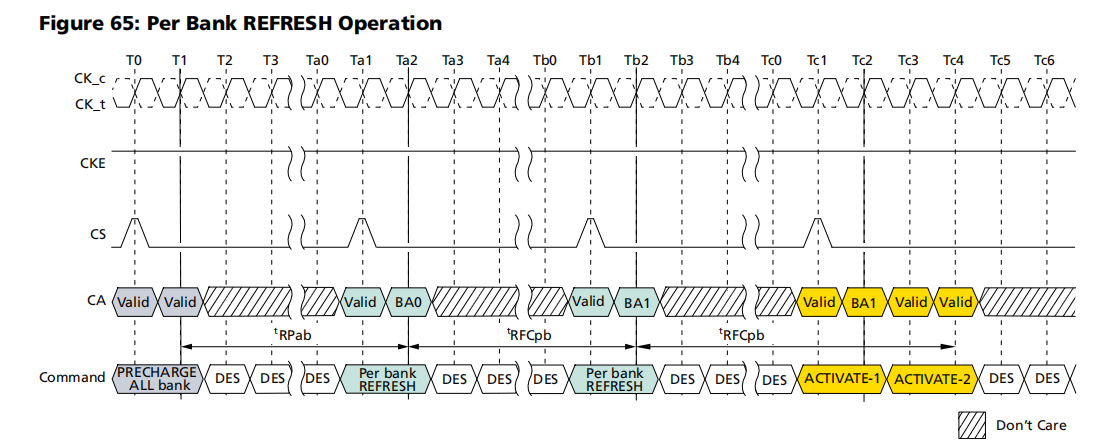

3.2 REFRESH 命令

REFRESH 命令就是刷新lpddr命令,lpddr需要不断的刷新来保证数据不会丢失。可以选择一次刷新所有8个bank或每次刷新一个bank。一次刷新所有bank和一次刷新一个bank的命令如下所示:

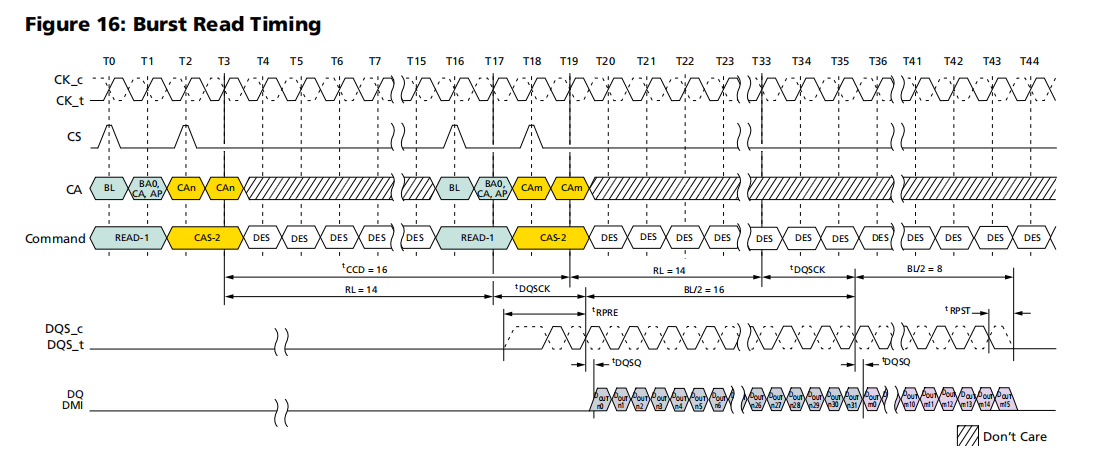

3.3 读时序

在ACTIVATE命令后,就可以发送读命令,读命令包含列地址信号,突发读命令如下所示:

这里只举例一种读时序,更多的读方式请芯片参考数据手册或“JESD209-4”规范

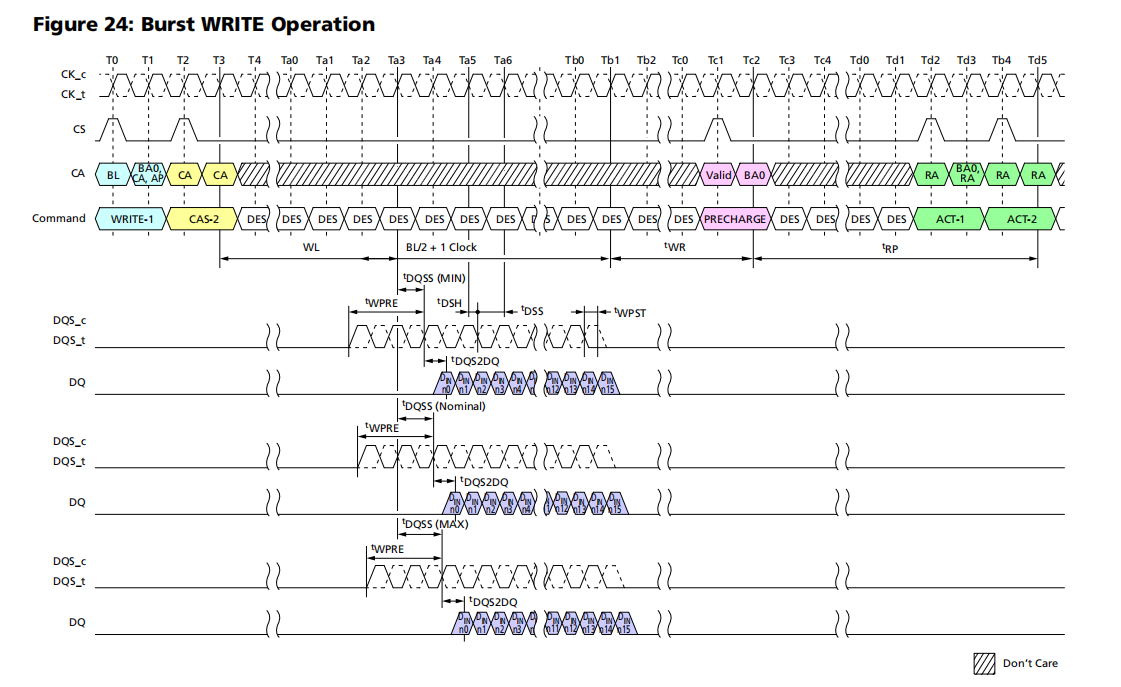

3.4 写时序

在ACTIVATE命令后,就可以发送写命令,写命令包含列地址信号,突发写时序如下所示:

这里只举例一种写时序,更多的写方式请芯片参考数据手册或“JESD209-4”规范