Ø CCOpt 概念

Ø 传统 CTS 介绍

Ø CCOpt 技术介绍

Ø CCOpt 优化流程

Ø Worst Chain Analysis

概念介绍

传统 CTS 介绍

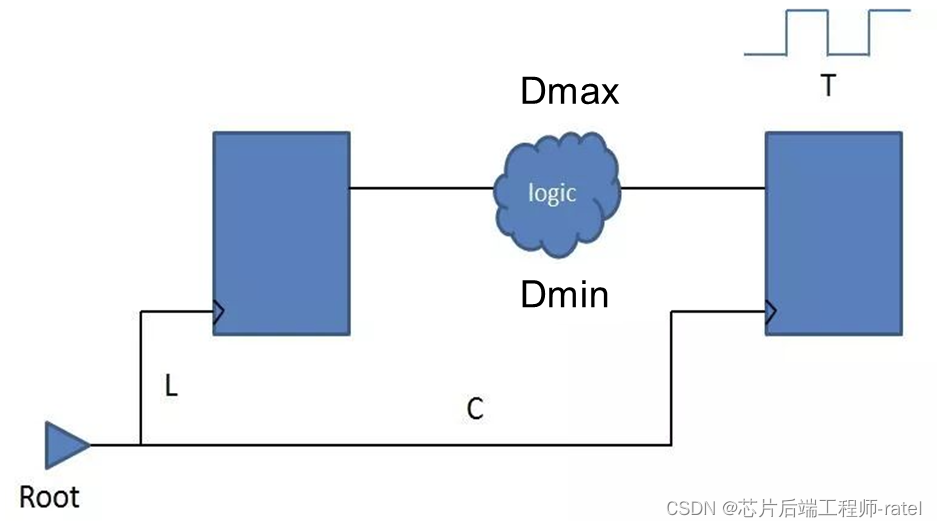

对传统的flop to flop之间的电路,setup和hold time需要满足以下两个条件,如图所示:

Propagated clock:

setup: L+ Dmax < T + C

hold: L+ Dmin > C

Ideal clock:

setup: Dmax < T

hold: Dmin > 0

Dmin > 0 是一个永远成立的条件,在这个model下面,我们只需要保证logic path上的最大delay,也就是critical path上的delay比时钟周期快就行。

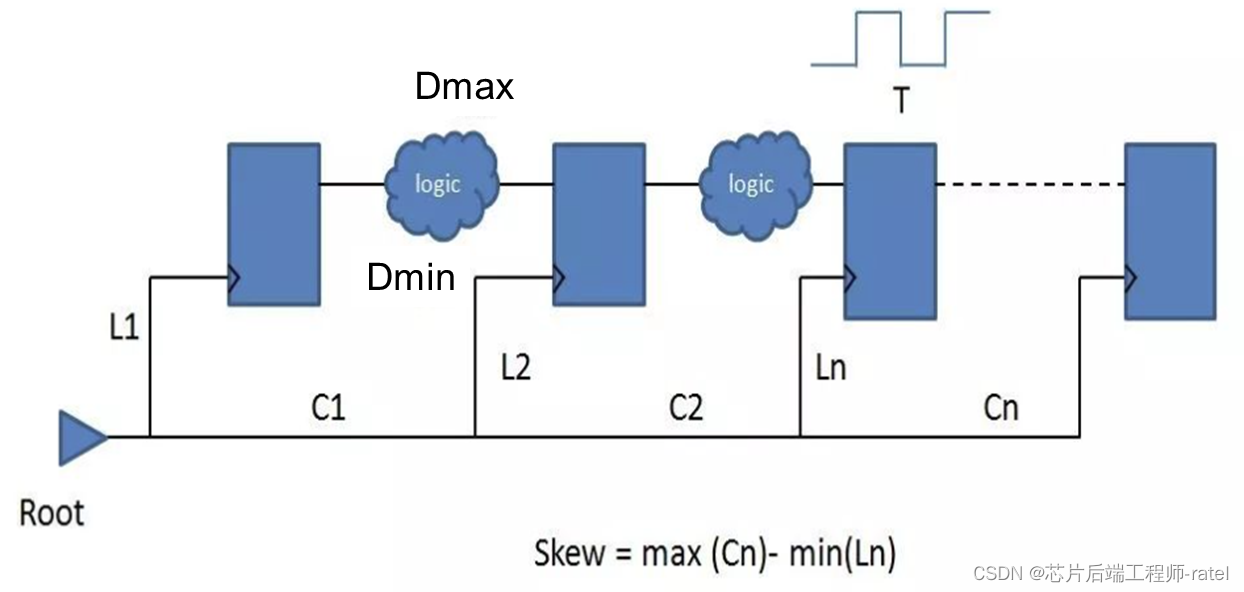

当一个时钟树有N个sink以后,这里就有了global skew概念,完全balance的时钟树就很难做,clock skew变成各个flop之间的Launch和capture clock path的最大差值。

Propagated clock:

setup: Dmax < T - (L-C)

hold: Dmin > C – L

Ideal clock:

setup: Dmax< T + skew

hold: Dmin > skew

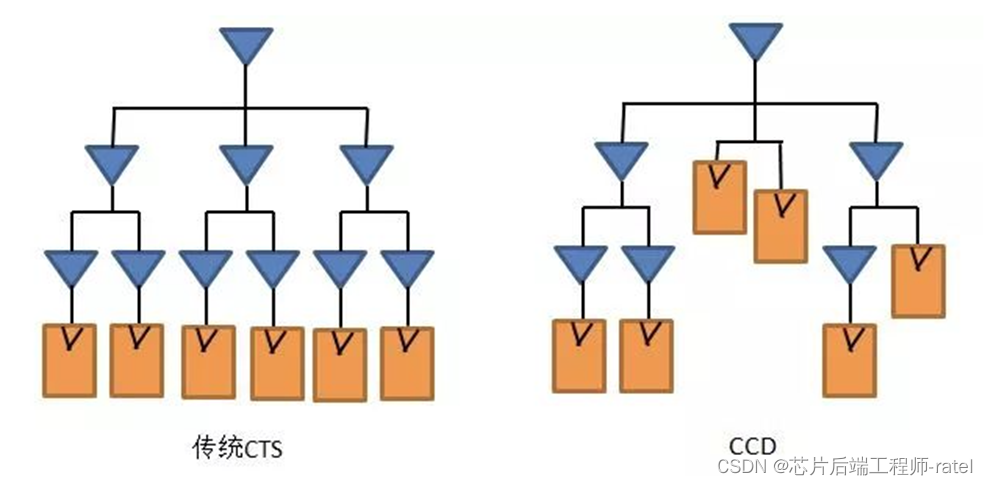

CCOpt 技术介绍

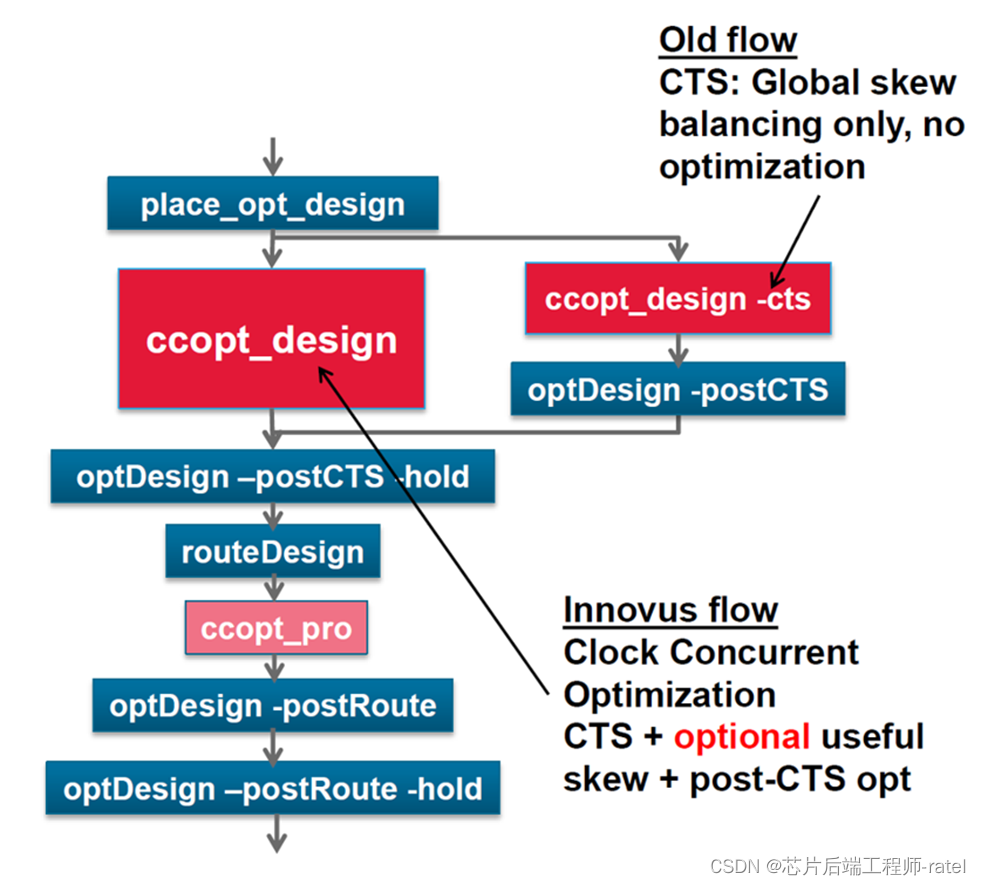

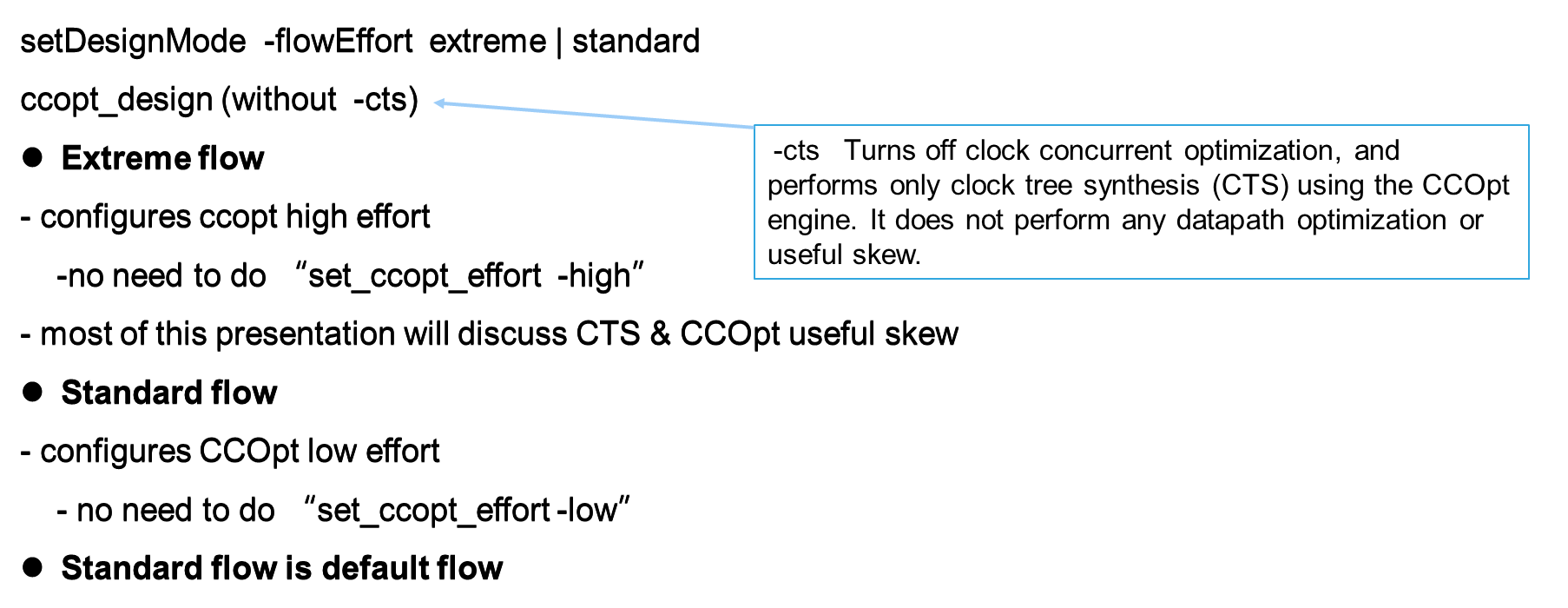

CCOpt 优化流程

CCOpt 技术介绍

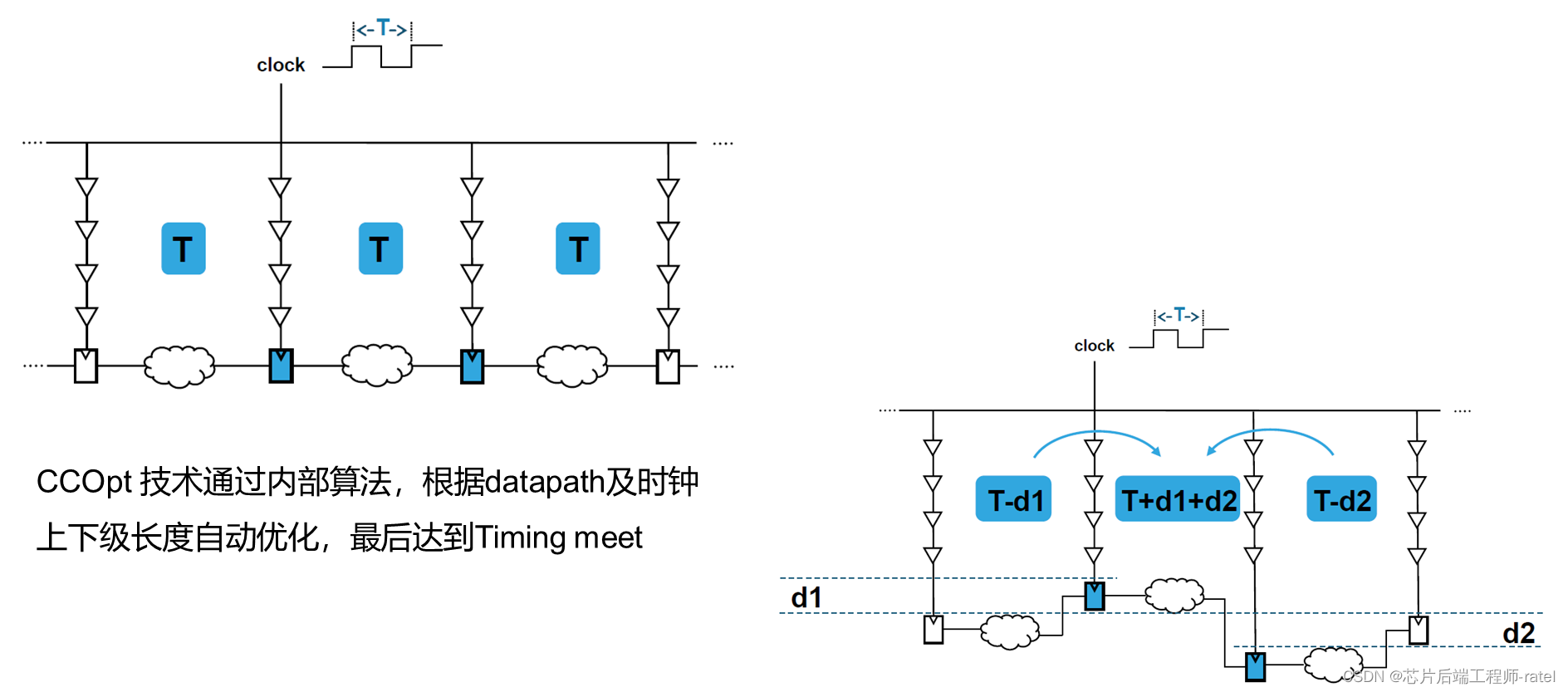

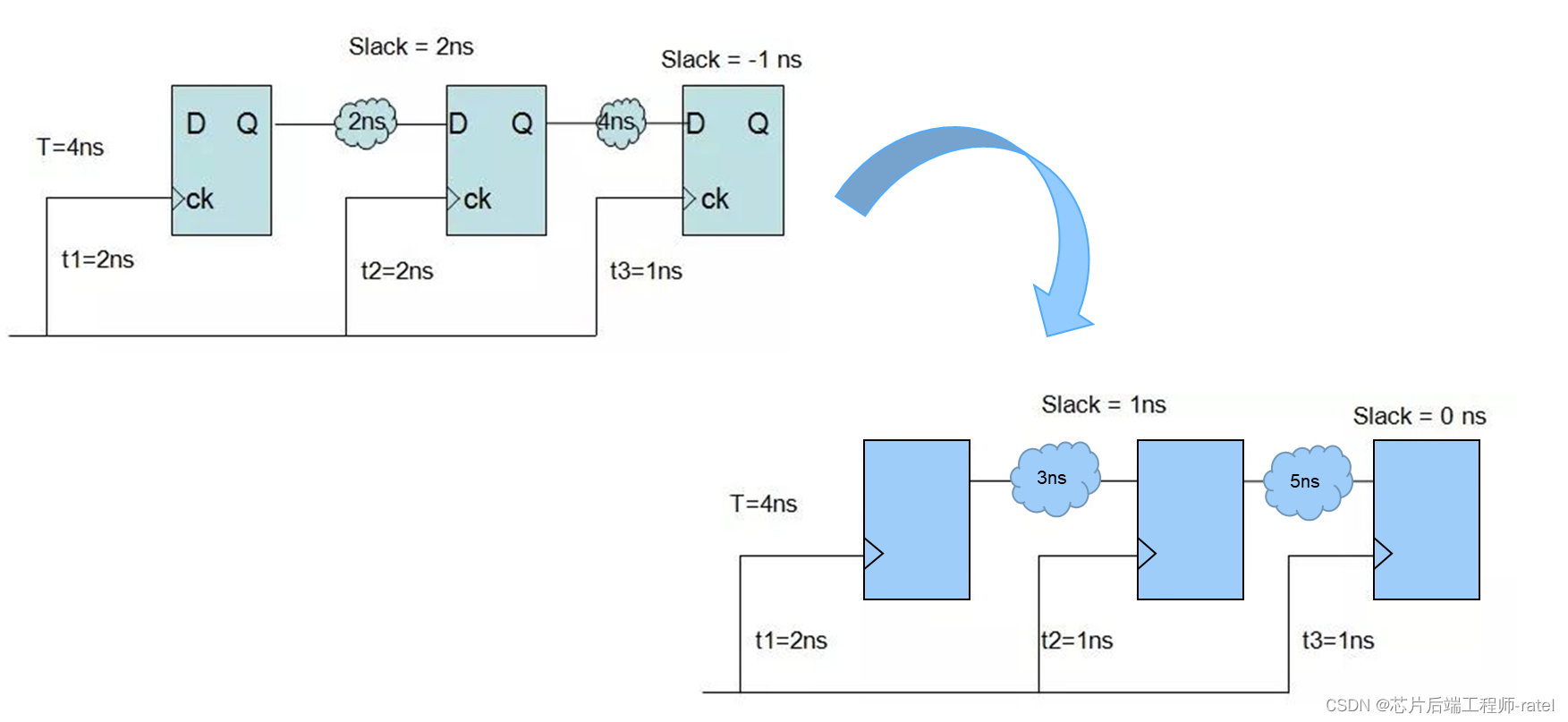

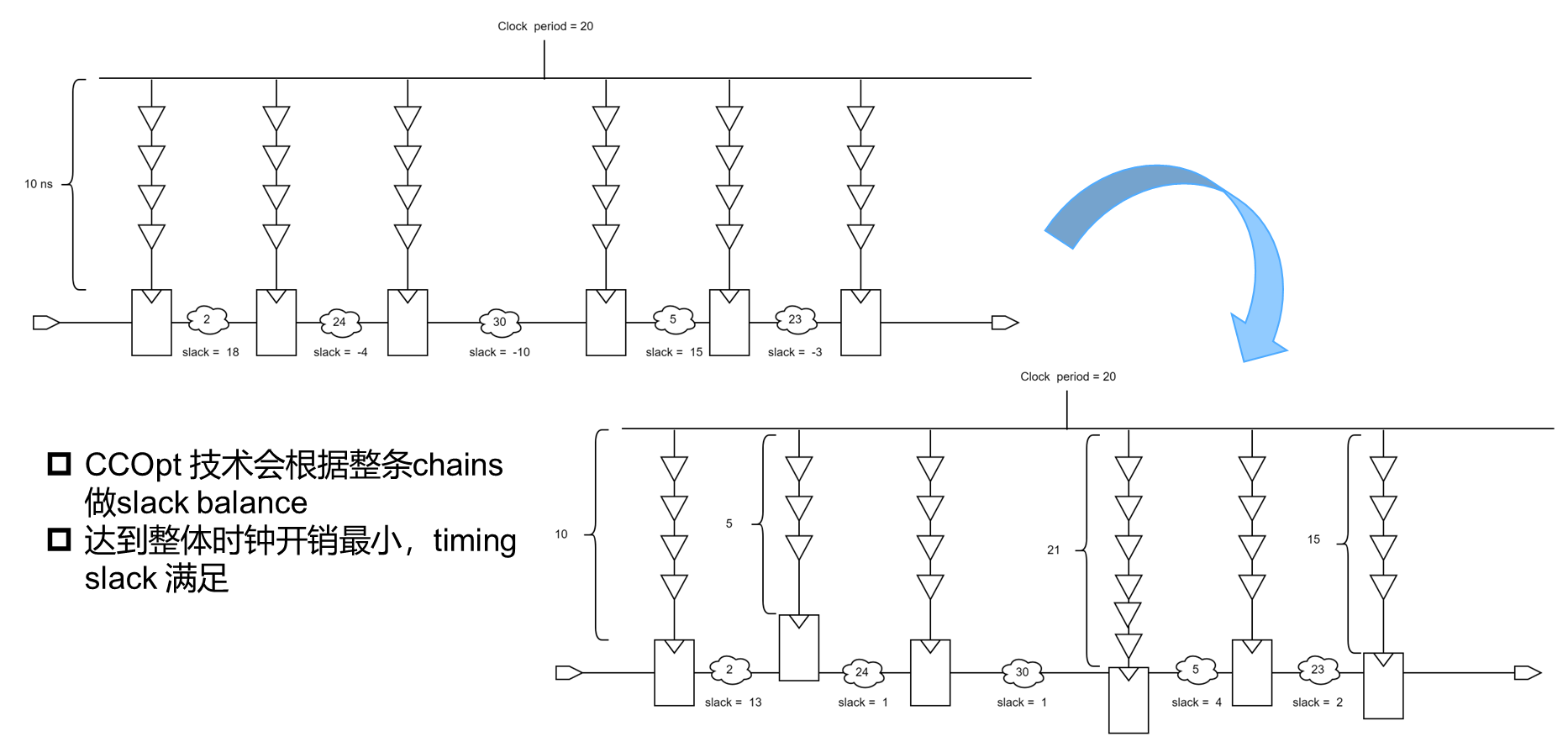

如下图可以看到,ccopt技术通过做短T2达到整体timing meet的要求。

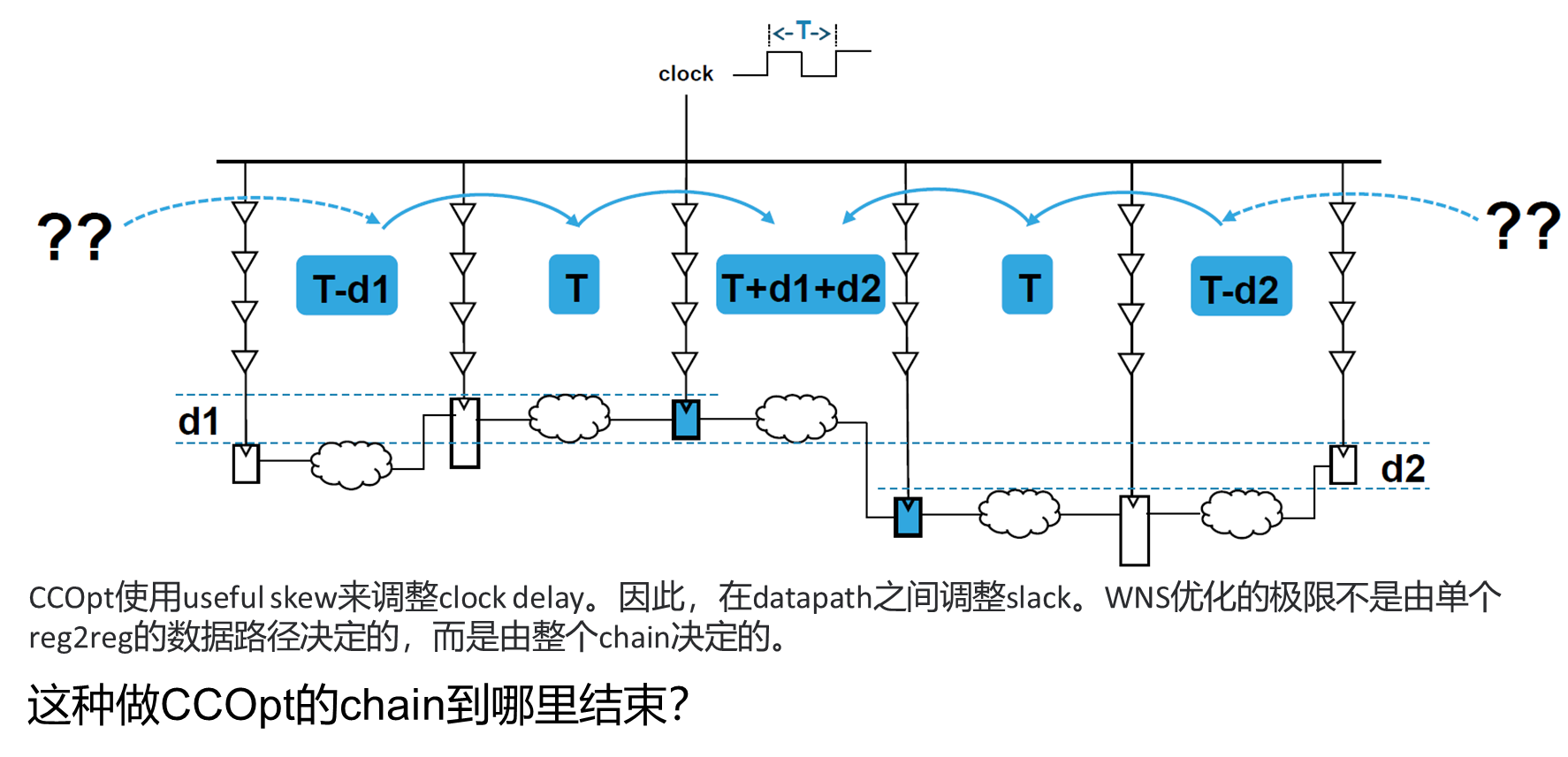

CCOpt (Chain的介绍)

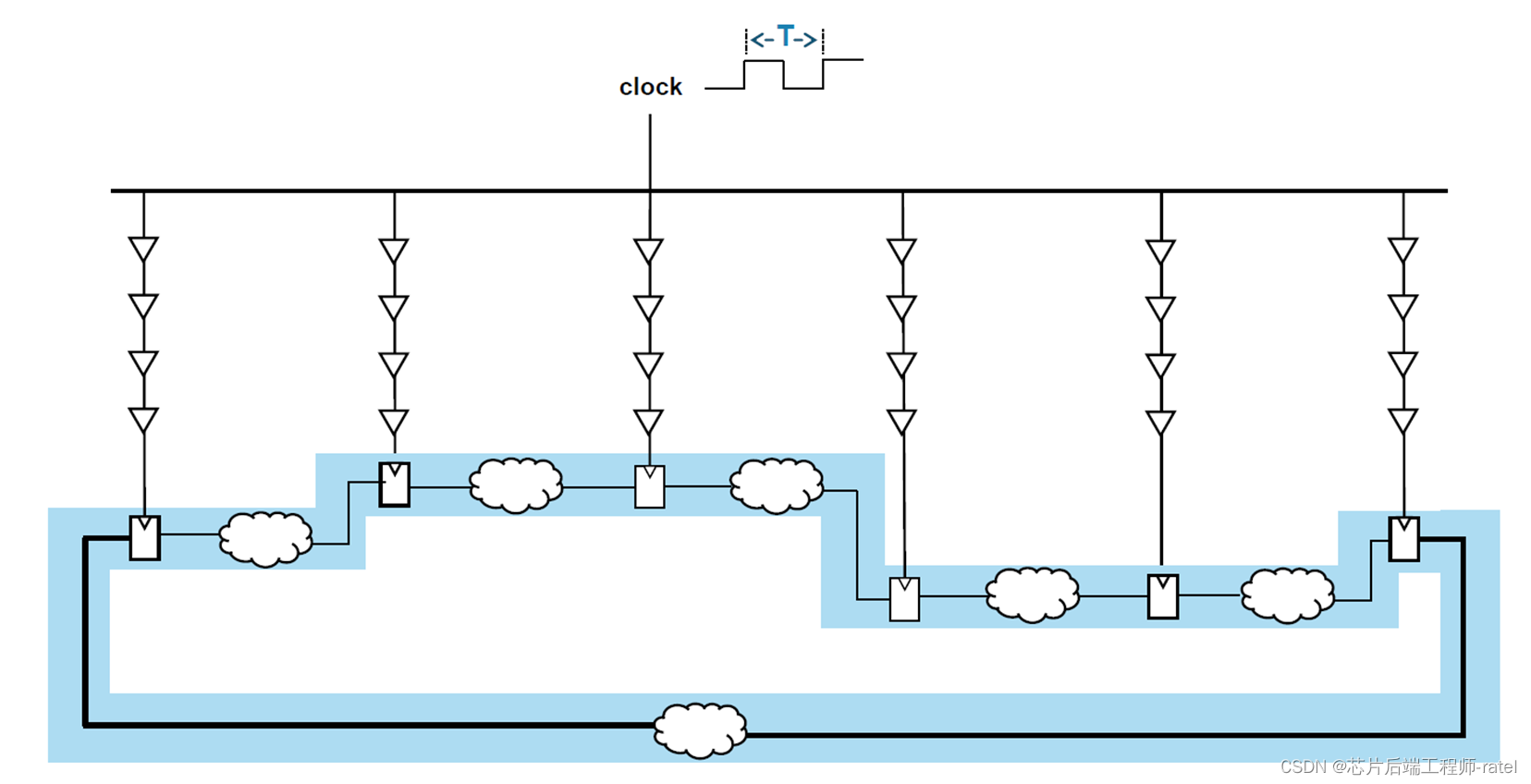

主要可以分为两类:IO chain和Loop chain

IO chain:

Loop chain:

可分为以下三种:

1.普通loop chain

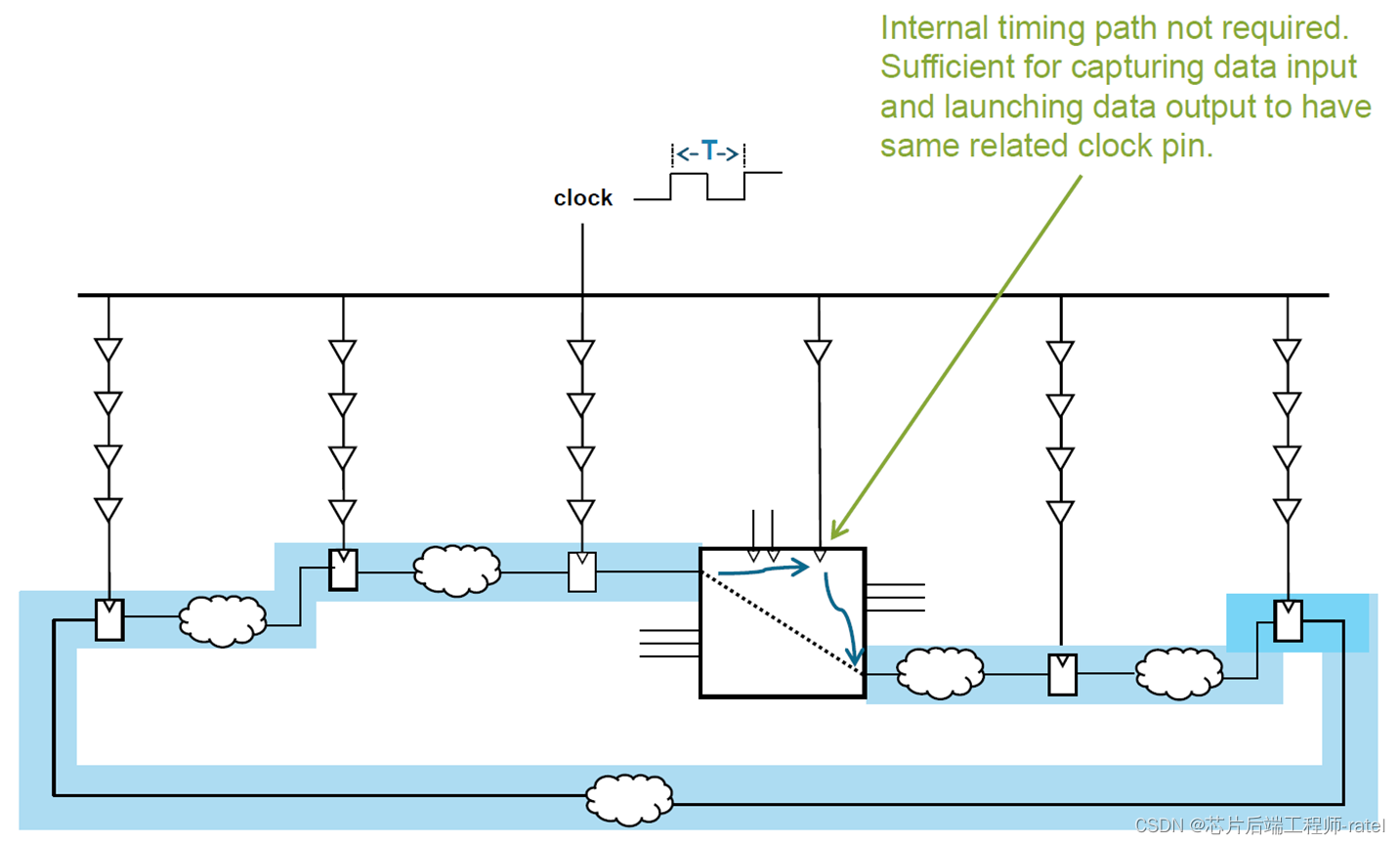

2.带macro chain

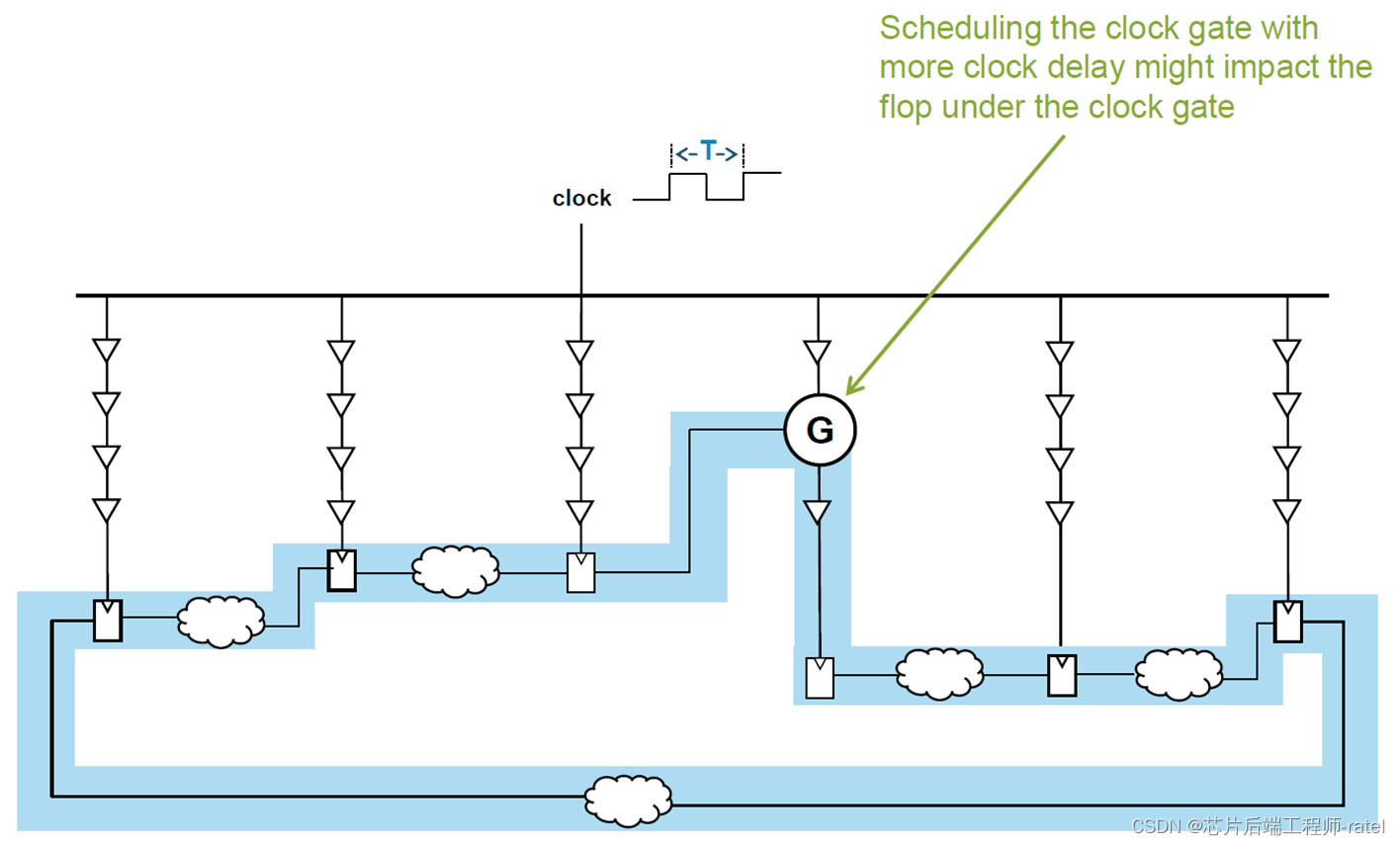

3.带ICG chain

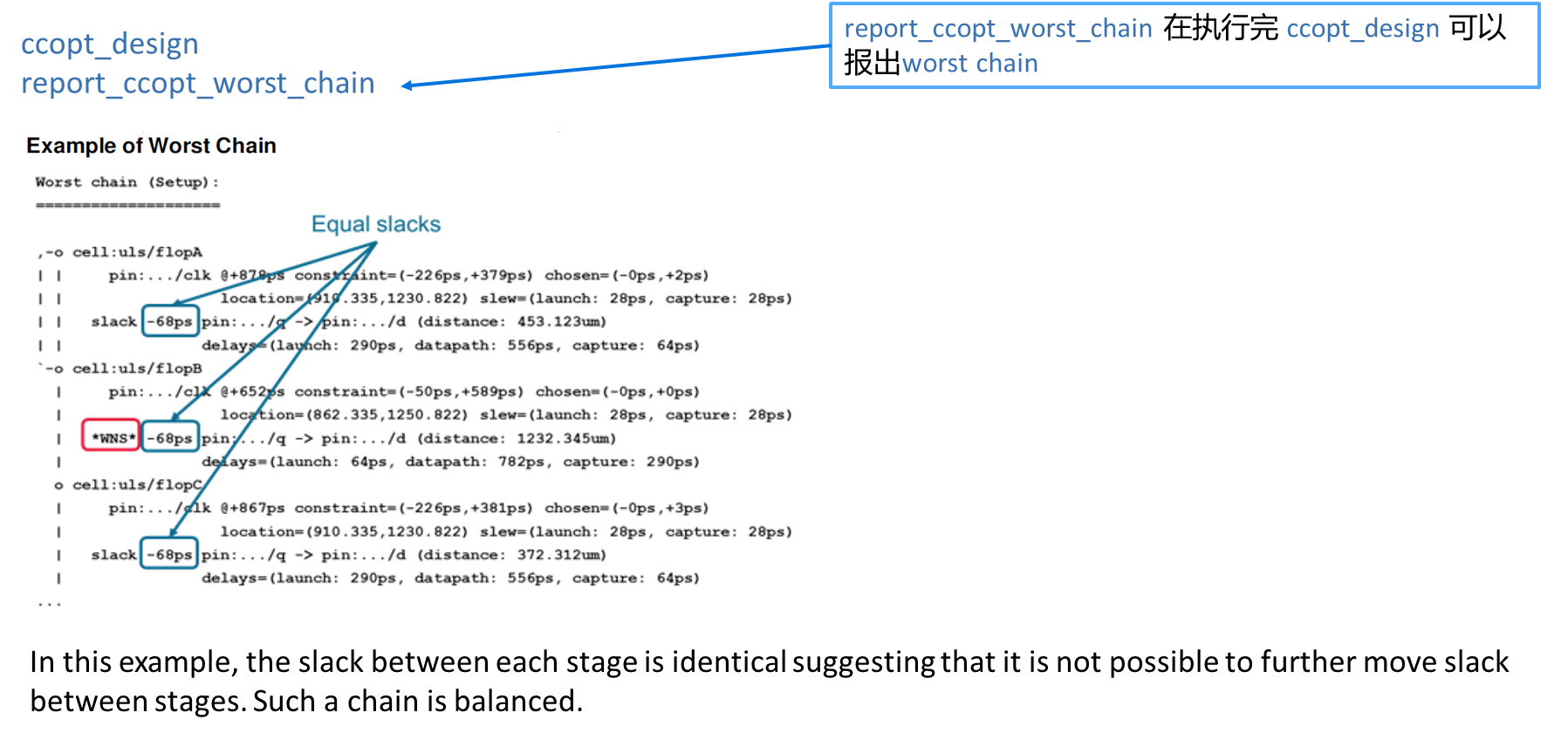

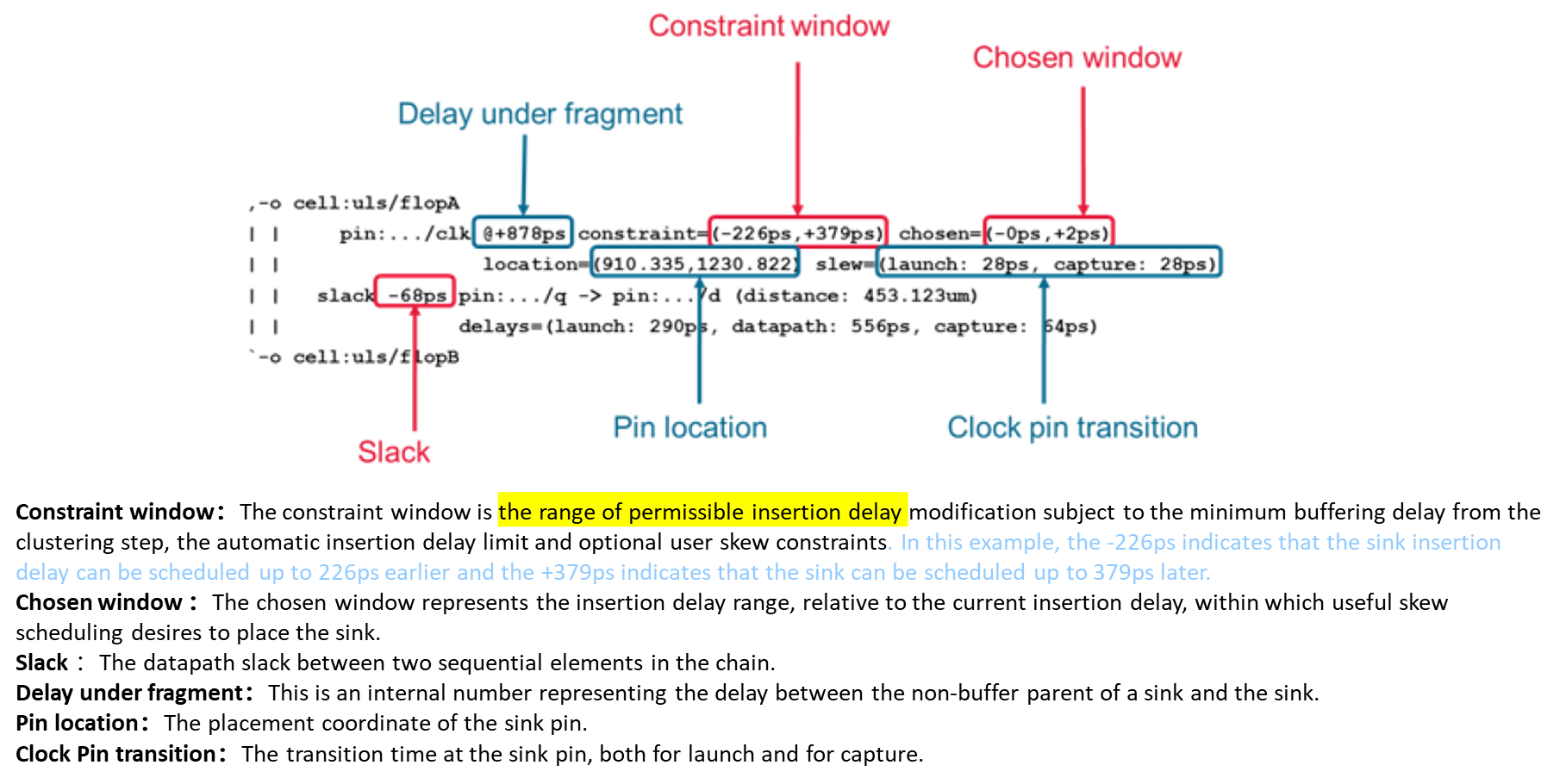

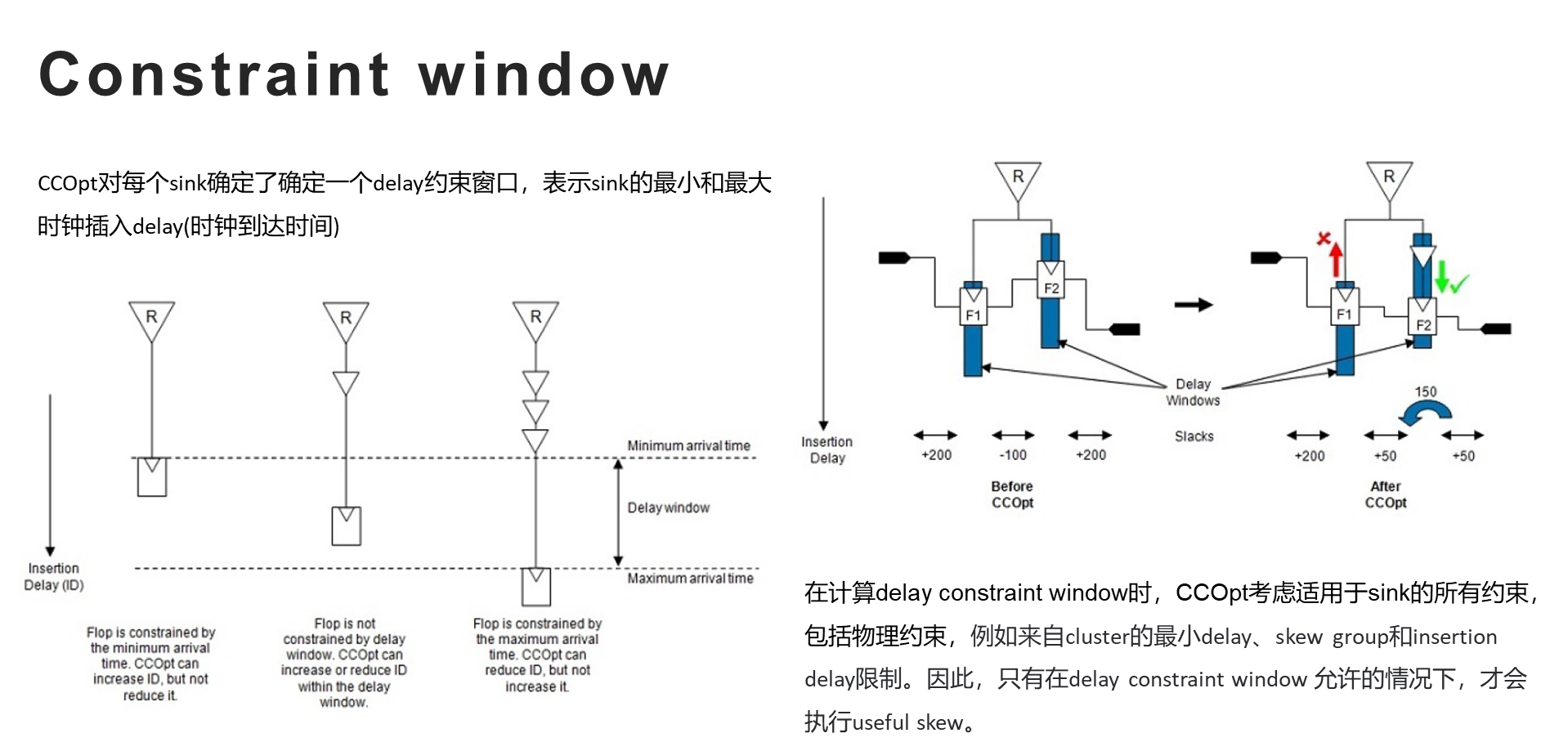

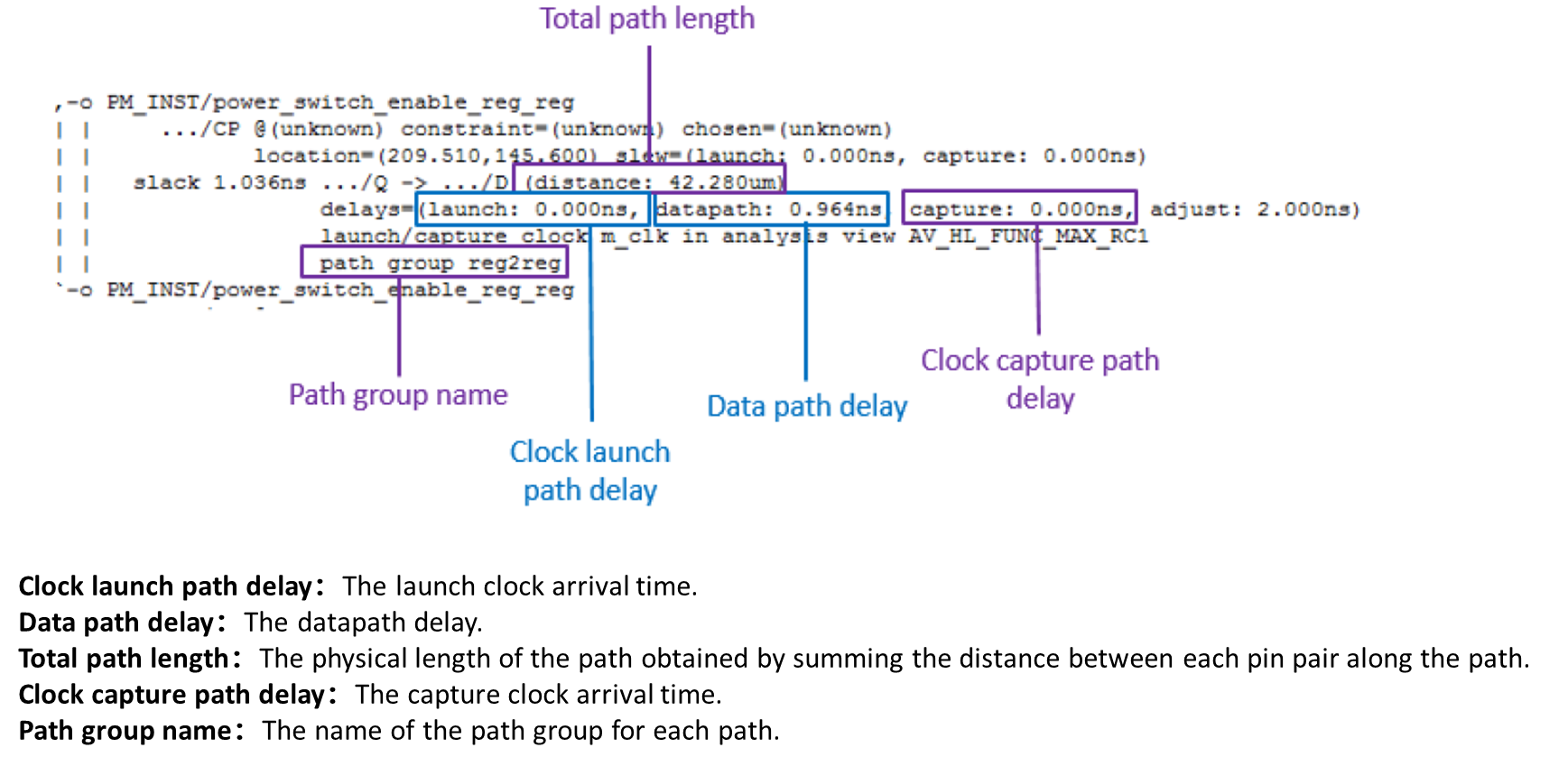

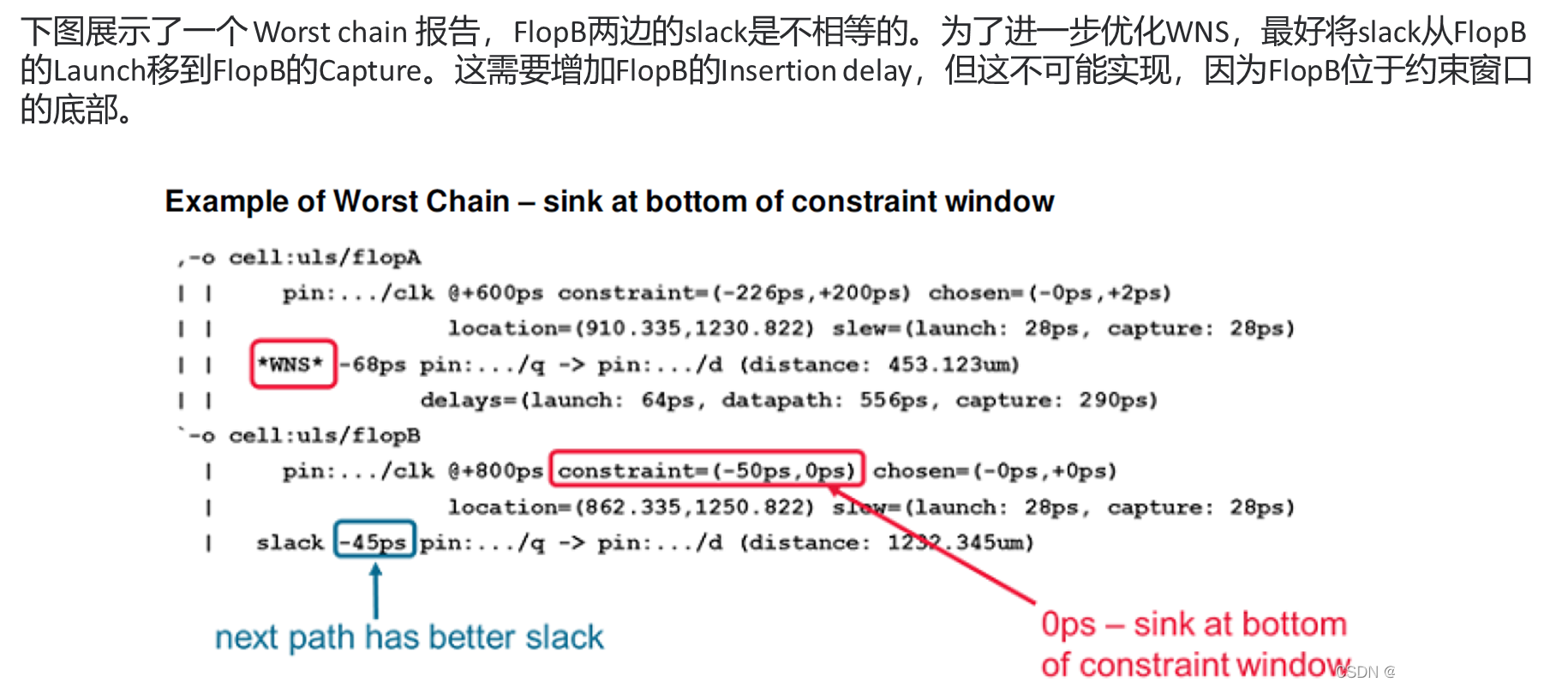

Worst chain analysis

常用命令介绍:

自定义时钟网络边界

set_ccopt_property sink_type {stop, ignore, exclude} –pin

stop:cts在该点停止,把这个pin作为skew group的sink,会对其做balance

ignore:cts只对这个pin做cluster,不做balance,ignore pin不会作为任何skew group的sink

exclude:cts在该点停止,该点不是时钟的一部分,不对其做balance