第二部分在:初学 PCIe System (二) - 如何访问PCIe设备的配置空间

PCI Express 介绍

PCI Express (PCIe) 属于第三代的高效能 I/O 汇流排,PCIe Spec对其的介绍是:

PCI Express is a high performance, general purpose I/O interconnect defined for a wide variety of future computing and communication platforms.

PCI Express 为各种未来的计算和通信平台所定义的高性能、通用互连 I/O 。

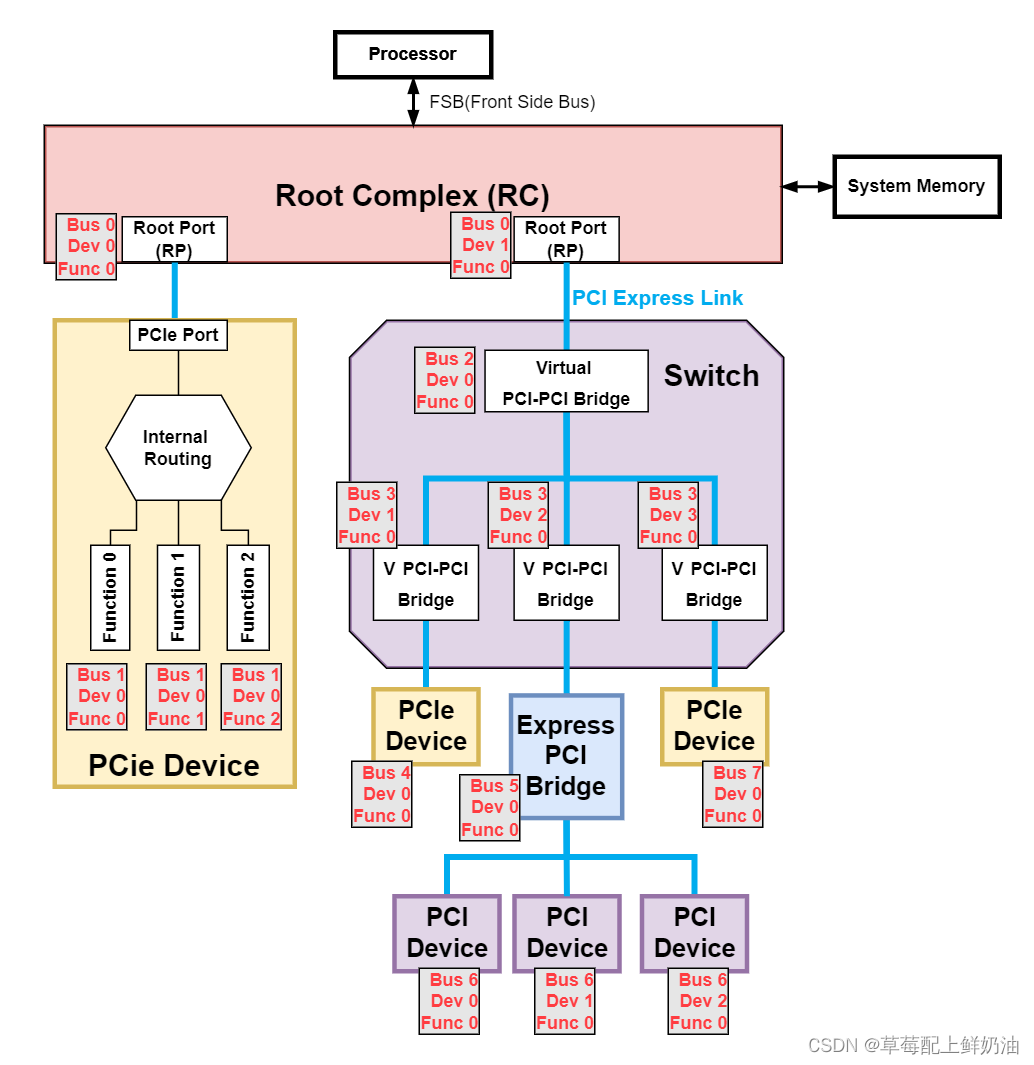

因此一个PCIe 系统就是指由许多设备相互透过 PCIe 点对点连接所组成的。如下图范例,其结构是由一个Root Complex (RC)、多个Endpoints、Bridge和Switches所组成。

- Root Complex (RC):I/O 层次结构的根,负责将 CPU/Memory子系统连接至 I/O ,可视为一虚拟的PCIe Bus(Bus-0)。 RC 比较偏向软体的概念,在x86 架构伺服器上,硬体部分是由CPU和PCH所共同实现。

- Switch:多个虚拟 PCI-to-PCI 桥设备的逻辑组合

- Endpoints:指一种Function 类型,可作为 PCIe 交易(Transaction)的请求者(Requester)或完成者(Completer)。

*Transaction 中文我一直不知道怎么翻译会比较好,在电脑科学中,讯息传送通常是点对点的,传送端和接收端的一次完整讯息沟通,包含了事前握手、讯息交换、和结束沟通,整个过程就称之为Transaction。

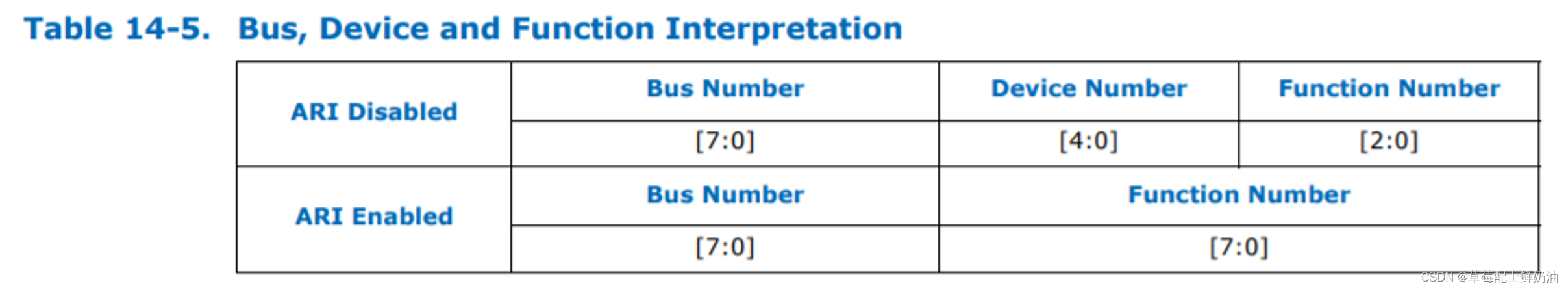

系统在开机之后,会透过深度优先演算法(DFS)去扫描目前系统上有哪些PCIe Device,并为他们定址。 PCIe Device的地址是由两个byte,并分为三个部分所组成的:

- Bus Number(8 bits) :PCI Express 将逻辑 PCI 总线编号映射到 PCI Express Link

- Device Number(5 bits) : 对于非 ARI 设备,PCI Express 组件仅限于在其主接口(上行端口)上实现单个设备编号

- Function Number(3 bits) :PCI 被允许在该设备编号内实现多达八个独立的功能

因此一个PCIe Device的地址 = bus << 8 | dev << 5 | func

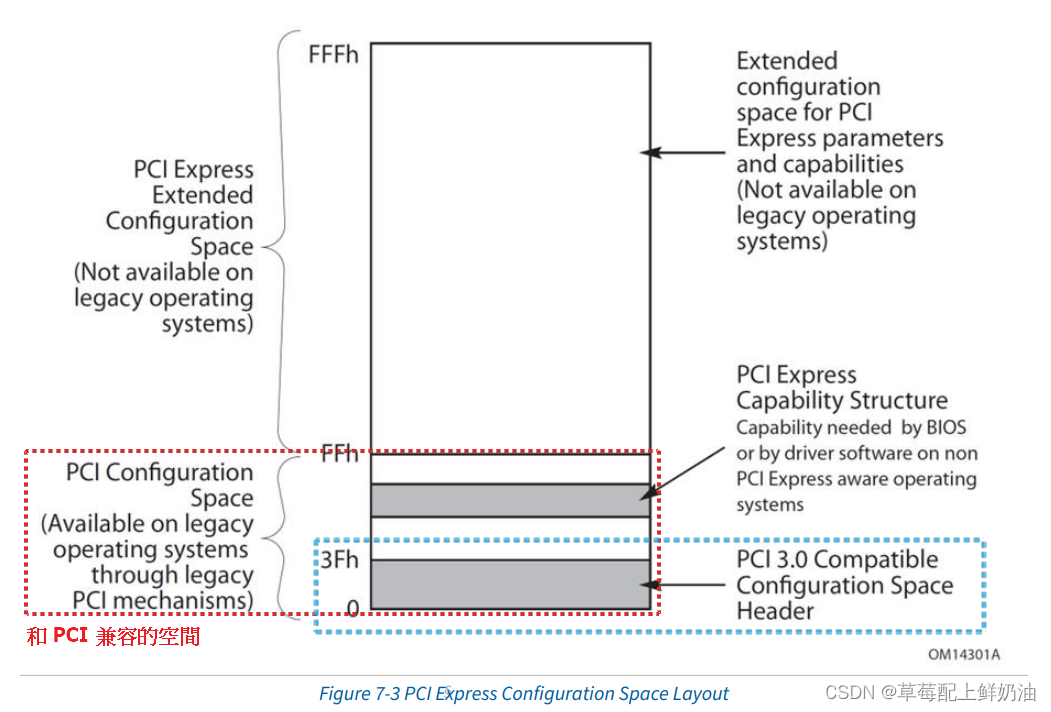

PCIe 配置空间 (PCIe Configuration Space)

PCIe Spec中定义:每个PCIe Function都有 4096 Byte 的配置空间(Configuration Space)。前256 Bytes 是和 PCI 兼容的空间,剩余的为PCIe 扩展配置空间(Extended Configuration Space)。其中前 256 Bytes PCI 兼容的空间是为software-driven的初始化和配置提供的,通常可以透过I/O Programming 或是 Direct Memory Access (DMA) 访问。

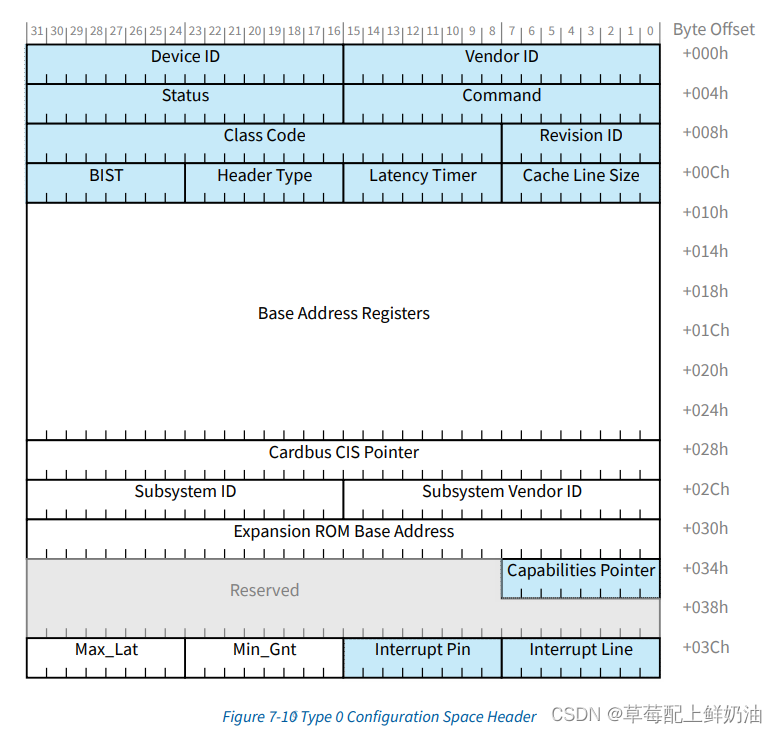

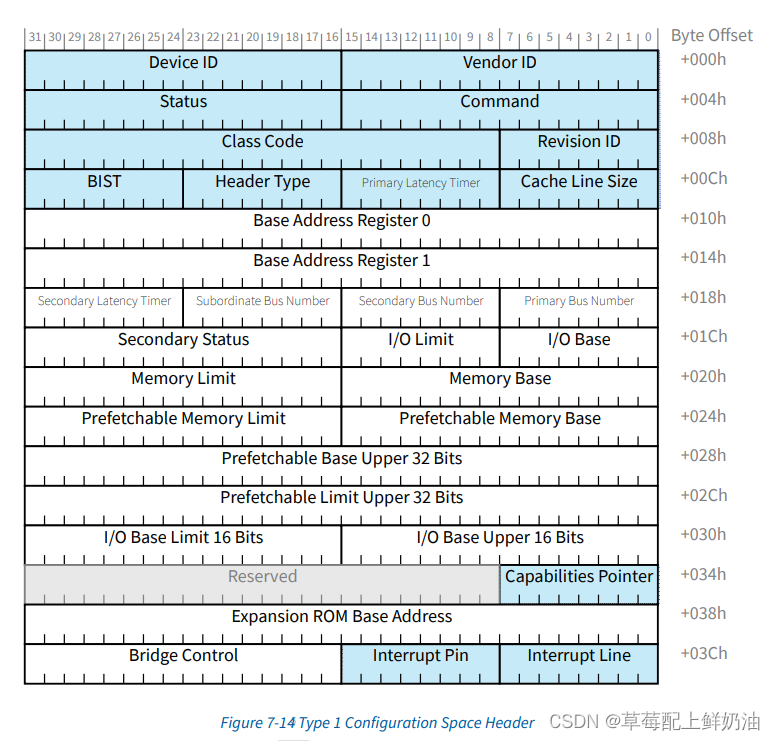

另外,在offset 0x00-0x3F的空间为Header(蓝色框部分), 他的内容格式可分为type 0 和 type 1两种,上色部分为他们共同的部分

Type 0 主要为Endpoints,例如PCI Express Endpoint、Legacy PCI Express Endpoint、RCiEP、Root Complex Event Collector

Type 1主要为Root Complex、Switch和Bridge

我们可以透过访问Configuration Space Header得到许多重要的资讯,例如:

- Vendor ID Register (Offset 00h):Vendor ID是 HwInit,标示函数的制造商,可以从Member Companies | PCI-SIG (pcisig.com) 输入ID查找制造商

- Device ID Register (Offset 02h):Device ID 是 HwInit,标示函数的功能。 Device ID 与Vendor ID 和Revision ID 一起用作应加载哪个驱动程序的一种机制。

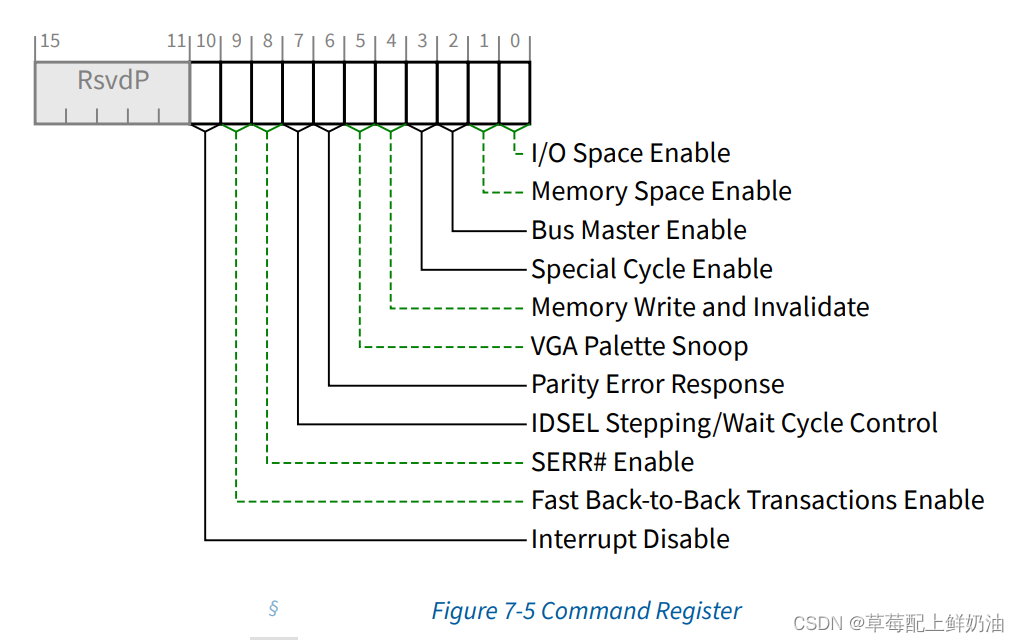

- Command Register (Offset 04h):Individual bits in the Command Register may or may not be implemented depending on the feature set supported by the Function.

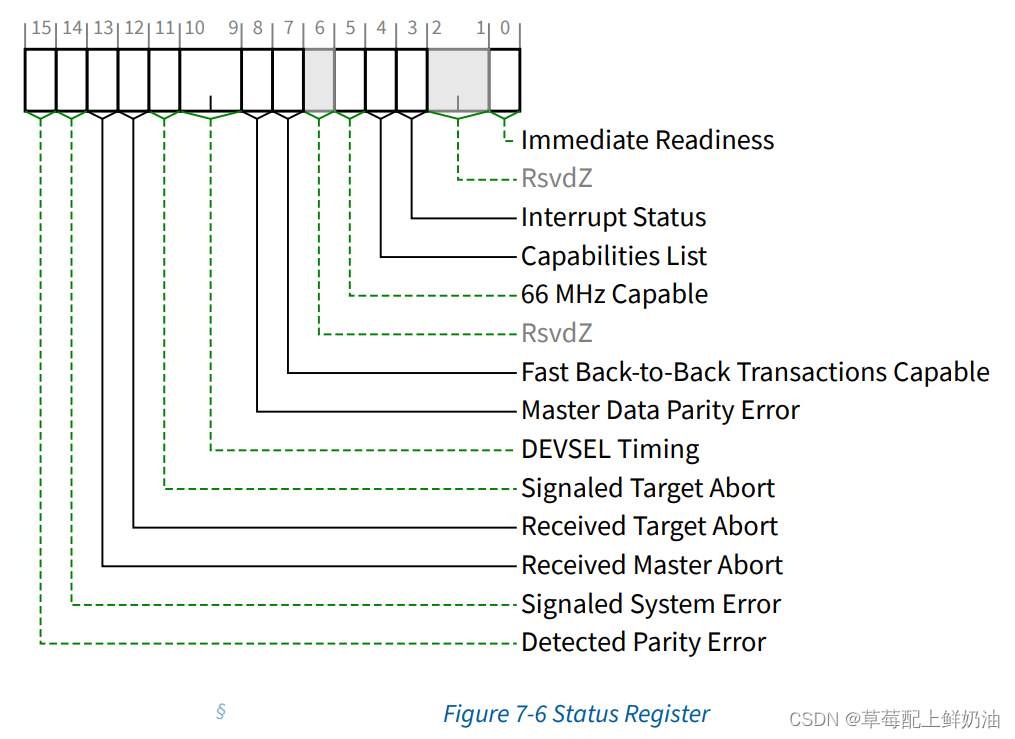

- Status Register (Offset 06h):Functions may not need to implement all bits, depending on the feature set supported by the Function.

- Revision ID Register (Offset 08h) :Revision ID 是 HwInit。 Device ID 与Vendor ID 和Revision ID 一起用作应加载哪个驱动程序的一种机制。

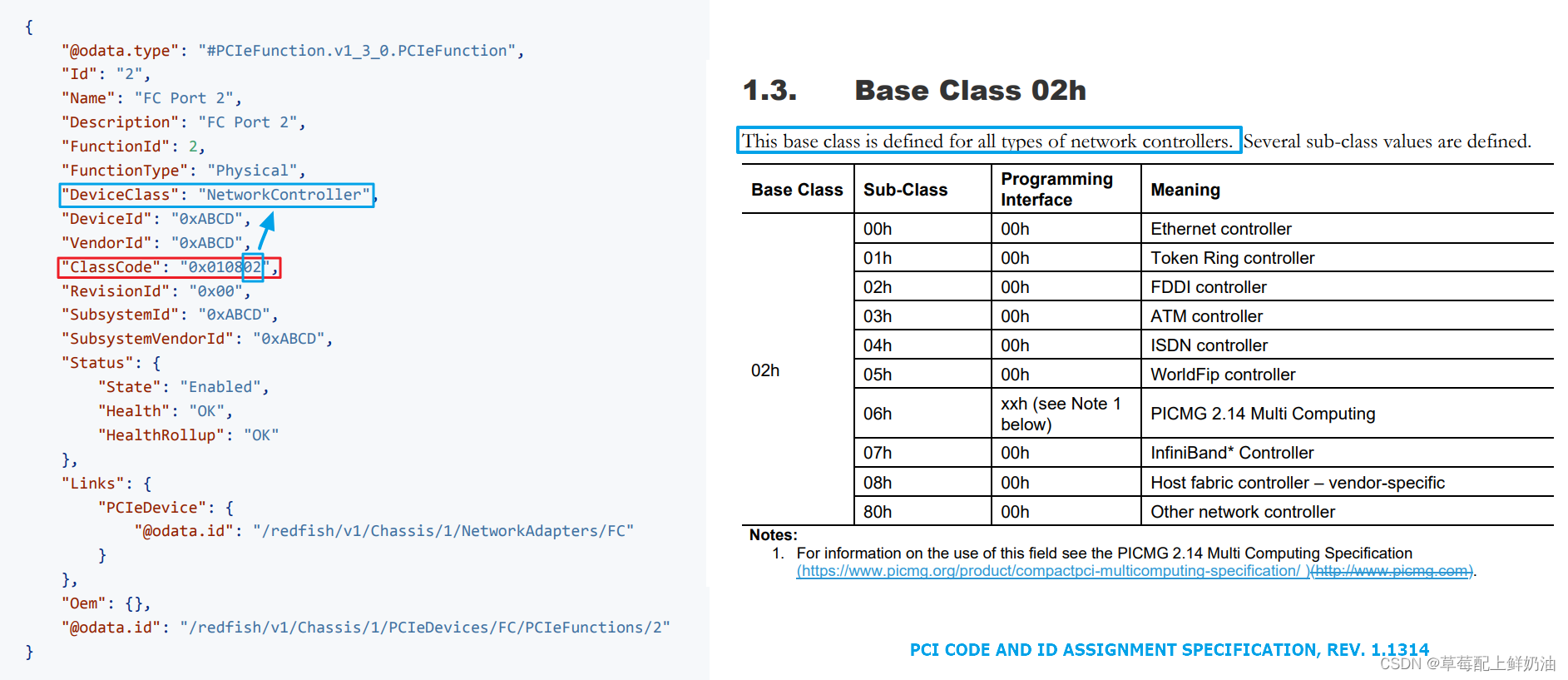

- Class Code Register (Offset 09h):是read-only的,用于标示Function的通用操作。由三个Byte组成:

Class Code 需要另外对照PCI-Code-and-ID 这份Spec,这边用Redfish Resource and Schema Guide (dmtf.org) 中的范例来解释,这边第三个Byte-Base Class Code为0x02,因此这个Function是一个NetworkController

- Header Type Register (Offset 0Eh):标示设备是否可能包含多个Function。

---

以上就是PCIe Configuration Space Header 的资讯内容大概,至于如何访问,会在初学 PCIe System (二) - 如何访问PCIe设备的配置空间介绍