参考教材:《计算机组成原理(第六版)》白中英主编 科学出版社

题型均为基础题

一. 论述题(共8题,64分)

1. (论述题, 8分)

8K*8位DRAM芯片组成32K*16位的存储器,试问:

(1) 数据寄存器多少位?地址寄存器多少位?

(2) 共需要多少个芯片?如何组织?

(3)需要多少根地址线?其中要多少根作片选译码信号?

(4)画出此存储器与CPU的连接图。需要标注MREQ和读写信号。

(每问2分)

1)数据寄存器16位、地址寄存器15位(32K--2^15);

2)8片,2片一组构成8K*16位,共4组;

3)A12~A0共13根地址线共用,A13、A14二根地址线作为片选译码信号

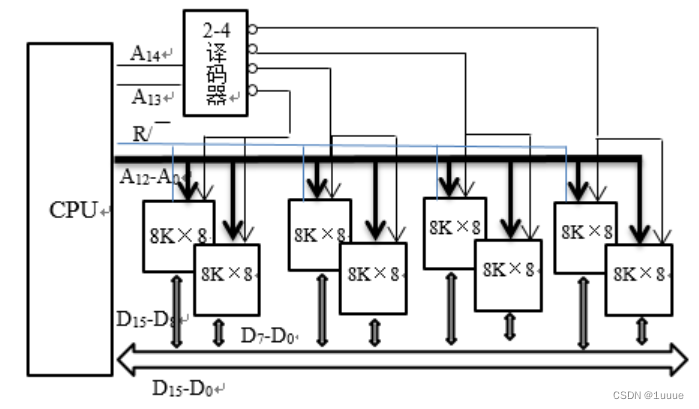

4)图中MREQ非需要连接到2-4译码器也要标出【此图为基础原理框图】

2. (论述题, 8分) 在一个分页虚存系统中,用户虚地址空间为512页,页长为2KB,主存物理为64KB。

已知用户程序有10页长,若虚页0、1、2、3已经被调入到主存4、7、8、10页中。

请问:

1)物理地址和虚地址的格式。

2)虚地址01883和4BCD(十六进制)对应的物理地址是多少?

(每问4分)

(1)地址空间分配情况

页长2KB—211,页内地址11位

物理地址空间:

64KB/2KB=32页—25, 页面地址5位,页内地址11位,共16位地址码

虚地址空间:

512页—29,页面地址9位,页内地址11位。共20位地址码

(2)地址对应情况

当前内存状况在反映在页表中,页表的内容 为4、7、8、10

虚地址01883H=0000 0001 1000 1000 0011B,页面号为3,查表得已被调入到主存页10,

所以,物理地址中的页面号为10,页内地址与虚地址的页内地址相同,

所以物理地址是:101 0000 1000 0011B=5083H

虚地址4BCDEH=0100 1011 1100 1101 B,页面号为9,查表,发现该页未被调入到主存中,所以无物理地址,会发生缺页中断。

3. (论述题, 8分)

设主存容量为512K字,CACHE容量为2K字,块长为16个字。

1)在直接映射方式下,设计主存地址格式。

2)在直接映射方式下,字地址为01234H的单元调入Cache,该地址的标记。

3)直接映射的优缺点。

4)全相联映射下,主存格式。

5)4路组相联映射下,主存格式。

(1) 主存容量512K字,地址位数19;块长16字,位数为4

Cache容量2K字,共有2K/16=128块,行地址可用7位表示

标记位数为19-7-4=8

在直接映射方式下,设计主存地址格式为

标记

行地址

块内地址

8

7

4

(2) 在直接映射方式下,

字地址为01234H= 000 0001 0010 0011 0100,前8位00000010为标记,即02H。

(3)直接映射的优点是硬件简单、成本低。 缺点是每个主存块只能调入Cache中固定的行,如果Cache容量小,会出现内存块频繁调入调出Cache的情况。

(4)在全相联映射方式下,主存地址格式为

标记

块内地址

15

4

(5)Cache容量2K字,共有2K/16=128块,4路组相联,128/4=32组,组地址可用5位表示

标记位数为19-5-4=10

在组相联映射方式下,设计主存地址格式为

标记

组地址

块内地址

10

5

4

4. (论述题, 8分) 某微程序控制器中,微指令采用水平格式,微命令编码方法采用字段直接译码法,共有20个微操作控制信号,构成3个相斥类的微命令组,各组分别包含5、7、8个微命令。已知可判定的外部条件有两个,微指令的下地址字段直接给出后续微指令地址,微指令字长20位。

1)按水平型微指令格式设计微指令。

2)画出微程序控制器原理框图。

3)计算控制存储器容量

1)按水平型微指令格式设计微指令

直接译码法中,微命令编码时全0保留不用,所以5、7、8个微命令构成的3组分别需要

5+1——3位 7+1——3位 8+1——4位

判定条件有2个,加上直接地址,需要2位。

下地址字段的位数为 20-(3+3+4)-2=8

微指令格式为

5个微命令 7个微命令 8个微命令 2个判定条件

操作控制字段

条件测试

下地址

3位 3位 4位 2位 8位

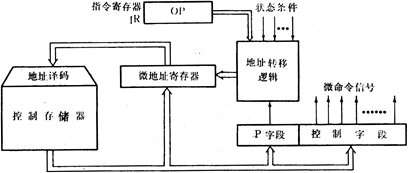

2)微程序控制器原理框图

3)计算控制存储器容量

下地址8位,最多可有2^8条微指令,

每条微指令字长20位

容量:2^8*20/8=640B

5. (论述题, 8分)

设某机有5级中断:L0、L1、L2、L3、L4,其中中断响应优先次序为:L0到L4,L0最高,L4最低,现在要求将中断处理顺序改为L1、L3、L0、L4、L2,试问:

(1)下表中各级中断处理程序的各中断级屏蔽值如何设置(每级对应一位,该位为“0”表示允许,该位为“1”表示中断屏蔽?

(2)如这5级中断同时都发出中断请求,按更改后的次序画出进入各级中断处理程序的过程示意图。并叙述处理过程。

中断处理程序 |

中断处理屏蔽位 |

||||

I0级 |

I1级 |

I2 |

I3 |

I4 |

|

I0 |

|||||

I1 |

|||||

I2 |

|||||

I3 |

|||||

I4 |

|||||

(1)处理程序中需屏蔽本级和低级中断,各级中断处理程序的屏蔽值设置如下表:

中断处理程序

中断处理屏蔽位

I0级

I1级

I2

I3

I4

I0

1

0

1

0

1

I1

1

1

1

1

1

I2

0

0

1

0

0

I3

1

0

1

1

1

I4

0

0

1

0

1

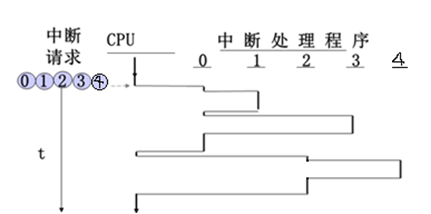

(2)若这5级中断同时发出中断请求,按优先次序先调用L0,L0屏蔽了本级和低级中断请求,而L1的中断请求未屏蔽,则L1发生中断嵌套响应;L1中断时,不允许任何中断,服务完毕后,退回到L0的中断服务程序,这时,允许L3的中断嵌套响应;L3服务完毕后,返回L0中断服务程序;L0服务完毕后,按照顺序应处理L2,进入L2的处理程序,L2被L4中断,执行L4级中断服务程序;L4执行完毕,执行L2的处理程序。

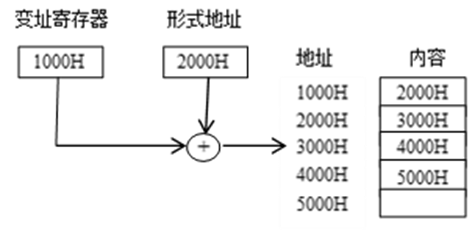

6. (论述题, 8分) 若变址寄存器R的内容为1000H,指令中的形式地址为2000H,地址1000H中的内容为2000H,地址2000H中的内容为3000H,地址3000H中的内容为4000H,地址4000H中的内容为5000H,则变址寻址方式下访问到的操作数是多少?请画图回答问题。

变址寻址的有效地址为变址寄存器的内容加上偏移,即1000H+2000H=3000H

3000H中保存的内容为4000H,故操作数为4000H

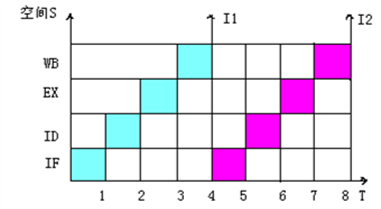

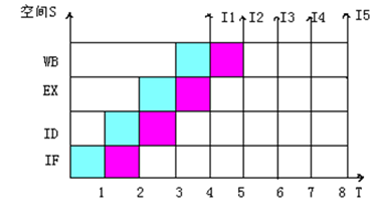

7. (论述题, 8分) 指令流水线有取指(IF)、译码(ID)、执行(EX)、写回 (WB)四个过程,共有10条指令连续输入此流水线。

(1)画出指令周期流程图

(2)画出非流水线时空图

(3)画出流水线时空图

(4)假设时钟周期为100ns,求流水线的实际吞吐率(单位时间里执行完毕的指令数)。

(1)指令周期包括4个子过程,流程图如下。

(2)非流水CPU时空图

(3)流水CPU时空图

(4)第一条指令输出结果需要4个周期,其他指令仅需要一个时钟,故实际的吞吐率为

10/[(4+9)*100ns]=7.7*106条/秒

8. (论述题, 8分) 今有4级流水线,分别完成取指、指令译码并取数、运算、送结果四步操作。假设完成各步操作的时间依次为100ns、100ns、80ns、50ns。请问:

① 流水线的操作周期应设计为多少?

② 若相邻两条指令发生数据相关,硬件上不采取措施,那么第2条指令要推迟多少时间进行?

③ 如果再硬件设计上加以改进,至少需推迟多少时间?

④ 设共有20条指令流入此流水线,求流水线的实际吞吐量(单位时间内执行完毕的指令条数)

⑤ 设共有20条指令流入此流水线,求流水线的加速比。(非流水时间/流水时间)

① 流水线的操作周期应设计为多少?

流水线的操作周期应按各步操作的最大时间来考虑,即流水线时钟周期性 ,故取100ns。

② 若相邻两条指令发生数据相关,硬件上不采取措施,那么第2条指令要推迟多少时间进行?

遇到数据相关时,就推迟第2条指令的执行;

要推迟到所需读取的数据已产生为止,因此至少需要延迟2个时钟周期。

③ 如果再硬件设计上加以改进,至少需推迟多少时间?

如采用专用通路技术,应保证取数之前结果已计算出来;

因此,至少需要延迟1个时钟周期。

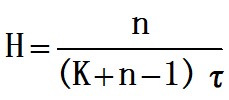

流水线实际吞吐量

④ n=20,k=4, t=100ns H=20/((4+20-1)*100*10^-9)=8.70*10^6条/s

⑤流水线加速比 n=20,K=4, S=20*4/(4+20-1)=3.48

二. 计算题(共7题,36分)

9. (计算题, 5分)

求十进制数-17的原码表示,反码表示,补码表示和移码表示(用8位二进制表示,并设最高位为符号位,真值为7位)。

17 =(10001)2

-17

原码 10010001

反码 11101110

补码 11101111

移码 01101111

10. (计算题, 6分) 已知x=1011,y=-1000,用变形补码计算x+y,x-y 并指出是否溢出。

变形补码,双符号位

故[X]补=001011 [Y]补=111000

[X+Y]补=[X]补+[Y]补

00 1011

+ 11 1000

00 0011

符号位为00,无溢出 X+Y=0011

[X-Y]补=[X]补+[-Y]补

[X]补=001011 [-Y]补=00 1000

00 1011

+ 00 1000

01 0011

符号位为01,正溢出

11. (计算题, 5分) 设x=+9,y=-7,用带求补器的补码阵列乘法器计算X×Y。

[X]补=01001 [Y]补=11001算前求补器输出为 |X|=1001 |Y|=0111

1001

× 0111

1001

1001

1001

+ 0000

0111111

符号位单独计算 0⊕1=1,

算后求补器输出为

[ X×Y]补=111000001 = -28+27+26+1=-256+128+64+1=-63

验算 X=9 Y=-7 X×Y=-63 (可不验算)

12. (计算题, 5分) CPU执行一段程序时,cache完成存取的次数为3800次,主存完成存取的次数为200次,已知cache存取周期为50ns,主存为250ns,求cache / 主存系统的效率和平均访问时间。

命中率 H = Ne / (NC + Nm) = 3800 / (3800 + 200) = 0.95

主存慢于cache的倍率 :r = tm / tc = 250ns / 50ns = 5

访问效率 :e = 1 / [r + (1 – r)H] = 1 / [5 + (1 – 5)×0.95] = 83.3%

平均访问时间 :ta = tc / e = 50ns / 0.833 = 60ns

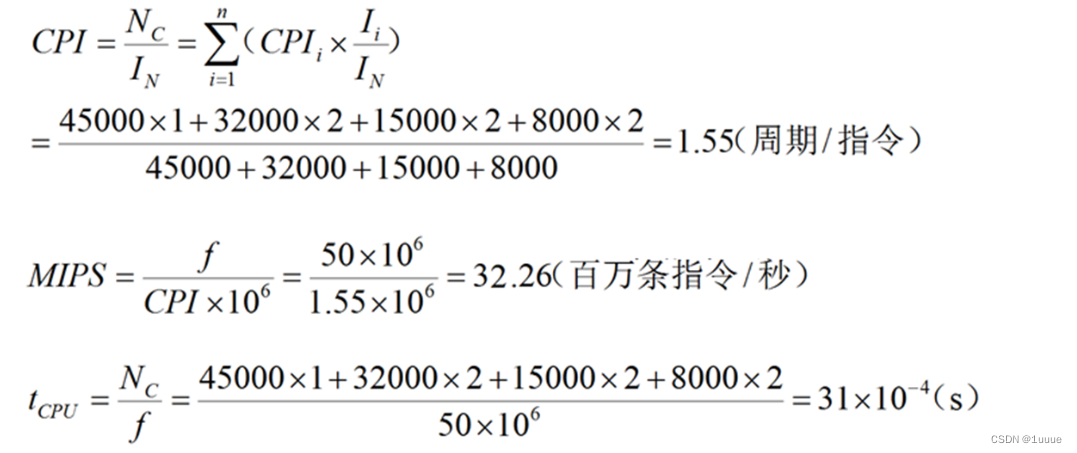

13. (计算题, 5分) 用一台50MHz处理机执行标准测试程序,它包含的混合指令数和相应所需的平均时钟周期数如表所示

求有效CPI、MIPS速率、处理机程序执行时间tcpu.

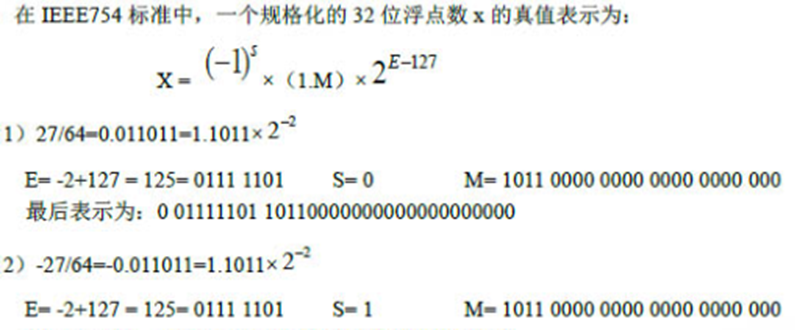

14. (计算题, 5分) 将下列十进制数表示为IEEE754标准的32位规格化数

27/64

-27/64

27转换为二进制11011

64转换为二进制1000000

27/64 转换为二进制 0.011011

表示成十六进制分别为 0011 1110 1101 1000 0000 0000 0000 0000B =3ED80000 H

表示成十六进制分别为 1011 1110 1101 1000 0000 0000 0000 0000B =BED80000 H

15. (计算题, 5分) 某IEEE754标准的32位规格化数为BED80000H,求真值。

一个规格化的32位浮点数x的真值表示为

BED80000 H=1011 1110 1101 1000 0000 0000 0000 0000B

1 011 1110 1 101 1000 0000 0000 0000 0000

数符S为1 阶码E为01111101 尾数M为1011

e=125-127=-2 真值为-1.1011*2^-2=-0.011011B=-27/64