一、RS485电路

RS485( Recommended Standard-485)是隶属于OSI模型-物理层的电气特性,规定为 2 线、半双工、平衡传输线的多点异步通信标准,通信采用差分信号传输。

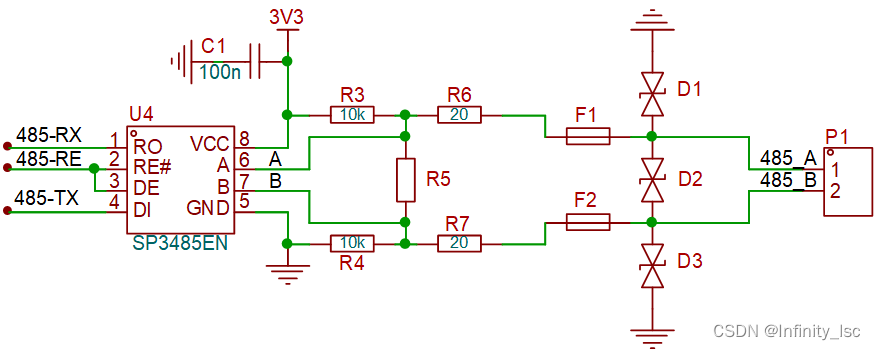

- 典型485应用电路如下图所示:

其中

、

# 分别控制接收和发送,

由于管脚 1 0 DE 发送使能 发送禁止 RE# 接收禁止 接收使能 、

# 逻辑相反,一般将

、

# 短接在一起

当 485-RE 为低电平时,485处于接收状态;当 485-RE 为高电平时,485处于发送状态;通过控制 485-RE 来切换485收发状态。 - 自收发485应用电路如下图所示:

当 485_TX 为低电平时,

、

# 为高电平,485处于发送状态,DI 引脚接地,所以AB处于低电平,即向外发送低电平信号;

当 485_TX 为高电平时,、

# 为低电平,485处于接收状态,AB引脚处于高阻态,B脚被拉至GND,A脚被拉至VCC,即向外发送高电平信号。

由于 485_TX 为高电平时,

#

,485处于接收状态,因此 485_TX 只需保持为高电平即可接收数据,故自收发电路发送高电平时同时也是接收状态。

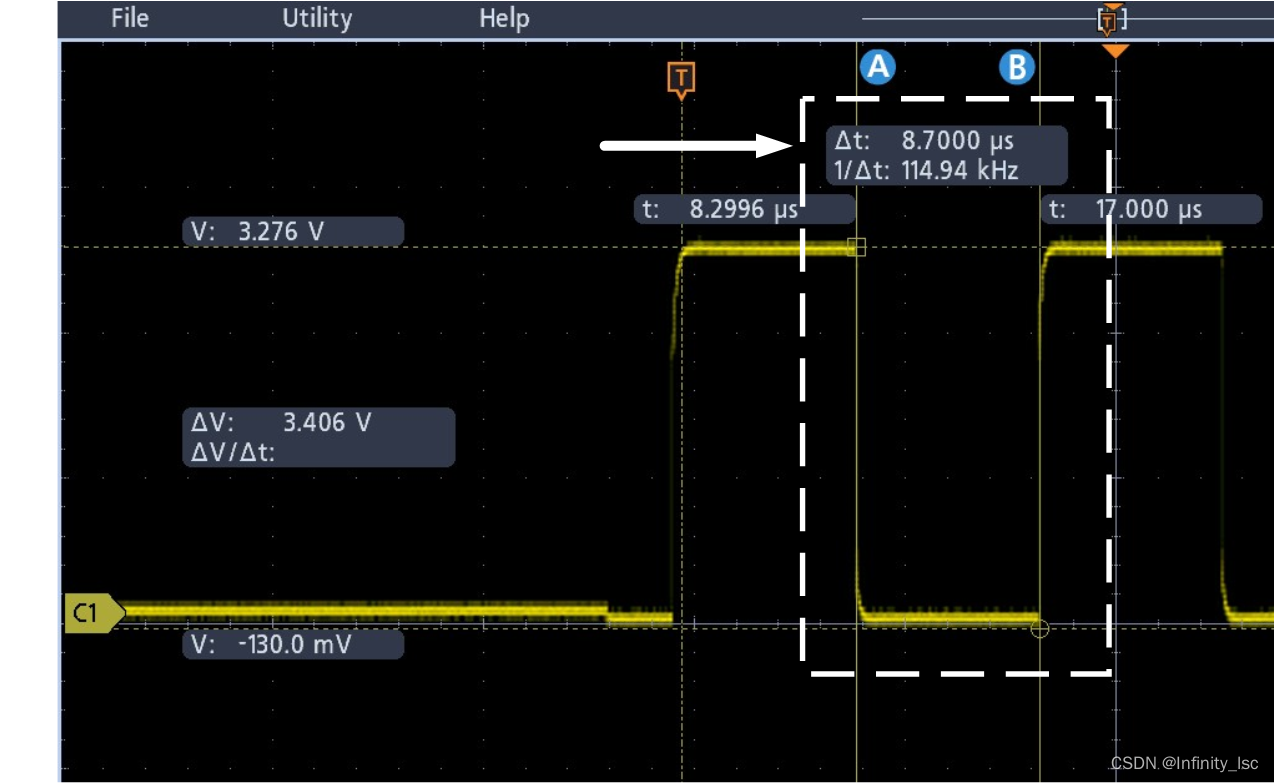

二、RS485波形

下图是RS485 输出端实测信号波形,其中,差分信号的 A、B 每个通道的共模电压值都在标准要求的-7~12V之内;

单片机 UART 发送数据为 ,模式为1个起始位,8个数据位,1个停止位,无校验位,转换为二进制为 1100 0101,从 bit0 开始逐位发送,即先发送低位,后发送高位。

其中,每 bit 占用时间为:,与测试时间一致

本文含有隐藏内容,请 开通VIP 后查看