目录

一、VGA简介

VGA,英文全称"Video Graphics Array”,译为视频图形阵列,是一种使用模拟信号进行视频传输的标准协议,由IBM公司于1987年推出,因其分辨率高、显示速度快、颜色丰富等优点,广泛应用于彩色显示器领域。

VGA接口:

母头:

公头:

VGA连接线两头都是公头:

使用VGA连接线将计算机和VGA显示器连接起来

二、VGA引脚的定义

1(红基色)、2(绿基色)、3(蓝基色)、13(行同步信号)、14(场同步信号)拐角最为重要

RGB色彩显示标准:根据三原色中红色、绿色、蓝色所占比例以及三原色相互之间的叠加来显示各式各样的颜色

三、VGA显示原理:

VGA显示器逐行扫描原理:逐行扫描是扫描从屏幕左上角一点开始,从左至右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起始位置。在这期间,CRT对电子束进行消隐,每行结束时,用行同步信号HS进行同步;当扫描完所有的行,形成一帧,用场同步信号VS进行帧同步,并使扫描回到屏幕左上方,同时进行场消隐,开始下一帧。

四、VESA标准下的VGA时序:

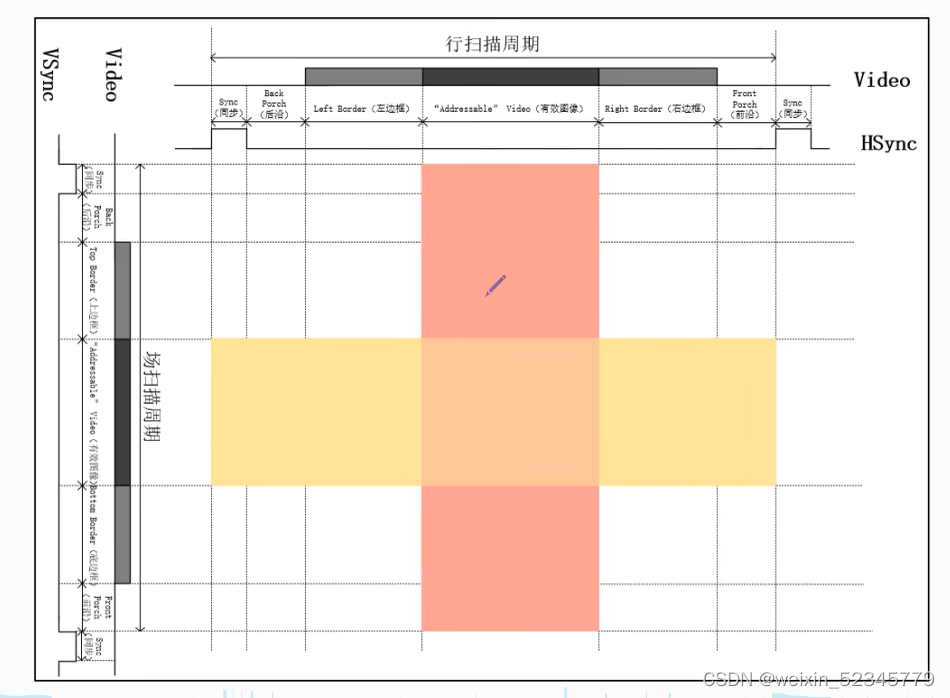

①行同步时序图

Video图像信息,GSync行同步信号

行同步信号自上升沿起到下一个上升沿止为一个周期,这个周期成为行扫描周期,一个完整的行扫描周期包含六个部分:同步、后延、左边框、有效图像、右边框、前沿。这六个部分的基本单位是一个像素,在图像传输过程中,每一个时钟周期传输一个像素点,这六个部分的基本单位也可以称作一个像素时钟周期,在一个完整的行扫描周期内,图像信息是在行同步信号的同步下完成一行图像的扫描,图像信息只有在“有效图像阶段”才是有效的,行同步信号只在同步阶段才保持高电平。

②场同步时序图

场同步信号自上升沿起到下一个上升沿止为一个周期,这个周期成为场扫描周期,一个完整的场扫描周期包含六个部分:同步、后延、左边框、有效图像、右边框、前沿。这六个部分的基本单位是一行。在一个完整的场扫描周期中,图像信息需要在行同步信号和场同步信号的共同作用下完成一帧图像的显示,图像信息只有在“场有效图像”、‘’行有效图像“两个阶段才是有效的

③VGA时序图

红色和黄色相交的位置就是VGA图像的最终显示区域

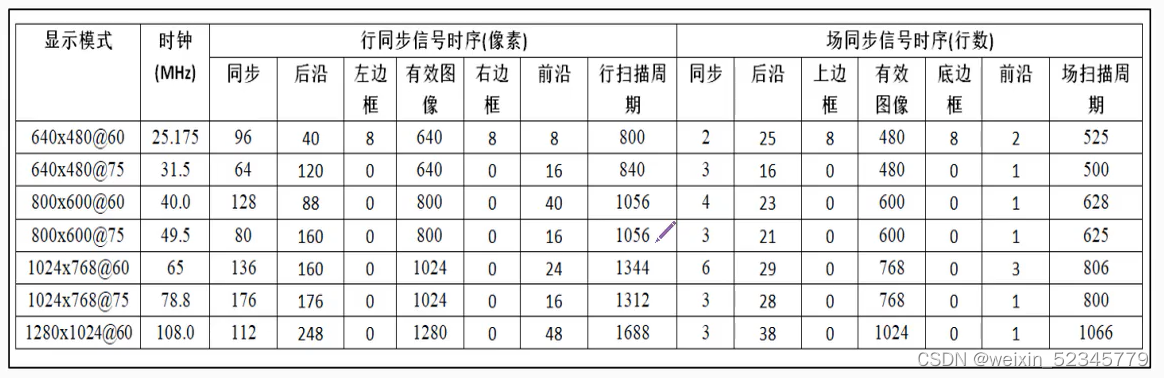

五、VGA显示模式以及相关参数:

显示模式640x480@60,640表示在一个完整的行扫描周期中,有效显示图像每一行有640个像素点,480表示一帧完整的图像有480行

640x480≈30万,表示一帧图片约包含30万个像素点,60是帧率表示在640x480@60显示模式下,每秒刷新图像60次,也就是每秒显示60帧图像。时钟25.175MHZ表示VGA显示的工作时钟,就是像素点扫描的频率,96表示在同步阶段保持96个时钟周期,40表示在后延阶段保持40个时钟周期。行扫描周期800等于行同步信号的六个阶段时钟周期相加

注:行扫描周期x场扫描周期x帧率=时钟F

例:在显示模式640x480@75中,840x500x75=31500000HZ=31.5MHZ

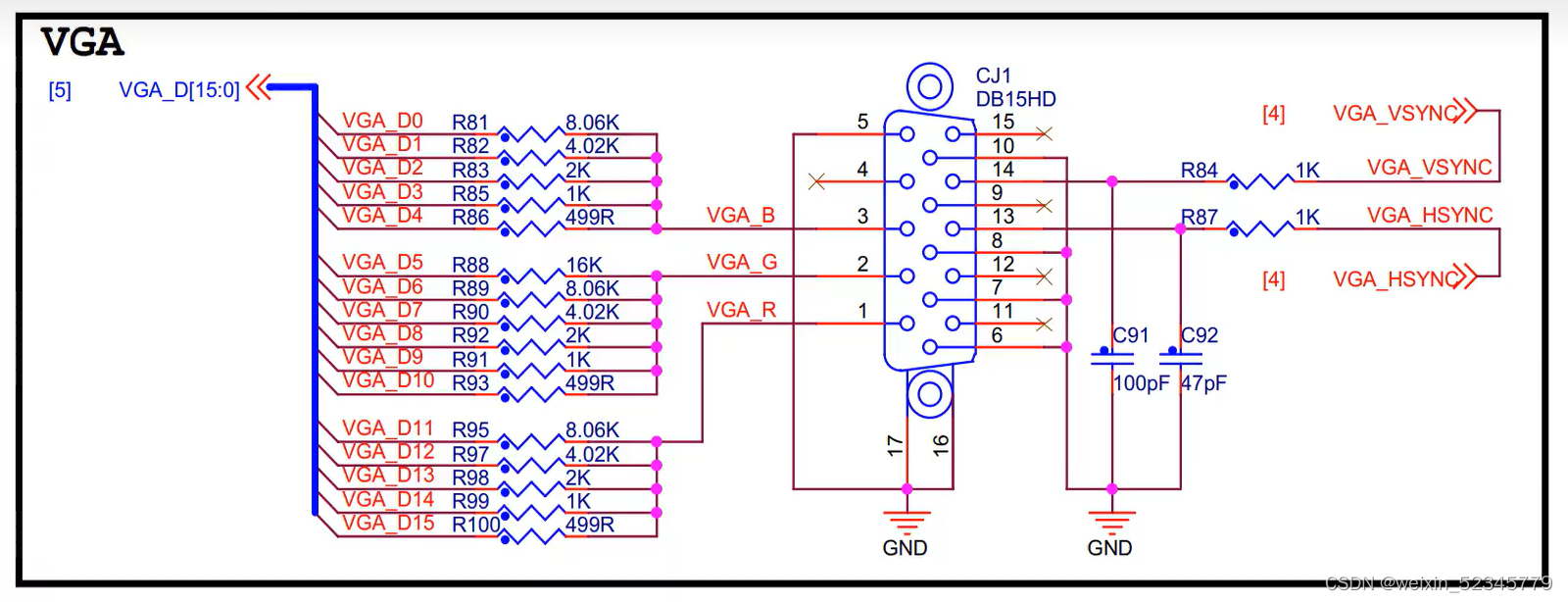

六、数字信号与模拟信号的转换

VGA传输协议传输的是模拟信号,VGA显示器只能识别模拟信号,尔FPGA处理的是数字信号,将数字信号转换为模拟限号有两种方式:AD7123等转换芯片(稳定但成本稍高)、权电阻网络(成本低)

权电阻网络原理图

征途系列开发板使用RGB565图像模式,每个像素点的位宽是16位宽(5+6+5)(红+绿+蓝),在图像显示时FPGA通过VGA_D端口将图像信号传输到权电阻网络,经过权电阻网络的数模转换,生成能够被VGA识别的图像信号VGA_R,VGA_G,VGA_B,生成的三路模拟信号的电压范围是0~0.714V,0V表示无色,0.714V表示满色

实战演练一:VGA显示彩条

1、实验目标

驱动VGA显示器,在640x480@60显示模式下显示十种颜色等宽彩条的显示

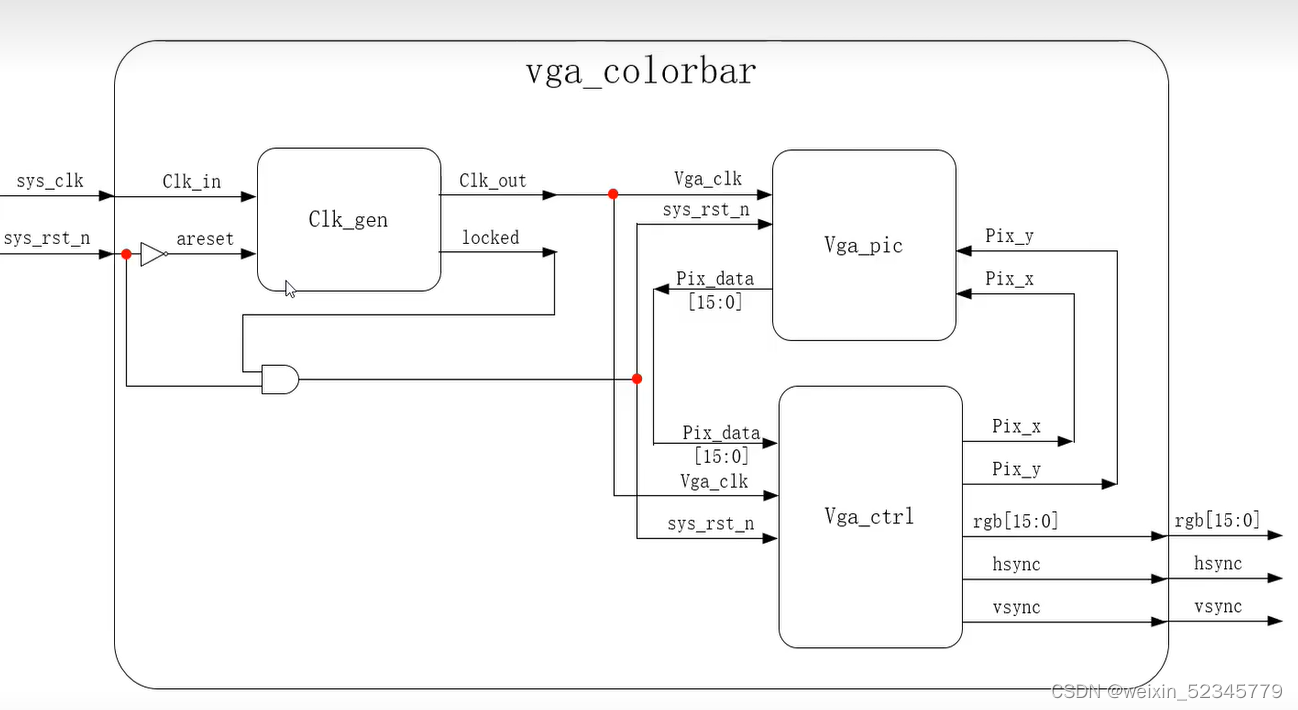

2、各模块框图及其波形图

①②顶层模块:

rgb[15:0]:图像信息,使用的是RGB565图像模式,所以位宽为16位,此信号由FPGA产生然后传输给权电阻网络

hsync:行同步信号,此信号由FPGA产生然后传输给权电阻网络

vsync:场同步限号,此信号由FPGA产生然后传输给权电阻网络

注:locked锁定信号只有为高电平的时候,分频后的时钟信号才是有效的,所以需要将系统复位信号sys_rst_n和locked进行”与''操作后再接入Vga_pic和Vga_ctrl的复位信号

②时钟分频模块:将50MHZ的系统时钟分频成25MHZ,fpga系统时钟为50MHZ,而640x480@60显示模式下时钟频率为25.175MHZ,由于25.175MHZ的频率不太方便生成。为了便于时钟的生成,这里使用25MHZ代替25.175MHZ

CLK_in:输入50MHZ的系统时钟

areset:异步复位信号

CLK_out:输出25Mhz的输出时钟

locked:锁定信号,此信号为高电平则CLK_out才可以被使用

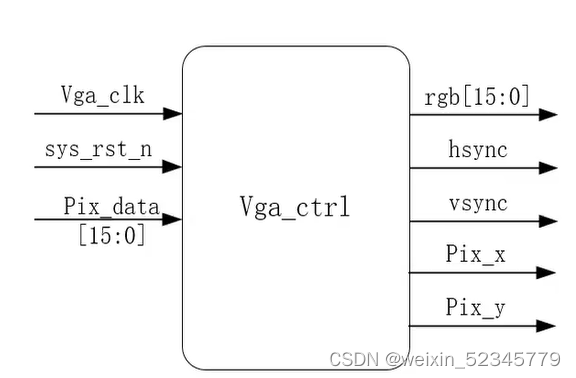

③VGA_ctrl模块:生成rgb[15:0]、hsync、vsync三路信号,以及图像的横纵坐标

Vga_clk:分频后产生的25MHZ的时

sys_rst_n:系统复位信号

Pix_data[15:0]:图像信息,和rgb[15:0]相同

rgb[15:0]:图像信息,使用的是RGB565图像模式,所以位宽为16位

hsync:行同步信号

vsync:场同步限号

Pix_x:有效图像横坐标

Pix_y:有效图像纵坐标

VGA_ctrl模块信号波形图:

cnt_h[9:0]:行计数器,对行扫描周期计数,最大值799

cnt_h[9:0]:行计数器,对行扫描周期计数,最大值799

cnt_v[9:0]:场计数器,对场扫描周期计数,行计数器完成了一个完整的行扫描周期的计数,场计数器加一,最大值524

hsync:行同步信号,在行计数器计数到0~95时(行同步阶段)时拉高,其他时间为低电平

vsync:场同步信号,在场计数器计数到0~1时(行场同步阶段)时拉高,其他时间为低电平

rgb_valid:图像有效信号,行计数器计数到有效图像范围144~783并且场计数器计数到有效图像范围35~514,此信号为高电平

Pix_x:有效图像横坐标,有效图像为高电平时,在数值上等于行计数器数值减去行同步、行后延、行边框三个阶段数值之和

Pix_y:有效图像纵坐标,有效图像为高电平时,在数值上等于场计数器数值减去场同步、场后延、场边框三个阶段数值之和

rgb[15:0]:有效图像信息,初值全零表示显示黑色,当图像有效信号rgb_valid为高电平时,rgb[15:0]=Pix_data[15:0]

图④像信息生成模块:根据有效图像坐标信息产生要显示的图像数据

vga_clk:分频后的时钟

sys_rst_n:复位信号 Pix_x:横坐标 Pix_y:纵坐标

Pix_data[15:0]:生成的图像信息

3、模块代码

clk_gen:调用pll锁相环

vga_ctrl:

`timescale 1ns/1ns

module vga_ctrl ( //VGA控制模块

input wire vga_clk ,

input wire sys_rst_n ,

input wire [15:0] pix_data ,//图像数据

output wire [9:0] pix_x ,

output wire [9:0] pix_y ,

output wire hsync ,//行扫描信号

output wire vsync ,//场扫描信号

output wire [15:0] rgb

);

parameter H_SYNC = 10'd96 , //行同步

H_BACK = 10'd40 , //行时序后沿

H_LEFT = 10'd8 , //行时序左边框

H_VALID = 10'd640 , //行有效数据

H_RIGHT = 10'd8 , //行时序右边框

H_FRONT = 10'd8 , //行时序前沿

H_TOTAL = 10'd800 ; //行扫描周期

parameter V_SYNC = 10'd2 , //场同步

V_BACK = 10'd25 , //场时序后沿

V_TOP = 10'd8 , //场时序上边框

V_VALID = 10'd480 , //场有效数据

V_BOTTOM = 10'd8 , //场时序下边框

V_FRONT = 10'd2 , //场时序前沿

V_TOTAL = 10'd525 ; //场扫描周期

reg [9:0] cnt_h ;

reg [9:0] cnt_v ;

wire pix_data_req ;

wire rgb_valid ; //图像有效信号,行扫描信号位于有效图像范围并且场扫描信号位于有效图像范围时图像有效信号为高电平

//cnt_h:行同步信号计数器

always @(posedge vga_clk or negedge sys_rst_n ) begin

if(sys_rst_n == 1'b0)

cnt_h <= 10'd0;

else if(cnt_h == H_TOTAL - 1'b1 )

cnt_h <= 10'd0;

else

cnt_h <= cnt_h + 10'd1;

end

//hsync:行同步信号

assign hsync = (cnt_h <= H_SYNC - 1'd1) ? 1'b1 : 1'b0 ;

//cnt_v:场同步信号计数器

always @(posedge vga_clk or negedge sys_rst_n ) begin

if(sys_rst_n == 1'b0)

cnt_v <= 10'd0;

else if((cnt_v == V_TOTAL - 1'd1) && (cnt_h == H_TOTAL-1'd1))

cnt_v <= 10'd0;

else if(cnt_h == H_TOTAL -10'd1 )

cnt_v <= cnt_v + 1'd1;

else

cnt_v <= cnt_v;

end

//vsync:场同步信号

assign vsync = (cnt_v <= V_SYNC - 1'd1) ? 1'b1 : 1'b0 ;

//图像有效信号

assign rgb_valid = (((cnt_h >= H_SYNC + H_BACK + H_LEFT)

&& (cnt_h < H_SYNC + H_BACK + H_LEFT + H_VALID))

&&((cnt_v >= V_SYNC + V_BACK + V_TOP)

&& (cnt_v < V_SYNC + V_BACK + V_TOP + V_VALID)))

? 1'b1 : 1'b0;

assign pix_data_req = (((cnt_h >= H_SYNC + H_BACK + H_LEFT - 1'b1)

&& (cnt_h < H_SYNC + H_BACK + H_LEFT + H_VALID - 1'b1))

&&((cnt_v >= V_SYNC + V_BACK + V_TOP)

&& (cnt_v < V_SYNC + V_BACK + V_TOP + V_VALID)))

? 1'b1 : 1'b0;

//pix_x,pix_y:VGA有效显示区域像素点坐标

assign pix_x = (pix_data_req == 1'b1)

? (cnt_h - (H_SYNC + H_BACK + H_LEFT-1'b1)) : 10'h3ff;

assign pix_y = (pix_data_req == 1'b1)

? (cnt_v - (V_SYNC + V_BACK + V_TOP)) : 10'h3ff;

//rgb:输出像素点色彩信息

assign rgb = (rgb_valid == 1'b1) ? pix_data : 16'b0 ;

endmodule vga_pic:

`timescale 1ns/1ns

module vga_pic

(

input wire vga_clk , //输入工作时钟,频率25MHz

input wire sys_rst_n , //输入复位信号,低电平有效

input wire [9:0] pix_x , //输入VGA有效显示区域像素点X轴坐标

input wire [9:0] pix_y , //输入VGA有效显示区域像素点Y轴坐标

output reg [15:0] pix_data //输出像素点色彩信息

);

parameter H_VALID = 10'd640 , //行有效数据

V_VALID = 10'd480 ; //场有效数据

parameter RED = 16'hF800, //红色

ORANGE = 16'hFC00, //橙色

YELLOW = 16'hFFE0, //黄色

GREEN = 16'h07E0, //绿色

CYAN = 16'h07FF, //青色

BLUE = 16'h001F, //蓝色

PURPPLE = 16'hF81F, //紫色

BLACK = 16'h0000, //黑色

WHITE = 16'hFFFF, //白色

GRAY = 16'hD69A; //灰色

always@(posedge vga_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

pix_data <= 16'd0;

else if((pix_x >= 0) && (pix_x < (H_VALID/10)*1))

pix_data <= RED;

else if((pix_x >= (H_VALID/10)*1) && (pix_x < (H_VALID/10)*2))

pix_data <= ORANGE;

else if((pix_x >= (H_VALID/10)*2) && (pix_x < (H_VALID/10)*3))

pix_data <= YELLOW;

else if((pix_x >= (H_VALID/10)*3) && (pix_x < (H_VALID/10)*4))

pix_data <= GREEN;

else if((pix_x >= (H_VALID/10)*4) && (pix_x < (H_VALID/10)*5))

pix_data <= CYAN;

else if((pix_x >= (H_VALID/10)*5) && (pix_x < (H_VALID/10)*6))

pix_data <= BLUE;

else if((pix_x >= (H_VALID/10)*6) && (pix_x < (H_VALID/10)*7))

pix_data <= PURPPLE;

else if((pix_x >= (H_VALID/10)*7) && (pix_x < (H_VALID/10)*8))

pix_data <= BLACK;

else if((pix_x >= (H_VALID/10)*8) && (pix_x < (H_VALID/10)*9))

pix_data <= WHITE;

else if((pix_x >= (H_VALID/10)*9) && (pix_x < H_VALID))

pix_data <= GRAY;

else

pix_data <= BLACK;

endmodulevga_colorbar:

`timescale 1ns/1ns

module vga_colorbar

(

input wire sys_clk ,

input wire sys_rst_n ,

output wire hsync ,

output wire vsync ,

output wire [15:0] rgb

);

wire vga_clk ;

wire locked ;

wire rst_n ;

wire [9:0] pix_x ;

wire [9:0] pix_y ;

wire [15:0] pix_data;

assign rst_n = (sys_rst_n & locked);

clk_gen clk_gen_inst

(

.areset (~sys_rst_n ),

.inclk0 (sys_clk ),

.c0 (vga_clk ),

.locked (locked )

);

vga_ctrl vga_ctrl_inst

(

.vga_clk (vga_clk ),

.sys_rst_n (rst_n ),

.pix_data (pix_data ),

.pix_x (pix_x ),

.pix_y (pix_y ),

.hsync (hsync ),

.vsync (vsync ),

.rgb (rgb )

);

vga_pic vga_pic_inst

(

.vga_clk (vga_clk ),

.sys_rst_n (rst_n ),

.pix_x (pix_x ),

.pix_y (pix_y ),

.pix_data (pix_data )

);

endmodule

4、实验结果

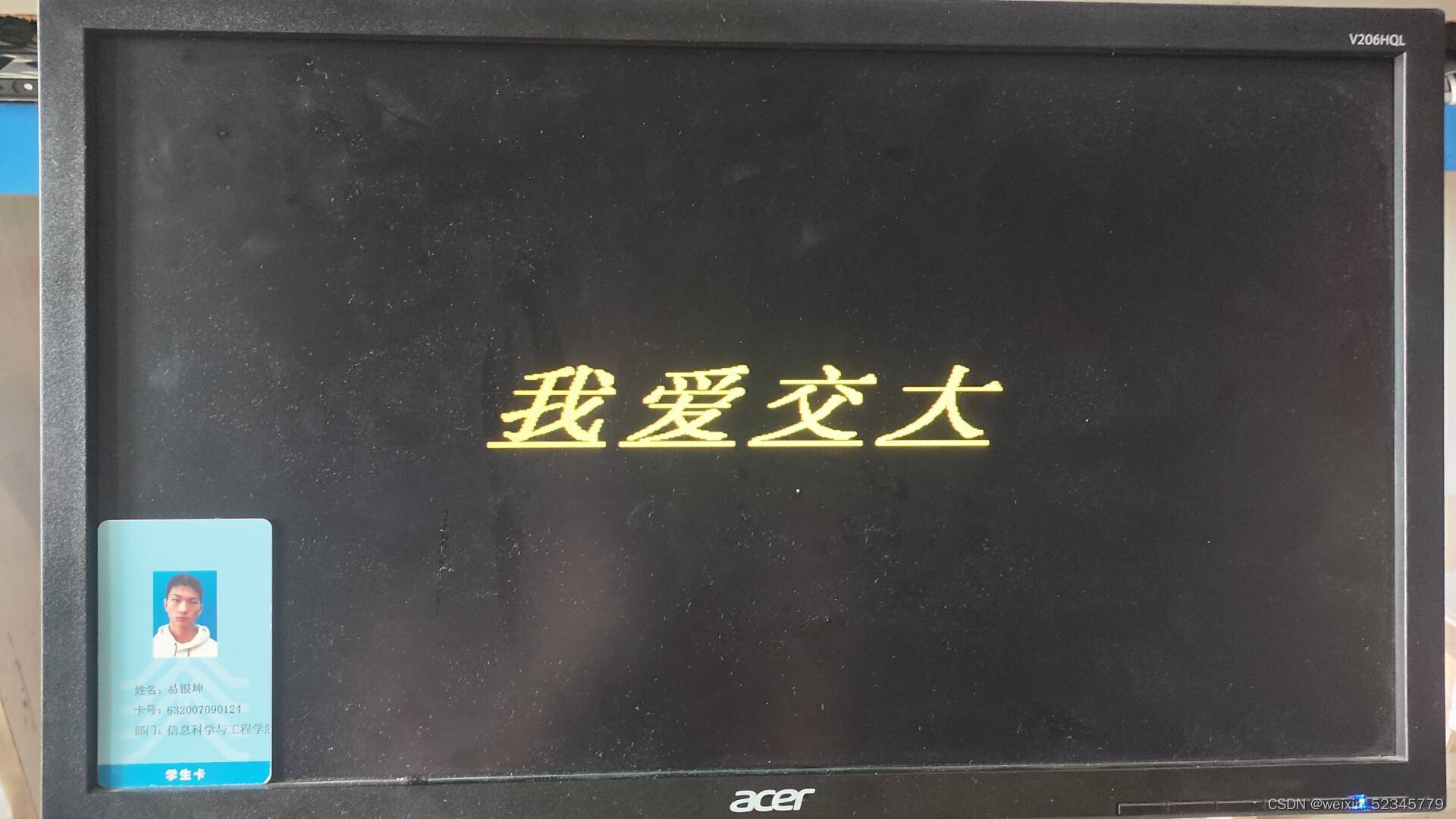

实战演练二:显示自定义字符:我爱交大

1、实验目标:

在vga显示屏上,显示点阵大小64x64,字宽x字高=56x56,显示模式640x480@60,背景为黑色的野火科技四个字符,如下:

2、各模块框图及其波箱图

顶层模块:

时钟分频模块:

vga控制模块:

图像信息生成模块:

图像信息生成模块波形图:

Vga_clk:经过时钟分频模块分频后的时钟 sys_rst_n:系统复位信号 Pix_x:由vga_ctrl产生的有效图像横坐标 Pix_y:由vga_ctrl产生的有效图像纵坐标 char_x:字符区域横坐标 char_y:字符区域纵坐标 Pix_data[15:0]:图像信息

3、模块代码:

顶层模块vga_char:

`timescale 1ns/1ns

module vga_char

(

input wire sys_clk ,

input wire sys_rst_n ,

output wire hsync ,

output wire vsync ,

output wire [15:0] rgb

);

wire vga_clk ;

wire locked ;

wire rst_n ;

wire [9:0] pix_x ;

wire [9:0] pix_y ;

wire [15:0] pix_data;

assign rst_n = (sys_rst_n & locked);

clk_gen clk_gen_inst

(

.areset (~sys_rst_n ),

.inclk0 (sys_clk ),

.c0 (vga_clk ),

.locked (locked )

);

vga_ctrl vga_ctrl_inst

(

.vga_clk (vga_clk ),

.sys_rst_n (rst_n ),

.pix_data (pix_data ),

.pix_x (pix_x ),

.pix_y (pix_y ),

.hsync (hsync ),

.vsync (vsync ),

.rgb (rgb )

);

vga_pic vga_pic_inst

(

.vga_clk (vga_clk ),

.sys_rst_n (rst_n ),

.pix_x (pix_x ),

.pix_y (pix_y ),

.pix_data (pix_data )

);

endmodule

时钟分频模块:clk_gen,调用pll锁相环

vga控制模块:

`timescale 1ns/1ns

module vga_ctrl

(

input wire vga_clk ,

input wire sys_rst_n ,

input wire [15:0] pix_data ,

output wire [9:0] pix_x ,

output wire [9:0] pix_y ,

output wire hsync ,

output wire vsync ,

output wire [15:0] rgb

);

parameter H_SYNC = 10'd96 , //行同步

H_BACK = 10'd40 , //行时序后沿

H_LEFT = 10'd8 , //行时序左边框

H_VALID = 10'd640 , //行有效数据

H_RIGHT = 10'd8 , //行时序右边框

H_FRONT = 10'd8 , //行时序前沿

H_TOTAL = 10'd800 ; //行扫描周期

parameter V_SYNC = 10'd2 , //场同步

V_BACK = 10'd25 , //场时序后沿

V_TOP = 10'd8 , //场时序上边框

V_VALID = 10'd480 , //场有效数据

V_BOTTOM = 10'd8 , //场时序下边框

V_FRONT = 10'd2 , //场时序前沿

V_TOTAL = 10'd525 ; //场扫描周期

//wire define

wire rgb_valid ; //VGA有效显示区域

wire pix_data_req ; //像素点色彩信息请求信号

//reg define

reg [9:0] cnt_h ; //行同步信号计数器

reg [9:0] cnt_v ; //场同步信号计数器

//cnt_h:行同步信号计数器

always@(posedge vga_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_h <= 10'd0 ;

else if(cnt_h == H_TOTAL - 1'b1)

cnt_h <= 10'd0 ;

else

cnt_h <= cnt_h + 1'd1 ;

//hsync:行同步信号

assign hsync = (cnt_h <= H_SYNC - 1'd1) ? 1'b1 : 1'b0 ;

//cnt_v:场同步信号计数器

always@(posedge vga_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_v <= 10'd0 ;

else if((cnt_v == V_TOTAL - 1'd1) && (cnt_h == H_TOTAL-1'd1))

cnt_v <= 10'd0 ;

else if(cnt_h == H_TOTAL - 1'd1)

cnt_v <= cnt_v + 1'd1 ;

else

cnt_v <= cnt_v ;

//vsync:场同步信号

assign vsync = (cnt_v <= V_SYNC - 1'd1) ? 1'b1 : 1'b0 ;

//rgb_valid:VGA有效显示区域

assign rgb_valid = (((cnt_h >= H_SYNC + H_BACK + H_LEFT)

&& (cnt_h < H_SYNC + H_BACK + H_LEFT + H_VALID))

&&((cnt_v >= V_SYNC + V_BACK + V_TOP)

&& (cnt_v < V_SYNC + V_BACK + V_TOP + V_VALID)))

? 1'b1 : 1'b0;

//pix_data_req:像素点色彩信息请求信号,超前rgb_valid信号一个时钟周期

assign pix_data_req = (((cnt_h >= H_SYNC + H_BACK + H_LEFT - 1'b1)

&& (cnt_h < H_SYNC + H_BACK + H_LEFT + H_VALID - 1'b1))

&&((cnt_v >= V_SYNC + V_BACK + V_TOP)

&& (cnt_v < V_SYNC + V_BACK + V_TOP + V_VALID)))

? 1'b1 : 1'b0;

//pix_x,pix_y:VGA有效显示区域像素点坐标

assign pix_x = (pix_data_req == 1'b1)

? (cnt_h - (H_SYNC + H_BACK + H_LEFT - 1'b1)) : 10'h3ff;

assign pix_y = (pix_data_req == 1'b1)

? (cnt_v - (V_SYNC + V_BACK + V_TOP)) : 10'h3ff;

//rgb:输出像素点色彩信息

assign rgb = (rgb_valid == 1'b1) ? pix_data : 16'b0 ;

endmodule

图像信息生成模块:

module vga_pic (

input wire vga_clk,

input wire sys_rst_n,

input wire [9:0] pix_x,

input wire [9:0] pix_y,

output reg [15:0] pix_data

);

parameter CHAR_B_H = 10'd192 ,//字符开始X轴坐标

CHAR_B_V = 10'd208 ;//字符开始Y轴坐标

parameter CHAR_W = 10'd256,//字符宽度

CHAR_H = 10'd64 ;//字符高度

parameter BLACK = 16'h0000,

GOLDEN = 16'hFEC0;

reg [CHAR_W-1:0] char [CHAR_H -1:0]; //存储器变量,位宽256,深度64,表示char有64个存储单元,每个单元能存储的位宽是256

wire [9:0] char_x;

wire [9:0] char_y;

assign char_x = (((pix_x >= CHAR_B_H) && (pix_x < CHAR_B_H + CHAR_W))

&& ((pix_y >= CHAR_B_V) && (pix_y < CHAR_B_V + CHAR_H)))

? (pix_x - CHAR_B_H) : 10'h3ff;

assign char_y = (((pix_x >= CHAR_B_H) && (pix_x < CHAR_B_H + CHAR_W))

&& ((pix_y >= CHAR_B_V) && (pix_y < CHAR_B_V + CHAR_H)))

? (pix_y - CHAR_B_V) : 10'h3ff;

always@(posedge vga_clk)

begin

char[0]<=256'h0000000000000000000000000000000000000000000000000000000000000000;

char[1]<=256'h0000000000000000000000000000000000000000000000000000000000000000;

char[2]<=256'h0000000000070000000000000000001E0000000003C000000000000000E00000;

char[3]<=256'h00000000038F800000000000000000FE0000000003E000000000000000F80000;

char[4]<=256'h000000000FCFE0000000000000001FFF0000000003F000000000000000FE0000;

char[5]<=256'h000000003FCFEF00000000000007FFFF0000000001F800000000000001FE0000;

char[6]<=256'h00000001FFDFCF800000000007FFFFFF0000000001FC00000000000001F80000;

char[7]<=256'h0000001FFFDF87E0000001FFFFFFFFC00000000001FC00000000000001F00000;

char[8]<=256'h000003FFFE1F07F0000001FFFFC003E00000000000FC000E0000000003F00000;

char[9]<=256'h00003FFFC01F03F80000001C03C007F00000000000F8001E0000000003F00000;

char[10]<=256'h00003F0F803F03F80000001E03E00FF00000000000F8007F0000000003E00000;

char[11]<=256'h0000000F803E03F80000001F01F01FC00000000000F000FF0000000007E00000;

char[12]<=256'h0000001F803E01F80000001F81F83F800000FFFFFFFFFFFF0000000007E00000;

char[13]<=256'h0000001F007E01F80000001F81F83E000000FFFFFFFFFFFF0000000007C0001C;

char[14]<=256'h0000001F007C01F00000000F81F87C000000000000000000000000000FC0003C;

char[15]<=256'h0000003F007C00E00000000F81F0F80000000007800E0000000000000FC000FE;

char[16]<=256'h0000003E00FC007000001C0F81F1F0000000000FC00F8000000000000F8001FE;

char[17]<=256'h0000003E00F801F800001C0F01E3C0780000003FC007E0000003FFFFFFFFFFFF;

char[18]<=256'h0000007E00F803FC00003C0E000381FC0000007FC003F8000003FFFFFFFFFFFF;

char[19]<=256'h0007FFFFFFFFFFFC00007FFFFFFFFFFC000000FF0001FC00000000001F000000;

char[20]<=256'h0007FFFFFFFFFFFC0000FFFFFFFFFFFC000001FC0000FF00000000003F000000;

char[21]<=256'h000000FC01F000000000F801C00003F8000007F800007F80000000003F000000;

char[22]<=256'h000000F801F000000003F003F00007E000000FF8003C7F80000000007F000000;

char[23]<=256'h000000F803F01E000007F003F0000F8000003FB8003F3F80000000007F000000;

char[24]<=256'h000001F803E03E00000FE007F0001F0000007F38007F9F8000000000FF000000;

char[25]<=256'h000001F003E07F00000FE007E0003E000001FC3800FF9F8000000000FF000000;

char[26]<=256'h000001F003E0FF00000F8007C00078000003F03800FE0F8000000001FF000000;

char[27]<=256'h000003F07BE1FE000000000FC001FC00000FC03C01FC0F0000000001FF000000;

char[28]<=256'h000003E3FFC3F8000001FFFFFFFFFE00003F003C03F8000000000003FF000000;

char[29]<=256'h000003FFE7C7F0000001FFFFFFFFFE00003C003C03F0000000000007EF000000;

char[30]<=256'h000007FF07CFE0000000003F000000000000003C07E0000000000007EF800000;

char[31]<=256'h00001FF807DFC0000000003E000700000000003C0FC000000000000FCF800000;

char[32]<=256'h0001FFE007FF80000000007E001F80000000003E1F8000000000001F87800000;

char[33]<=256'h001FFFC00FFF0000000000FFFFFFC0000000003E3F8000000000001F87800000;

char[34]<=256'h01FFFF800FFE0000000000FFFFFFC0000000001E7F0000000000003F07C00000;

char[35]<=256'h01FFFF800FF80000000001FE007F80000000001FFE0000000000007E07C00000;

char[36]<=256'h01FF1F000FF00000000003FE00FE00000000001FFC000000000000FC07C00000;

char[37]<=256'h00FC1F000FE00000000007FF01FC00000000001FF8000000000001F803E00000;

char[38]<=256'h00F03F001FC0070000000FDF03F800000000001FE0000000000003F803E00000;

char[39]<=256'h00003E007FC00F0000001F8F8FF000000000000FC0000000000007F003F00000;

char[40]<=256'h00003E00FFE00E0000003F0F9FC000000000003FC000000000000FE001F80000;

char[41]<=256'h00007E03FFE01E0000007E07FF8000000000007FE000000000001FC001FC0000;

char[42]<=256'h00007C0FF7F01E000001F807FF000000000001FFF000000000007F0001FE0000;

char[43]<=256'h00007C3FC3F83C000003F003FC000000000007FBFC0000000000FE0000FF0000;

char[44]<=256'h0000FC7F03F83C000007E007FC00000000001FE1FF0000000001FC0000FF8000;

char[45]<=256'h0000F9FC01FE7C00001F801FFF00000000007F80FFC000000007F000007FE000;

char[46]<=256'h00E1FFF001FF7800003F007FFFF000000001FE007FFC0000001FE000003FFC00;

char[47]<=256'h00FFFF8000FFF80000FC01FF7FFFE0000007F8003FFFFC00003F8000001FFC00;

char[48]<=256'h00FFFC00007FF80001F80FFC1FFFF800003FE0001FFFFC0000FE0000001FFC00;

char[49]<=256'h003FF000003FF80007E07FE007FFF80001FF000007FFF80007F80000000FE000;

char[50]<=256'h001FE000001FF8000F87FF0000FFE0000FF8000000FFE0001FC0000000078000;

char[51]<=256'h000F80000003F8000E3FF000001FC0003FC00000001FC0007F00000000000000;

char[52]<=256'h000E000000007800003E0000000000003C000000000000007800000000000000;

char[53]<=256'hFFFFFFFFFFFFFF80FFFFFFFFFFFFFF80FFFFFFFFFFFFFF80FFFFFFFFFFFFFF80;

char[54]<=256'hFFFFFFFFFFFFFF80FFFFFFFFFFFFFF80FFFFFFFFFFFFFF80FFFFFFFFFFFFFF80;

char[55]<=256'hFFFFFFFFFFFFFF80FFFFFFFFFFFFFF80FFFFFFFFFFFFFF80FFFFFFFFFFFFFF80;

char[56]<=256'h0000000000000000000000000000000000000000000000000000000000000000;

char[57]<=256'h0000000000000000000000000000000000000000000000000000000000000000;

char[58]<=256'h0000000000000000000000000000000000000000000000000000000000000000;

char[59]<=256'h0000000000000000000000000000000000000000000000000000000000000000;

char[60]<=256'h0000000000000000000000000000000000000000000000000000000000000000;

char[61]<=256'h0000000000000000000000000000000000000000000000000000000000000000;

char[62]<=256'h0000000000000000000000000000000000000000000000000000000000000000;

char[63]<=256'h0000000000000000000000000000000000000000000000000000000000000000;

end

always@(posedge vga_clk or negedge sys_rst_n)begin

if(sys_rst_n == 1'b0)

pix_data <= BLACK;

else if((((pix_x >= CHAR_B_H-1'b1) && (pix_x <= CHAR_B_H + CHAR_W-1'b1))

&& ((pix_y >= CHAR_B_V) && (pix_y <= CHAR_B_V + CHAR_H)))

&& (char[char_y][10'd255- char_x] == 1'b1))

pix_data <= GOLDEN;

else

pix_data <= BLACK;

end

endmodule4、实验结果