高速电路设计的情况

- 高速的时钟频率

- 快速的上升沿和下降沿的切换时间将导致信号的反射和串扰问题

传输线模型

O-R-L-R-L-R-L-R-L-O

| | | |

C C C C

| | | |

P P P P

O=传输线终端

R=单位长度阻抗

P=平板

L=单位长度电感

L与结构无关,大约为每英寸3.5nH

X C = 1 2 π f C X_C=\frac{1}{2\pi f C} XC=2πfC1

X L = 2 π f L X_L=2\pi f L XL=2πfL

高频电路的特征阻抗:

Z 0 = L 0 C 0 Z_0=\sqrt{\frac{L_0}{C_0}} Z0=C0L0

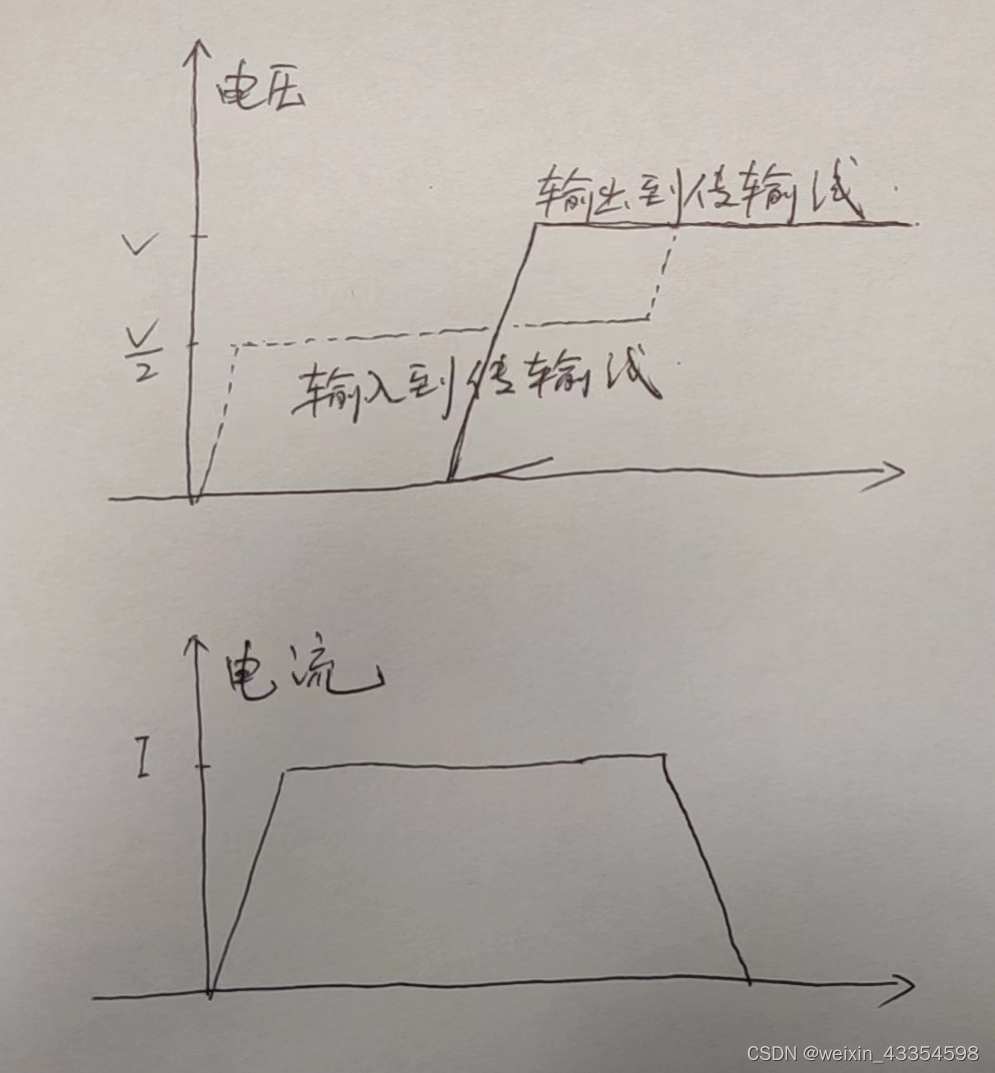

当信号从0变到1时,传输线的电压和电流波形

信号首先会对寄生电容进行充电,并且只达到一半的电压,到达另一端的开路后会产生反射,继续充电得到稳定的电压值,此时电路降为0。

反射问题和边缘长度

1ns信号切换的边缘长度是:

1E-9*C/4≈7.6cm(光速C=3E8)

1ps信号切换的边缘长度是:0.76cm

当传输线大于边缘长度时开始看到反射。此时应该使用可控的阻抗和端接方案来管理反射。

串扰问题

传输线等于边缘长度的1/2时,会出现串扰问题。

即1ns的信号,传输线在3.8cm以上是会出现串扰问题。

串扰在布线规则中进行管理。

影响信号的完整性SI的5个主要问题

- 反射的管理

- 串扰的管理

- 电源传输的稳定性

- 确保信号在合适的时候到达接收端

- 电磁干扰问题EMI

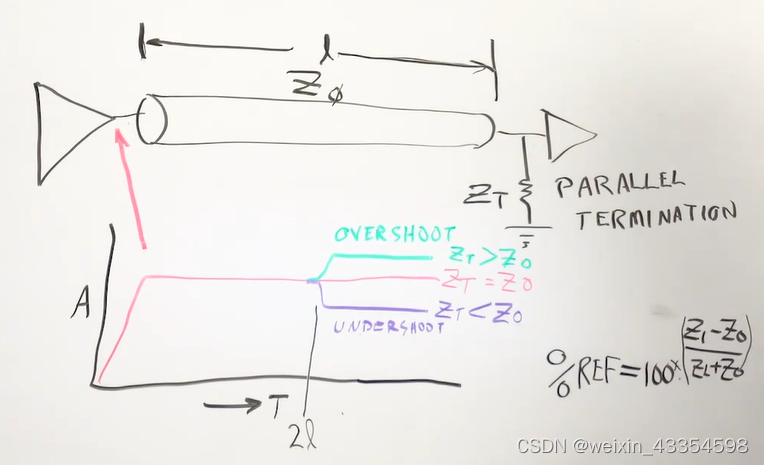

1. 反射

反射是因为传输路径阻抗的突变导致的。

通过仔细地堆叠stack up和端接来使反射最小化。

在传输线进行端接(end of tranmission line)可以有两种方式。

a. 在Driver Output串联termination

b. 在Receiver input并联termination

在实际使用中,由于并联termination会消耗大量的能量,因此使用的较少(DDR和差分对)。

我们可以通过堆叠来准备地计算出阻抗值

- 2D场求解器

- 板材的介电常数

当阻抗不匹配时的反射情况如下图。

2. 串扰

两个相邻的开关传输线能量的耦合。

同一层的串扰为电感性串扰。

相邻层的串扰为电容性串扰。

网络的串扰容限与逻辑family有关(TTL、LVTTL、COMS…)

我们需要SI分析工具来给出空间的规则,而不是采用2H、3H这样的经验值。

通过增加两条平行线之间的距离或者减小平行线和plane之间的距离来实现。

一个有效的布线的经验是5mil宽的布线,间隔5mil宽,5mil宽的布线,5mil高的plane层。

通过插入保护线段来消除串扰是不正确的,这往往会带来更多的串扰的风险。

使用差分对可以有效地解决串扰问题,重要的事情说3遍:使用差分对!使用差分对!使用差分对!

3. 电源的Distribute

电源纹波Ripple的定义为:随着负载电流的变化,Supply电压也出现变化。

事实证明最常见的电磁干扰源EMI的来源就是纹波的叠加。

叠层的设计

叠层Stackup:在PCB设计中的信号和电源层的排列。

单层电路板:低速信号,20纳秒的边缘速度(<50MHz)。

现代叠层的要求:

- 为所有的信号提供相同的阻抗,尽量将反射降到最低。

- 确保串扰的最小化。

- 提供多个供电电压。

- 为不同的供电提供层间的电容。

- 玻璃纤维会使高速差分对产生偏斜Slew。

电源旁路电容

在高速电路中,0.1uF,0.01uF的经验的旁路电容,往往并不能起到什么作用,反而是造成EMI的来源。

因此通过采用两个平面层之间的平面电容来代替分立电容,这是因为平面电容有比分立电容低2个数量级的电感。

通过控制叠层的厚度和介电常数,可以控制电容值。

玻璃纤维编织造成的问题

电路板铜皮之间为浸泡树脂的玻璃纤维的编织网。树脂的介电常数大约为3,玻璃纤维的介电常数大约为6,较高的介电常数意味着低的电阻,较低的介电常数意味着高的电阻。

所以传导线在玻璃纤维上传输时会看到阻抗的变化。

电磁场的速度公式:

1 μ ϵ \frac{1}{\sqrt{\mu \epsilon}} μϵ1

可见介电常数越大,电磁波的速度越小。

因此玻璃纤维上的速度要比中间空洞的树脂的速度要快。

这对于单端的信号通常不是什么问题。

但是对于差分信号,可能会造成两个信号到达接收端的时间的差异,这将导致skew。

我们可以通过控制玻璃纤维的成分(树脂的含量)来控制skew。