一、概述

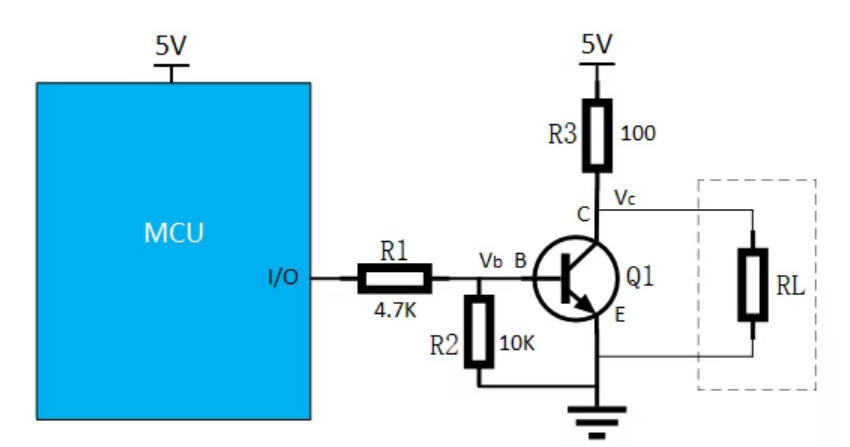

在嵌入式系统中,主芯片MCU的I/O口驱动电流通常比较小,如果外部负载需求的电流比较大时,比如背光LED、继电器、蜂鸣器等元件,常用到的一种电路是三极管的控制驱动电路。

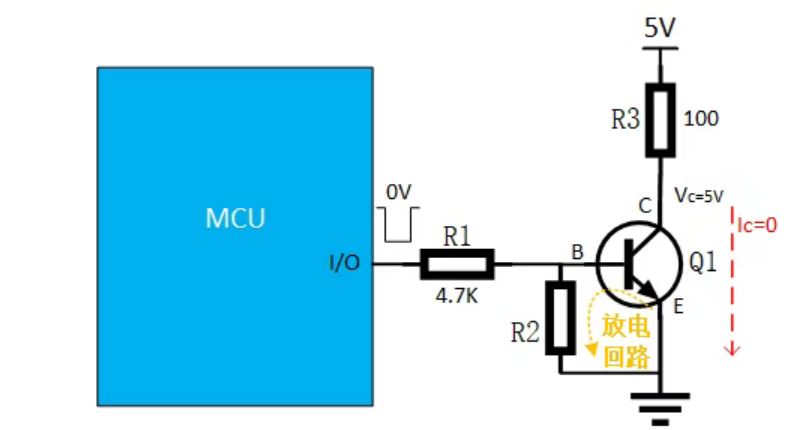

上图是1个典型的三极管控制驱动电路示例,主芯片通过I/O口来控制NPN三极管的通断,从而控制Vc输出电压的高低,Vc用于给外部负载RL提供驱动电压,其基本控制过程为:

I/O输出高时,Vb为高,三极管Q1导通,输出电压Vc为低,外部负载RL断电。

I/O输出低时,Vb为低,三极管Q1截止,输出电压Vc为高,外部负载RL通电。

这里面R1用于控制和调节基极B的输入电流;R3用于限制输出CE间的电流。

二、电路的基本原理

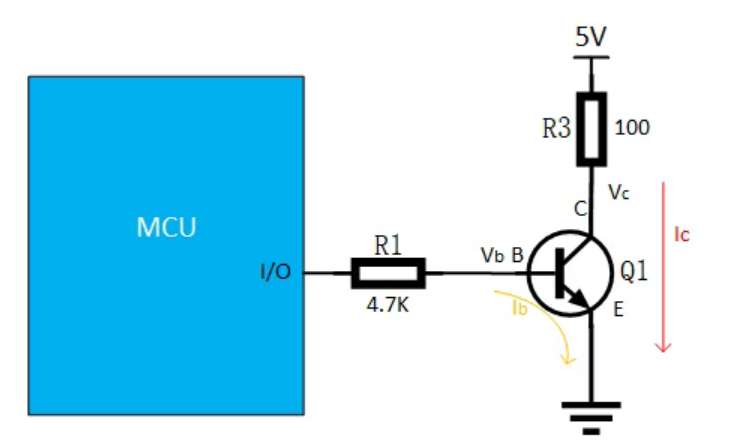

如果不使用电路中的R2,电路是否可以工作,下图为三极管Q1的输入端基极B没有下拉电阻R2时的电路。

根据上图所示,三极管Q1有三个工作状态,截止、放大和饱和。截止就是三极管不导通,处于断开状态;放大就是输出电流Ic与输入电流Ib成比例的变化,放大状态比较复杂,实际产品中很少使用图中的电路,需要放大功能时多使用集成的运放芯片,放大可以认为是部分导通;而饱和就是完全导通;我们这里只使用了截止断开和饱和导通两个状态。三极管的饱和导通条件主要包括电压和电流两个条件。对于NPN型三极管 ,导通条件如下:

电压条件:基极和发射极之间的电压Vbe需要大于导通电压,通常为0.6V至0.7V,这里按0.7计算。

电流条件:基极电流Ib要足够大,Ib > Ice/β,其中β是放大倍数,通常在90-120之间,我们这里按100估算(具体可以查阅详细datasheet获得相应的数据)。

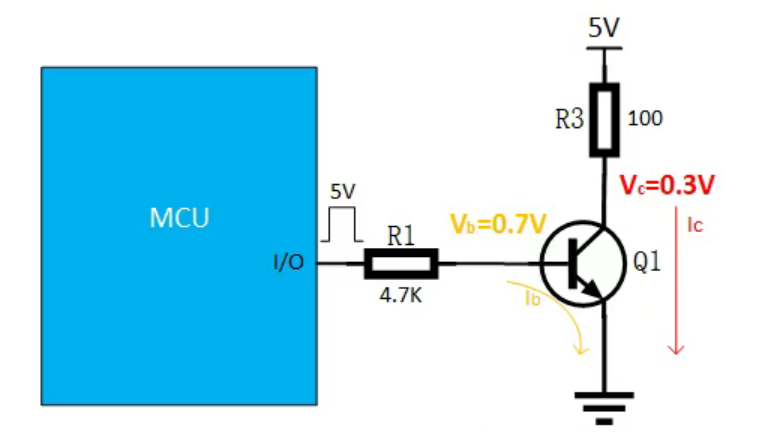

当I/O输出高电平(5V),三极管还未导通时,Vb=5V>0.7V,所以电压条件满足;

此时Ib=5/4.7k=1mA, βIb=100*1mA=100mA; 而Ic=5/100=50mA, Ice/β=50/100=0.5mA,Ib =1> 0.5mA,所以电流条件也满足。三极管可以正常的工作在截止与饱和导通之间,导通时,Vb=0.7V,Vc=0.3V。

从分析结果来看,不使用下拉电阻R2,三极管是可以工作的,而且在实际应用中,这个电路也确实可以使用。

既然这样,为什么很多电路还要使用下拉电阻呢?这样不是浪费吗?这个R2到底有什么用呢?

三、基极下拉电阻的作用

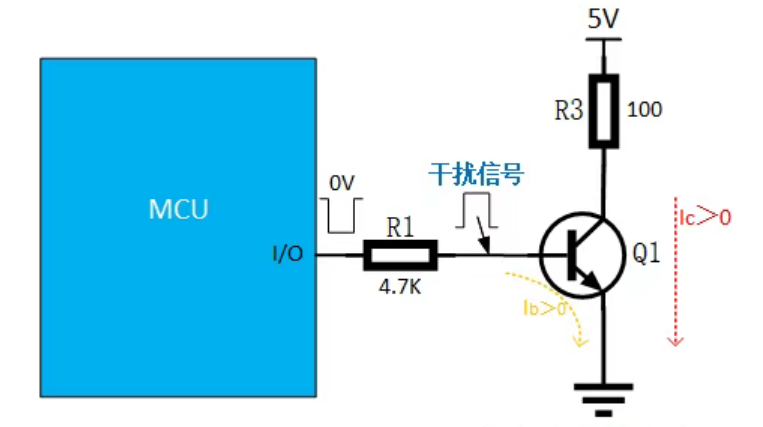

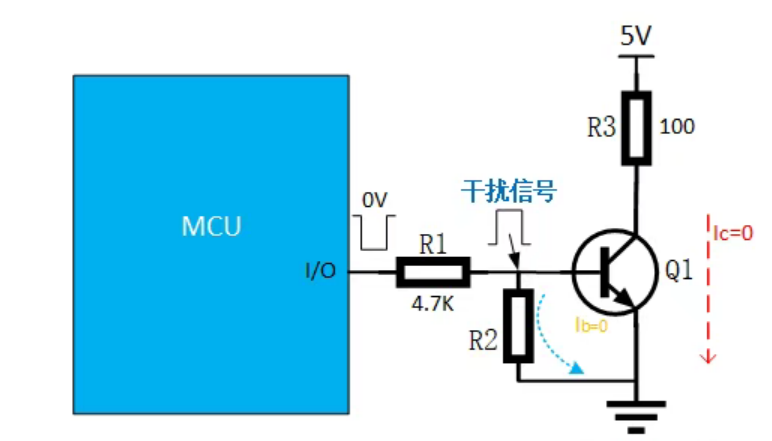

1. 抗输入干扰

在应用中,I/O口输出高电平(5V)时,要确保三极管导通;同样,在I/O口输出低电平(0V)时,要确保三极管截止。而实际电路中的电磁环境可能比较恶劣,电磁干扰也比较多,如果没有这个电阻,干扰信号可能会串入基极,导致三极管需要截止时而异常导通。干扰模型如下图所示。

而有了这个下拉电阻R2后,下拉电阻会在基极提供1个对地的路径,这样即使有干扰信号串入基极,这个干扰信号会被R2吸收,所以三极管还是保持截止。

2. 解决漏电流问题

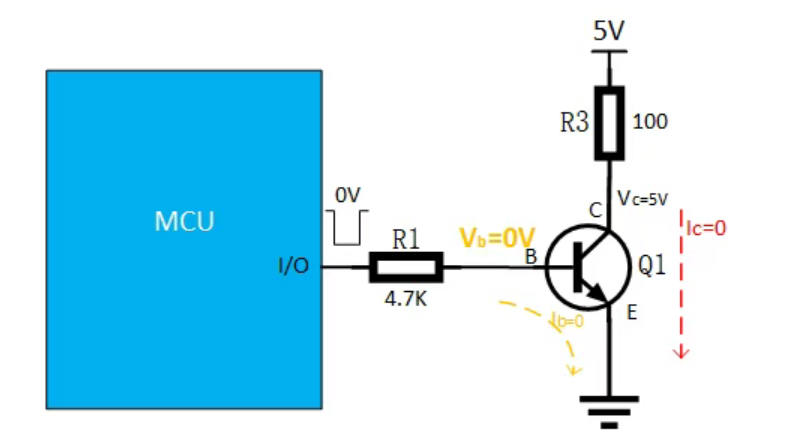

I/O口输出低电平(0V)时,Vb=0,三极管Q1处于截止不导通状态,此时Vc处相当于断路,Vc=5V,如下图所示。

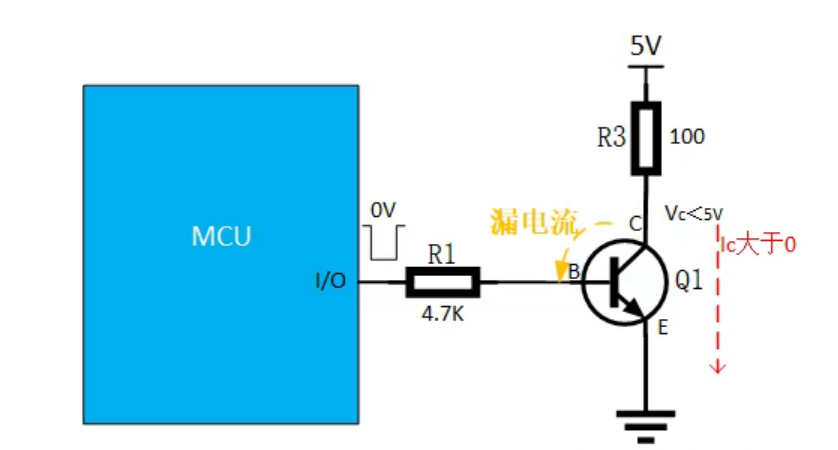

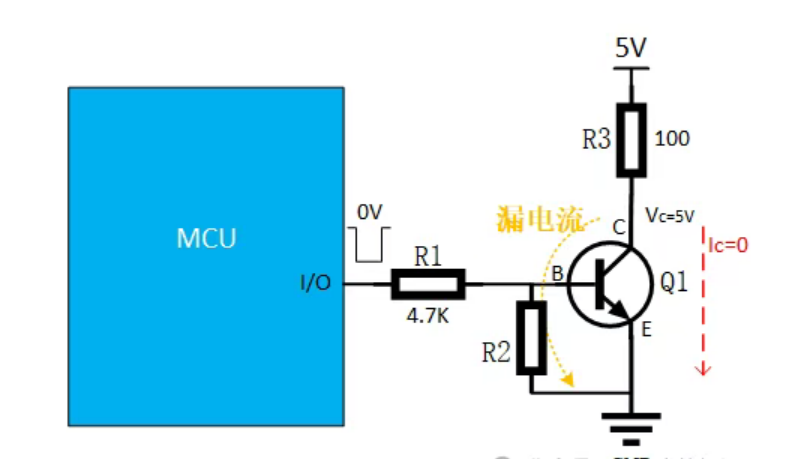

但是在实际电路中,由于三极管内部的PN结在制造过程中可能不完全隔离,导致在截止状态下仍有微小的电流流动,这时候会产生从集电极流入基极的漏电流,这个漏电流的大小会受多种因素的影响。比如材料纯度不够、杂质侵入、高温,高压、元器件老化等都会导致漏电流变大,漏电流达到一定程度时会把三极管带入到一个错误的导通状态,比如进入放大状态,也就是部分导通,如下图所示。

在那些对精度要求极高的电路中,微小的漏电流都可能导致结果出现很大的偏差,进而影响整体结果的准确性。而基级有了这个下拉电阻R2。漏电流就可以经过这个电阻到地,这样三极管还是可靠截止的。

3. 加速关断过程

I/O输出由高到低时,三极管会由饱和导通变为截止状态,也就是关断状态。一些高频或高速电路会要求快速响应,也就是三极管要立即关断。 但是三极管的基极B和发射极E极之间是存在内部电容的,当I/O口输出低电平(0V)时,由于电容的特性是电压不能突变,这就导致Vb不是立即为0,而是逐渐变化的,使三极管截止的过程变慢。而有了这个下拉电阻R2,就与BE之间形成了1个放电的回路,当三极管退出饱和区的时候,基极存储的电荷可以快速的释放掉,从而加快三极管的截止速度,使输出的脉冲上升沿更陡峭,使电路响应更快,具体放电回路如下图所示。

四、总结

三极管基极输入控制端下拉电阻的主要作用是抗输入干扰、解决漏电流问题和加速关断过程,它们在平时正常工作时作用不明显,但是在EMC环境较差、输出精度要求较高和高频电路应用时会发挥重要作用。