一、SPI 总线概念

SPI 总线 --- Serial Peripheral Interface,即串行外设接口

- SPI 是摩托罗拉公司设计的一款 串行、同步、全双工总线;

- SPI 总线是三线 / 四线制总线,分别是:SPI_SCK(时钟线)、SPI_MOSI(串行发送线)、SPI_MISO(串行接收线)、SPI_NSS / CSS(片选线 );

- SPI 总线通信速率一般 达到 Mbps;

- SPI 总线应用场景:数码管(中控屏)、LCD 屏……

- SPI 总线支持主从机模式,支持多主机多从机,一般使用单主机多从机。

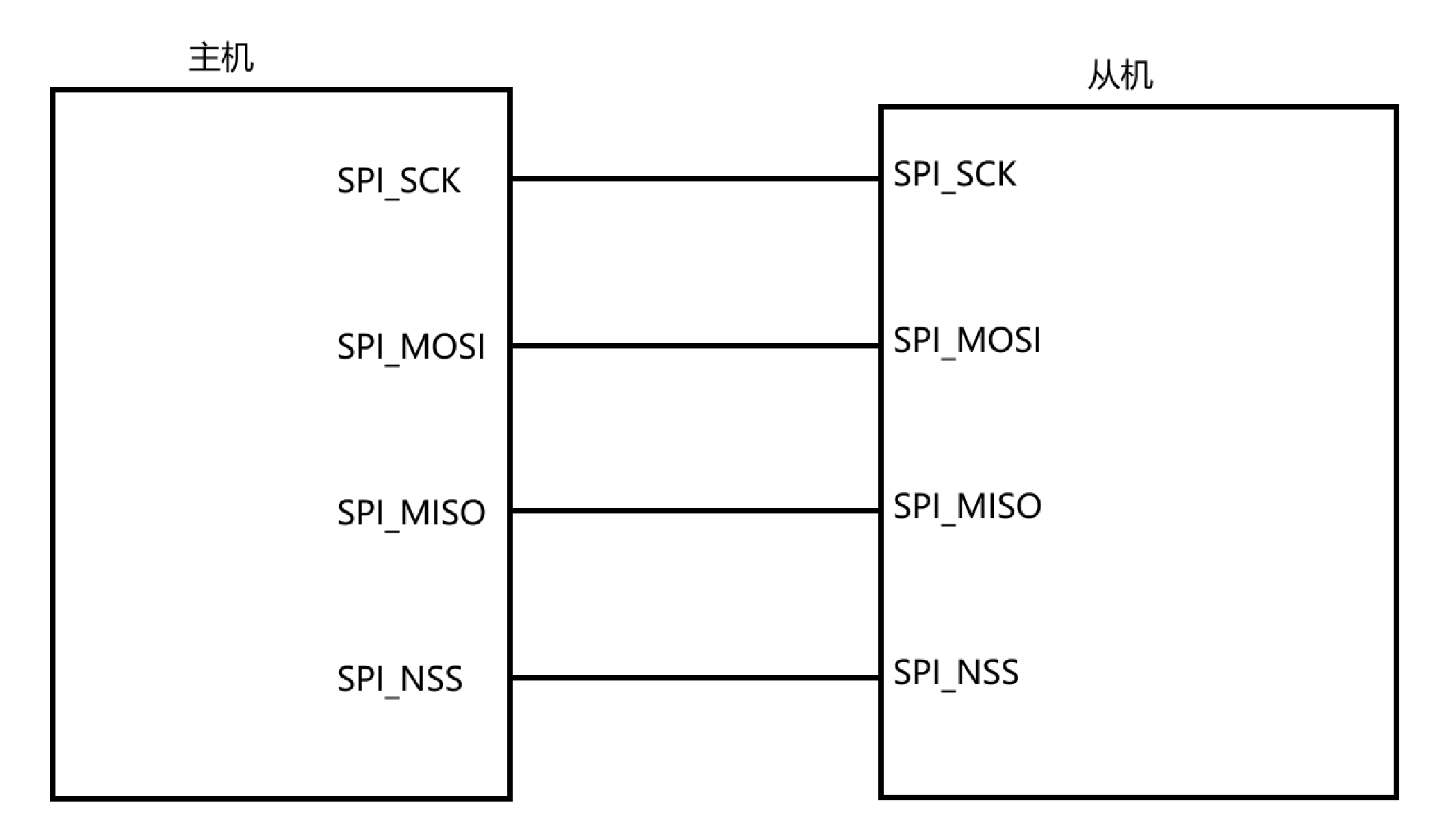

二、SPI 总线硬件连接

SPI 总线为三线制 / 四线制:

- SPI_SCK:时钟线 - 对使用 SPI 总线通信的两个设备进行时钟同步;

- SPI_MOSI:串行发送线 - 主机输出,从机输入;

- SPI_MISO:串行接收线 - 主机输入,从机输出

- SPI_NSS / NCS:片选线 - CS:Chip Select(芯片选择),N(多根、多个)。

SPI 总线支持主从机模式(Master / Slaver)

M:Master O:Output S:Slaver I:Input

当使用 SPI 总线通信时,存在多个从机设备,主机如何找到要通信的从机?

SPI 总线通过 SPI_NSS/NCS 片选线进行从机选择;

每一个挂载在 SPI 总线的从机设备,都有一根自己私有的 NSS/NCS 片选线和主机相连;

SPI 总线上的主机将需要通信的从机的 NSS/NCS 片选线电平信号拉低,就代表要和对应的主机进行通信。

2.1 四线制连接方式 - 多从机

四线制时,每个从机的 SPI_NSS/NCS 片选线都和主机单独相连。

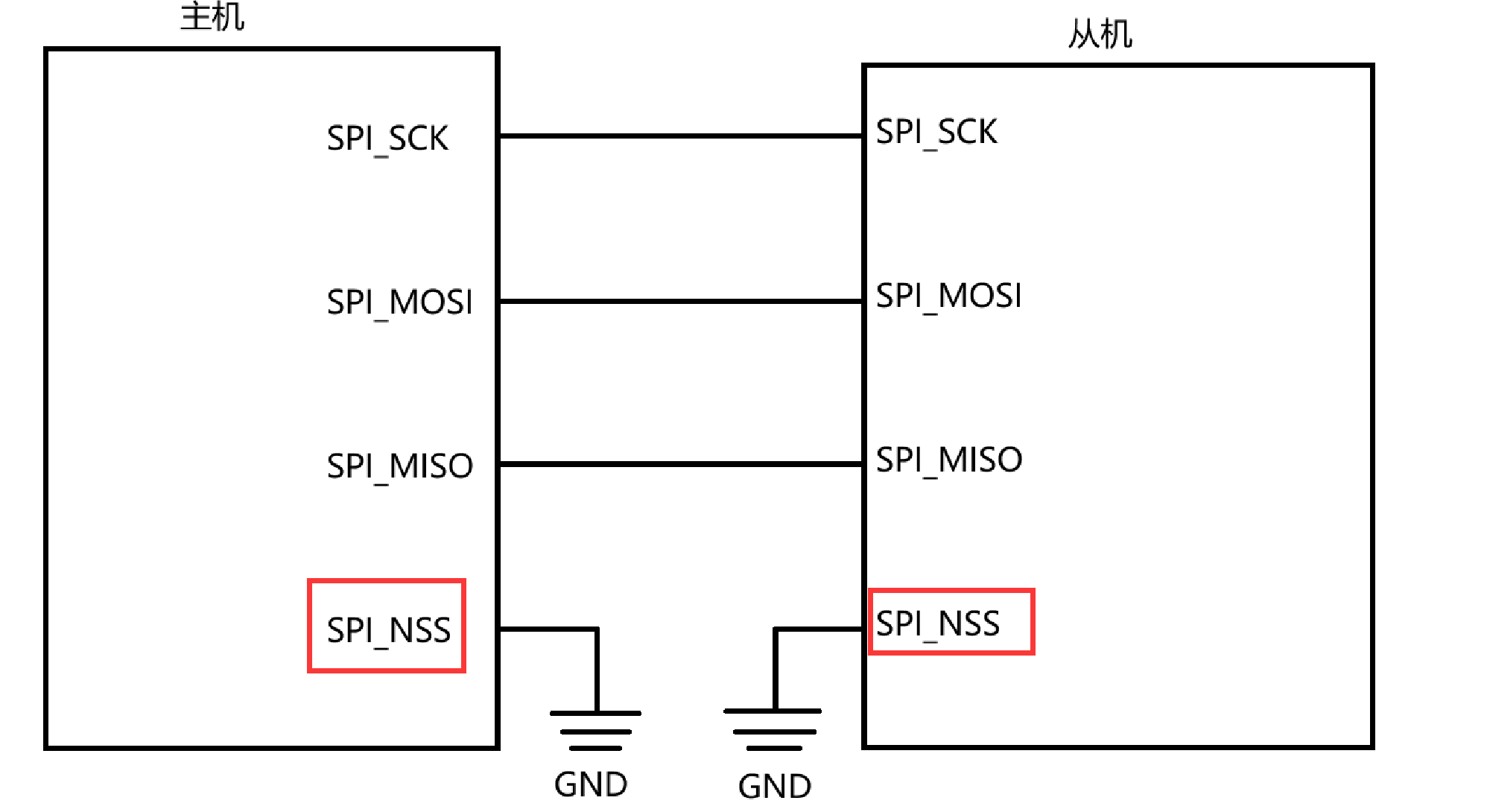

2.2 三线制连接方式 - 单从机

单从机时,主机和从机的 SPI_NSS/NCS 片选线可以直接接 GND,这样片选线上的电平一直为低电平,这样主机和从机都知道对方可以通信,直接进行数据收发。

三、SPI 总线时序图

起时信号:NSS / NCS 片选线上的电平信号从 高电平 -> 低电平 信号,产生一个下降沿信号时,代表主机要和对应从机通信,也代表一次 SPI 总线通信的开始。

终止信号:NSS / NCS 片选线上的电平信号从 低电平 -> 高电平 信号,产生一个上升沿信号时,代表主机要和对应从机断开连接,也代表一次 SPI 总线通信的结束。

数据发送信号(触发信号):SCK 时钟线处于上升沿变化期间,MOSI 数据线上主机可以发送数据,MISO 数据线上从机也可以发送数据;

数据读取信号(采样信号):SCK 时钟线处于下降沿变化期间,MOSI 数据线上主机可以接收数据,MISO 数据线上从机也可以接收数据。

SPI 总线通信的最小数据单位是字节,一般为 8 位(1 字节)或者 16 位(2 字节)。

NSS / NCS 片选线为低电平状态时,SPI 总线处于占用状态,数据线上有实际数据传输;

NSS / NCS 片选线为高电平状态时,SPI 总线处于空闲状态,数据线上无实际数据传输。

3.1 SPI 总线的全双工通信

- 场景:主机发送 0xFF,从机发送 0x00

- 时钟周期操作:

- 上升沿期间:主机通过 MOSI 数据线发送 0xFF 中的 1 位数据,同时从机通过 MISO 数据线发送 0x00 中的 1 位数据。

- 下降沿期间:从机通过 MOSI 数据线接收 0xFF 中的 1 位数据,同时主机通过 MISO 数据线接收 0x00 中的 1 位数据。

- 8 个时钟周期后:

- 主机:通过 MOSI 发送完毕 0xFF,同时通过 MISO 接收完毕 0x00。

- 从机:通过 MISO 发送完毕 0x00,同时通过 MOSI 接收完毕 0xFF。

与 IIC 总线的对比(8 个时钟周期):

- IIC 总线:主机可发送完毕 0xFF 数据,从机可接收完毕 0xFF 数据。

- SPI 总线:主机可发送完毕 0xFF 且接收完毕 0x00;从机可发送完毕 0x00 且接收完毕 0xFF。

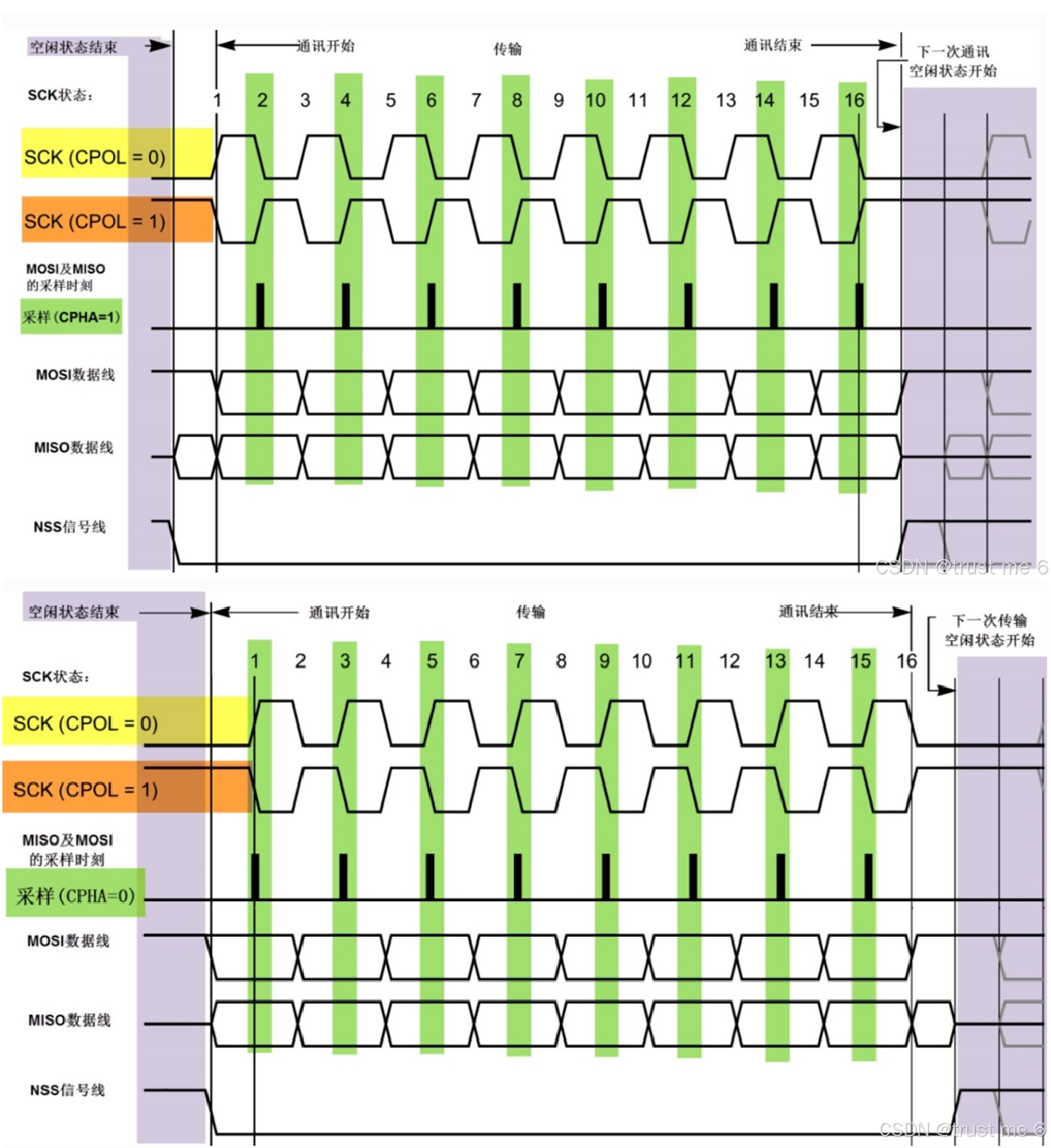

三、SPI 总线的工作模式 - 协议格式

SPI 总线的工作模式(协议格式)和 SPI 总线的 时钟极性 CPOL 、时钟相位 CPHA 相关。

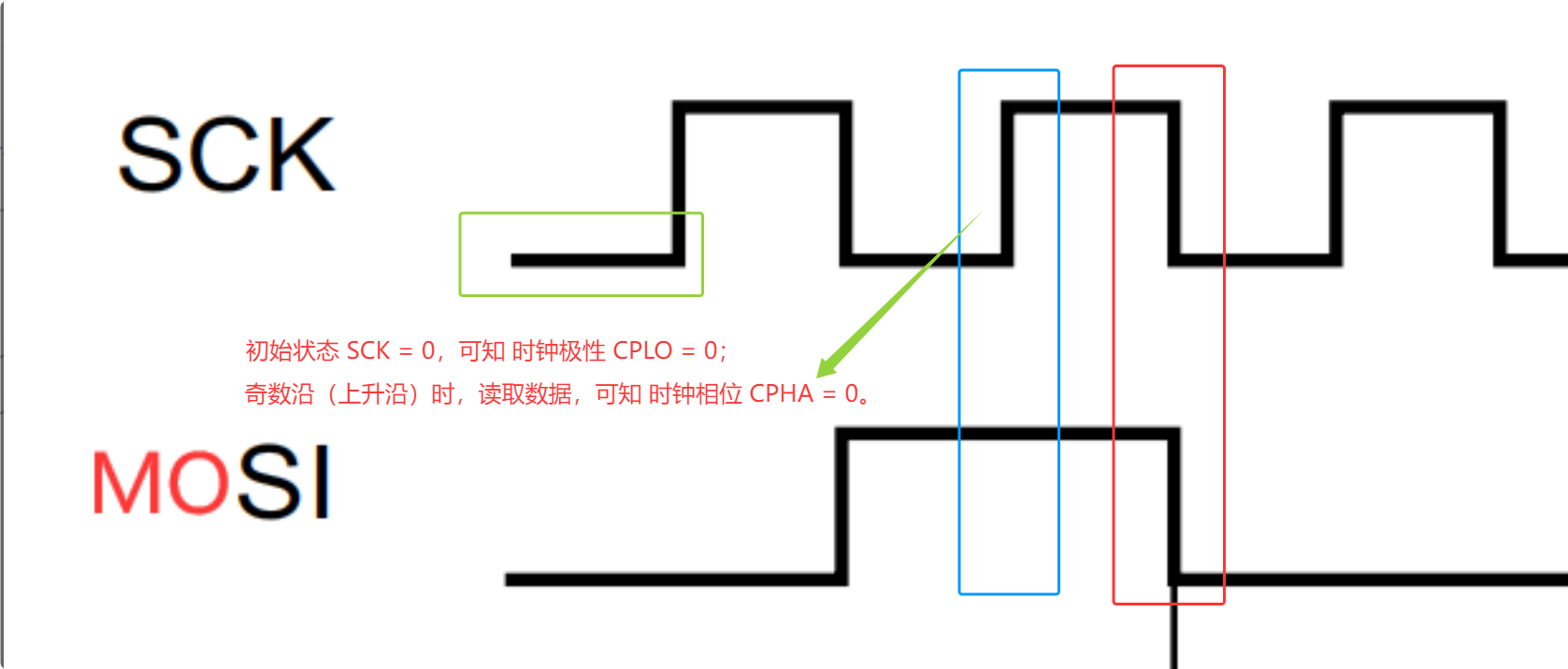

时钟极性(CPOL):时钟线初始状态的电平信号;

CPOL = 0:SCK 时钟线初始电平信号时低电平信号;

CPOL = 1:SCK 时钟线初始电平信号时高电平信号。

时钟相位(CPHA):SPI 总线进行数据采样(数据读取)是处于奇数沿还是偶数沿;

CPHA = 0:SPI 总线在 SCK 时钟线的奇数沿进行数据采样;

CPHA = 1:SPI 总线在 SCK 时钟线的偶数沿进行数据采样。

图 5 SPI 总线工作模式

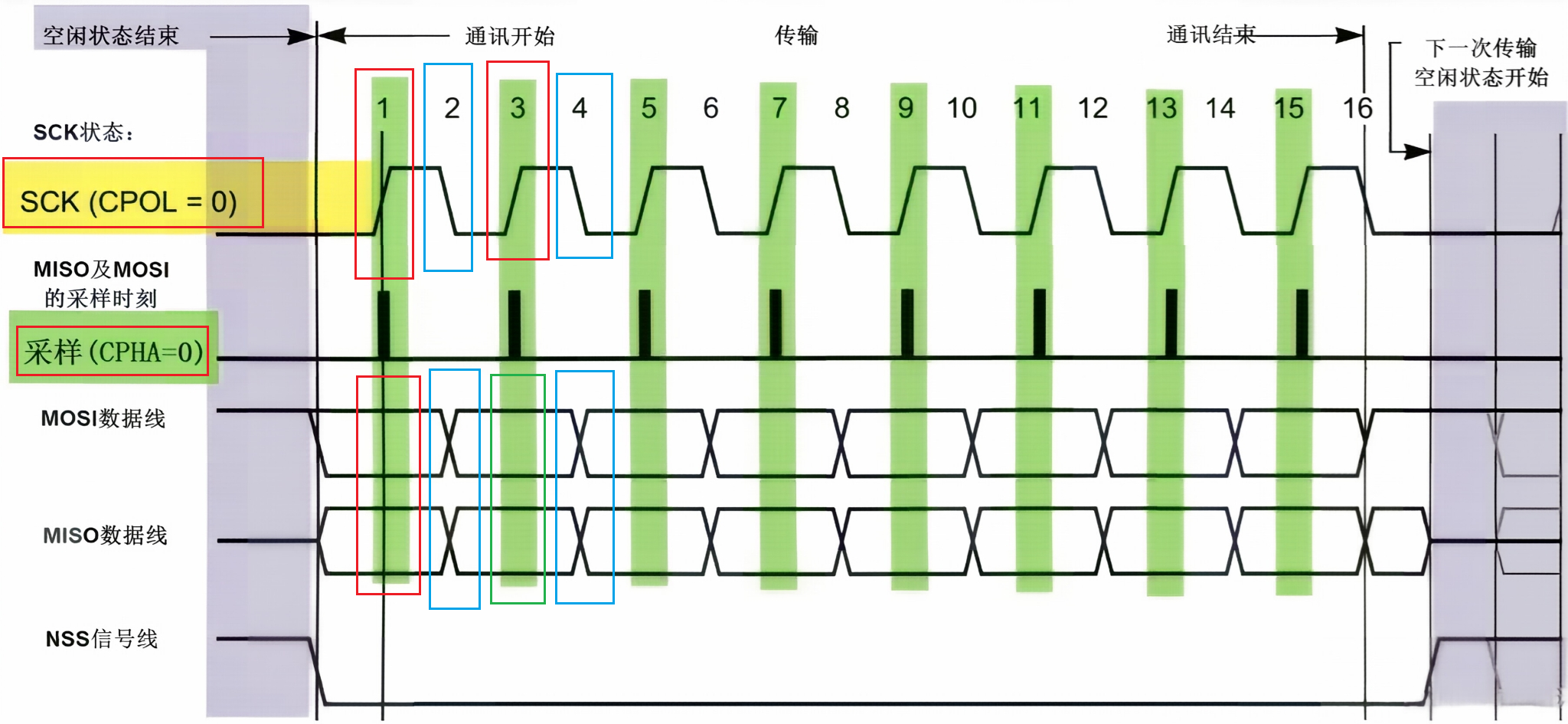

3.1 CPOL = 0,CPHA = 0 - 工作模式

图 6 CPOL = 0,CPHA = 0 CPOL = 0,CPHA = 0 时:

SCK 时钟线初始状态电平为 低电平 信号,SCK 时钟线处于 奇数沿 时,进行 数据采样

SCK 上升沿期间:主机 / 从机可以从 MOSI / MISO 数据线上 读取数据;

SCK 下降沿期间:主机 / 从机可以从 MOSI / MISO 数据线上 写入数据。

3.2 CPOL = 0,CPHA = 1 - 工作模式

图 7 CPOL = 0,CPHA = 1 CPOL = 0,CPHA = 1 时:

SCK 时钟线初始状态电平为 低电平 信号,SCK 时钟线处于 偶数沿 时,进行 数据采样

SCK 上升沿期间:主机 / 从机可以从 MOSI / MISO 数据线上 写入数据;

SCK 下降沿期间:主机 / 从机可以从 MOSI / MISO 数据线上 读取数据。

3.3 CPOL = 1,CPHA = 0 - 工作模式

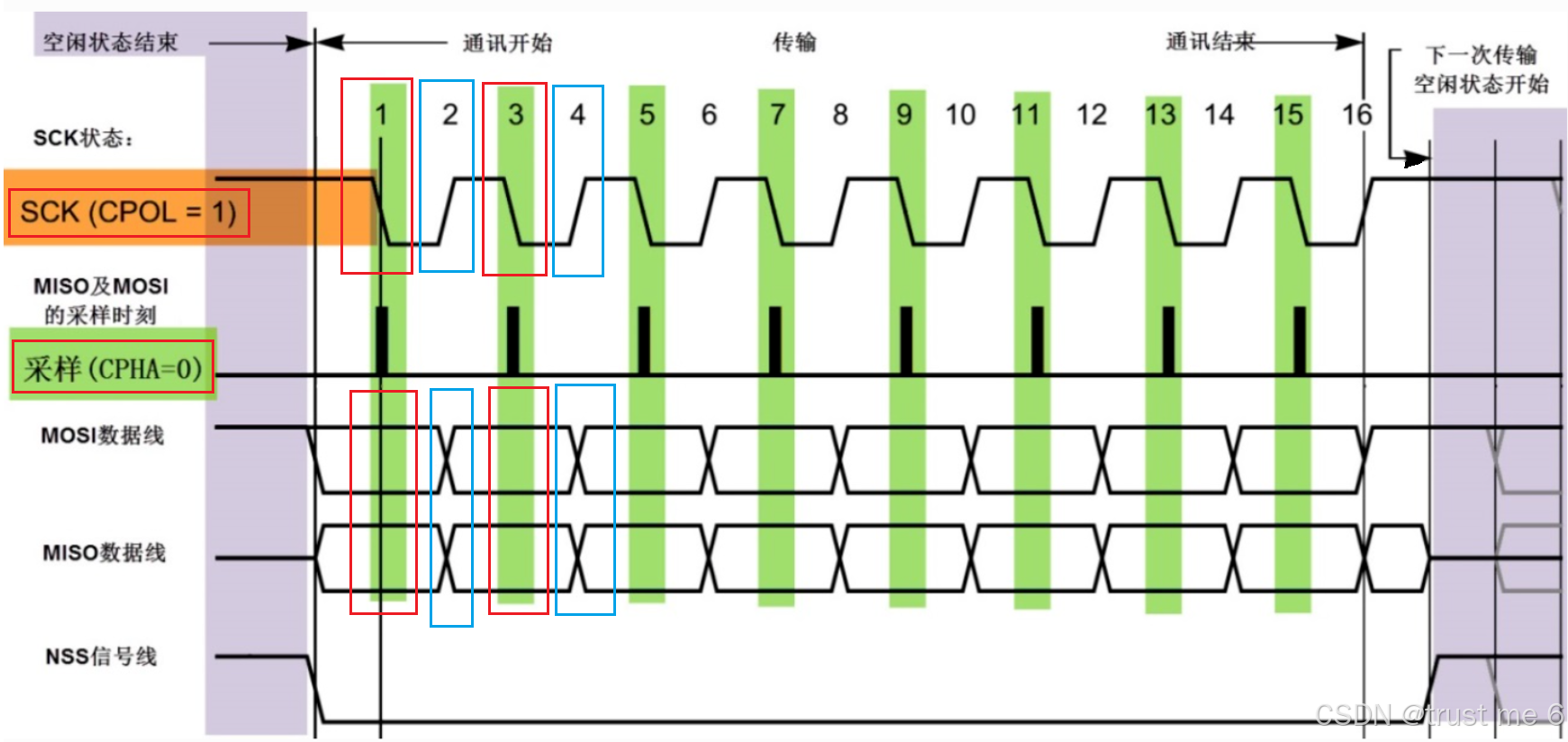

图 8 CPOL = 1,CPHA = 0 CPOL = 1,CPHA = 0 时:

SCK 时钟线初始状态电平为 高电平 信号,SCK 时钟线处于 奇数沿 时,进行 数据采样

SCK 上升沿期间:主机 / 从机可以从 MOSI / MISO 数据线上 写入数据;

SCK 下降沿期间:主机 / 从机可以从 MOSI / MISO 数据线上 读取数据。

3.4 CPOL = 1,CPHA = 1 - 工作模式

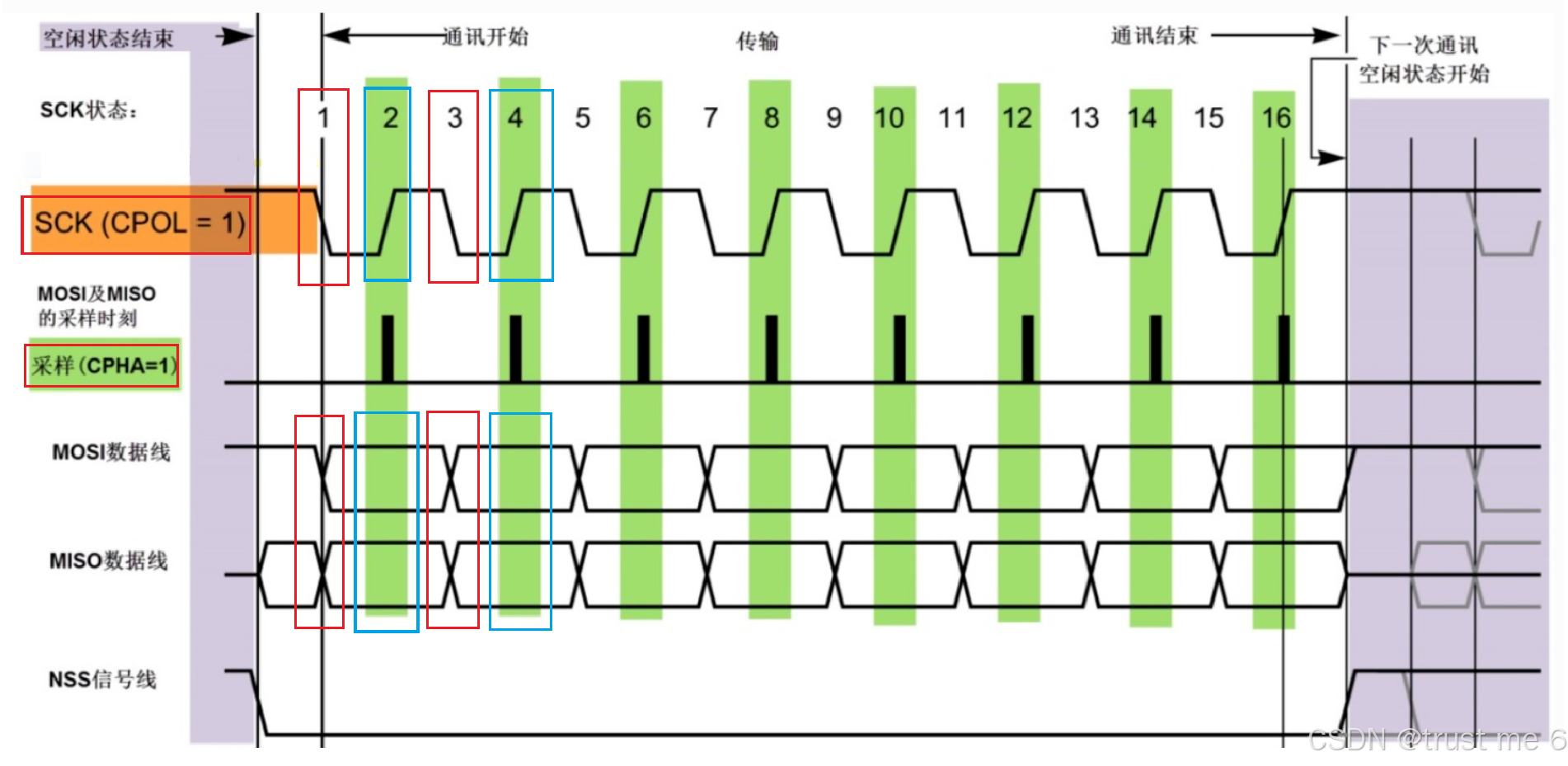

图 9 CPOL = 1,CPHA = 1 CPOL = 1,CPHA = 1 时:

SCK 时钟线初始状态电平为 高电平 信号,SCK 时钟线处于 偶数沿 时,进行 数据采样

SCK 上升沿期间:主机 / 从机可以从 MOSI / MISO 数据线上 读取数据;

SCK 下降沿期间:主机 / 从机可以从 MOSI / MISO 数据线上 写入数据。

3.5 SPI 总线通信要求

两个设备要使用 SPI 总线通信,必须:

- 两个设备的 SPI 总线的工作模式(协议格式)要相同;

- 工作模式相同就是:两个设备的时钟极性(CPOL)和时钟相位(CPHA)相同。

图 10 M74HC595 芯片的时钟极性和时钟相位